Fターム[5J055AX34]の内容

Fターム[5J055AX34]に分類される特許

1 - 20 / 290

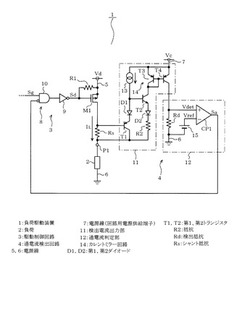

過電流検出回路および負荷駆動装置

【課題】回路用電源電圧としてむやみに高い電圧を用いることなく、シャント抵抗の低電位側端子の電圧がグランド電位付近となる異常が原因で生じる過電流を検出する。

【解決手段】検出電流出力部11は、シャント抵抗Rsの各端子電圧を入力し、その入力した電圧から負荷2に流れる電流に応じた検出電流を出力する。過電流判定部12は、検出電流に基づいて負荷2に過電流が流れているか否かを判定する。検出電流出力部11において、通常時に駆動用電源電圧Vdに近い電圧が印加される部分と、回路用電源電圧Vcに近い電圧が印加される部分との間の経路に第1ダイオードD1および第2ダイオードD2を逆方向に介在させることにより、第1トランジスタT1および第2トランジスタT2がブレークダウンして電流が流れることを阻止する。

(もっと読む)

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

半導体装置

【課題】スイッチング素子のターンオン直後における、過電流保護回路の誤動作防止と過電流検出遅れ防止とを両立させる。

【解決手段】半導体装置は、スイッチング素子1のセンス端子に流れるセンス電流を電圧(センス電圧)に変換するセンス抵抗4と、センス電圧が閾値を越えたときにスイッチング素子1の保護動作を行う過電流保護回路3とを備える。過電流保護回路3は、上記閾値を、第1基準電圧VREF1またはそれよりも低い第2基準電圧VREF2に切り替えることができる。過電流保護回路3は、スイッチング素子1が定常状態のときは、上記閾値を第2基準電圧VREF2とし、スイッチング素子1のターンオン直後のミラー期間のときは、上記閾値を第1基準電圧VREF1に設定する。

(もっと読む)

過電流検出装置

【課題】駆動に適した推奨値からずれた電気的特性を持つ負荷を駆動した場合でも誤検出を極力防止する。

【解決手段】しきい値生成回路11は、抵抗13、14にしきい値生成電流ITH、ITLを流してしきい値電圧VTH、VTLを生成し、コンパレータ12はシャント抵抗7の検出電圧Vaと比較して過電流検出信号Scを得る。しきい値補正回路17は、平均負荷電流、負荷電流の交流変化分、電源電圧VBが大きいほどしきい値電圧VTH、VTLを増やし、負荷4の温度が低いほどしきい値電圧VTH、VTLを増やす。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

負荷駆動装置

【課題】負荷電流検出手段により検出された負荷電流を用いてリーク故障を確実に検出する。

【解決手段】駆動回路33a、33bの出力端子Ta2、Tb2から電源線6に至る還流経路内にシャント抵抗9a、9bを接続し、電源線5と給電分岐点Nsとの間に共通のシャント抵抗24を接続する。駆動制御回路32は、MOSFET7a、7bをPWM駆動し、負荷電流検出回路12a、12bから負荷電流Ia、Ibを入力し、総電流検出回路23から総電流Isを入力する。検出負荷電流Ia、Ibに対しそれぞれ対応するPWM駆動信号のオフ駆動期間をマスク処理し、マスク処理した検出負荷電流Iam、Ibmを加算した加算電流Icmと検出総電流Isとを比較する。両者が等しい場合には正常状態と判定し、異なる場合にはショート故障またはリーク故障が生じたと判定する。

(もっと読む)

ハイサイドスイッチ回路

【課題】所定のスイッチング動作を実行しつつ、破壊耐性を向上することが可能なハイサイドスイッチ回路を提供する。

【解決手段】電源電圧をスイッチングして出力するハイサイドスイッチ回路100は、電源電圧Vccが印加される電源端子1に一端が接続された第1の出力MOSトランジスタM1、第1の出力MOSトランジスタの他端に一端が接続され電圧出力端子2に他端が接続された第2の出力MOSトランジスタM2、第1の出力MOSトランジスタに流れる電流の検出信号を出力する電流検出回路6、第1の出力MOSトランジスタが線形領域で動作するように第1の出力MOSトランジスタのゲートに第1の制御電圧を印加する第1のゲートドライバ4、第2の出力MOSトランジスタが線形領域で動作するように第2の出力MOSトランジスタのゲートに第2の制御電圧を印加する第2のゲートドライバ5を備える。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

半導体装置

【課題】駆動用のスイッチ素子によって出力端子からの出力を制御する半導体装置において、端子に静電気が印加されたときに、スイッチ素子をより確実に保護し得る構成を、装置構成の大型化を抑えて実現する。

【解決手段】半導体装置1は、高電位側電源又は低電位側電源の一方からなる基準部にスイッチ素子の第1端子が接続され、出力端子P1にスイッチ素子の第2端子が接続されている。また、スイッチ素子と並列に第1保護素子が設けられている。また、基準部とは逆側の電源(他方部)と出力端子の間には第2保護素子が接続されている。そして、基準部とは逆側の電源(他方部)側には無効化手段が接続され、出力端子へのサージ電圧の印加によって駆動電圧が発生した場合に、当該駆動電圧の発生後の所定時間、制御入力端子への通電信号の入力を無効化し、所定時間の経過後に無効化を解除するように機能している。

(もっと読む)

スイッチング素子の制御装置

【課題】実際に発生しているフライバックエネルギーを定量的に評価した上で保護動作を行うことができるスイッチング素子の制御装置を提供する。

【解決手段】NチャネルMOSFET2を介してコイル1に供給される電流をセンスMOSFET6及び検出用抵抗素子21により検出し、NチャネルMOSFET2をターンオフさせた際に発生し、ドレインに印加される逆起電圧をクランプ回路3によってクランプする。電流検出回路24は、クランプ回路3に発生するクランプ電圧によりNチャネルMOSFETがターンオンした際に、検出用抵抗素子21に流れる電流を複数の閾値と比較し、保護動作部26は、電流検出回路24の比較結果により、前記電流がNチャネルMOSFET2をターンオフさせた時点からの時間経過に対応する特定の閾値を超えていると判定されると、逆起電圧に基づくエネルギーを減少させるようにNチャネルMOSFET2の制御状態を変更する。

(もっと読む)

半導体スイッチング素子のゲート制御回路

【課題】スイッチング素子の発熱を抑制した過電圧抑制ゲート制御を確実、容易にし、さらにスイッチング素子を複数直列接続した半導体スイッチ回路における発振防止と分担電圧のバランス制御を確実、容易にする。

【解決手段】ゲートドライブ回路2によるゲート抵抗Aを通したIGBT1の主ゲート電流とは独立して、電圧補償ゲート制御回路3〜6はIGBT1のコレクタ・エミッタ間電圧Vceがしきい値を超えたときにゲート抵抗Bを通して電圧補償ゲート電流を注入し、電圧Vceがしきい値を下回ったときに電圧補償ゲート電流の注入をオフする。

ゲート抵抗Aの抵抗値に対してゲート抵抗Bの抵抗値を小さくする。電圧補償ゲート電流を注入した後にこのゲート電流の注入量とほぼ同じ電荷量分をIGBT1からゲート電流として引き抜く。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置の短絡保護装置

【課題】半導体素子、特にIGBTの特性の違いや温度変化があっても、最適なパラメータを自動的に設定することのできる半導体装置の短絡保護装置を提供する。

【解決手段】IGBTのゲート電荷QGに対応する電圧VQGを検出する電荷検出手段22と、IGBTの定格動作時の入力部の電荷から負荷短絡が発生したかどうかを判断するための基準電圧VREFを発生する基準電圧発生手段25と、電荷検出手段22で検出された電圧VQGがIGBTの定格動作時の電荷に対応する電圧か、あるいは負荷短絡時の電荷に対応する電圧かを判断する判断手段27と、判断手段27が短絡状態を検出したときにIGBTを動作停止する信号を出力するゲート駆動手段21とを持つ半導体装置の短絡保護装置において、基準電圧発生手段25に、IGBTの定格動作時の入力部の電荷に対応するゲート電荷電圧VQGのハイレベルで安定した電圧VPEAKを検出して記憶する記憶手段26を設ける。

(もっと読む)

過電流保護電源装置

【課題】直流電源17からスイッチ用のFET18を経て負荷16へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】比較基準電圧生成回路40を電流供給部41と比較基準電圧発生抵抗部46とで構成し、比較基準電圧VX を生成する。過電流検出電圧生成回路50を電流供給部51と過電流検出抵抗部54とで構成し、FET18の電圧VDSが増大すると減少する電流検出電圧VY を生成する。電圧VDSの増大を検出してFET18をオフすれば、過電流保護も過熱保護も可能となる。

(もっと読む)

半導体スイッチング素子駆動回路

【課題】 高コスト化、サイズ大型化を抑制し、短絡保護回路が制限する電流値がばらついても、過電流保護回路を確実に作動させる半導体スイッチング素子駆動回路を提供する。

【解決手段】半導体スイッチング素子駆動回路は、ゲート端子への電圧の印加により第1端子および第2端子間に主電流を流す半導体スイッチング素子Q1と、主電流の大きさに比例する電流値または電圧値が閾値を超えたとき、主電流が所定時間の間、所定の電流値を超える過電流となったと判断して主電流を低下させる過電流保護回路OPと、主電流が所定時間より短時間で過電流よりさらに大きい過電流となる場合に、ゲート端子に印加するゲート電圧を過電流保護回路による主電流の低下よりも早く低下させる短絡保護回路SPと、短絡保護回路の主電流の低下作動時に閾値を小さくする閾値変更回路TCと、を有する。

(もっと読む)

過電流保護電源装置

【課題】直流電源11からスイッチ用のFET12を経て負荷14へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】FETのドレイン・ソース間電圧に比例した電流Iを生成する電流変換回路4と、容量素子を含む一次遅れ回路として構成された過電流検出用電圧発生回路6とを直列接続し、その接続点Sの電圧を過電流検出用電圧VS とする。過電流検出回路5から制御回路3へ過電流検出信号が入力されて来たとき、制御回路3はFET12をオフする。過電流検出用電圧発生回路6の回路定数の設定を工夫することにより、VS を速やかに大になるようにすることが出来、1種類の保護回路で大過電流時にも保護が出来る。

(もっと読む)

負荷駆動装置

【課題】急激なアンダーシュート波形が生成されることにより発振状態になって不安定な動作を引き起こすことを防止する。

【解決手段】パワー素子4をオンさせる際に、パワー素子4の制御端子41に比較的大きな電流を供給することで制御端子41の電圧を比較的大きな勾配で上昇させつつ、制御端子41の電圧がクランプ電圧に至ってから電圧状態が安定化するまでは、制御端子41への比較的大きな電流の供給を保持する。そして、制御端子41の電圧状態が安定化した後に、制御端子41への電流供給が定電流回路31のみから為されるようにし、比較的小さな電流が制御端子41に供給されるようにする。

(もっと読む)

電子制御装置

【課題】電流検出用の抵抗を使用せず、簡易回路で負荷ショートの保護が可能な電子制御装置を得る。

【解決手段】パルス発生源3と第2のスイッチング素子21との間に接続されたコンデンサ23を有するトリガ回路と、負荷4と第1のスイッチング素子11との交点と第2のスイッチング素子21のベース端子との間にダイオード25を介して接続されるラッチ回路を有する制御回路を備え、パルス発生源が駆動信号を出力時は、トリガ回路を介し所定時間第2のスイッチング素子21をオンし、第1のスイッチング素子11もオンさせ、前記交点の電圧で、ラッチ回路を介し第2のスイッチング素子21のオン状態を継続させる。駆動信号の停止時は、第1、第2のスイッチング素子は共にオフとし、負荷ショートが発生した時は、パルス発生源3の駆動信号が出力されている場合でも、交点の電圧で、ラッチ回路を介して第2のスイッチング素子21をオフし、第1のスイッチング素子11もオフする。

(もっと読む)

並列接続された半導体スイッチ素子の駆動装置

【課題】 並列に接続された複数の半導体スイッチ素子に過電流が流れているか否かを精度良く検出可能な駆動装置等を提供する。

【解決手段】 駆動装置100は、第1の半導体スイッチ素子IGBT1と、第1の半導体スイッチ素子IGBT1の第2の端子Eでの電流を検出するための検出ノードSOと、第1の半導体素子スイッチIGBT1と並列に接続される少なくとも1つの半導体スイッチ素子IGBT2と、第1の半導体スイッチ素子IGBT1及び少なくとも1つの半導体スイッチ素子IGBT2を駆動する駆動回路DRと、第1の抵抗RG1と、少なくとも1組の抵抗RG2,RE2及び少なくとも1組のコモンモードフィルタLG2,LE2とを備える。RG1の抵抗値は、RG2の抵抗値とRE2の抵抗値とを加算した値に等しい。駆動回路DRの第2の駆動ノードEOは、何れの抵抗も介さず、第1の半導体スイッチ素子IGBT1の第2の端子Eと直接に接続される。

(もっと読む)

1 - 20 / 290

[ Back to top ]