Fターム[5J055DX63]の内容

Fターム[5J055DX63]の下位に属するFターム

エミッタ、ソース出力 (36)

コレクタ、ドレイン出力 (51)

2出力の差動型 (2)

ベース、ゲート出力

Fターム[5J055DX63]に分類される特許

1 - 20 / 94

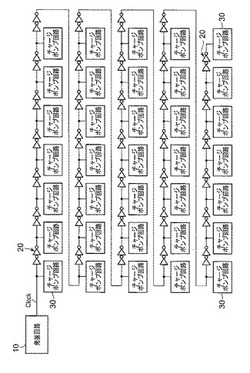

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

電流スイッチ回路およびDA変換器

【課題】差動出力電流のグリッチを打ち消しつつ、電源およびグランドに発生したノイズを打ち消す。

【解決手段】スイッチトランジスタM1、M2は、差動入力電圧Dip、Dimに基づいてスイッチング動作することで入力電流Iinを電流Ii1、Ii2に変換し、雑音電流発生回路1は、入力電流源2を介して流れる雑音電流を模擬したダミー電流Ibを生成し、スイッチトランジスタM3、M4は、差動入力電圧Dip、Dimに基づいてスイッチング動作することでダミー電流Ibを電流Ii3、Ii4に変換し、電流Ii1、Ii2に逆相的に重畳する。

(もっと読む)

ドライバ回路およびそれを用いた試験装置

【課題】ポジティブエッジの波形、ネガティブエッジの波形の少なくとも一方を調節可能なドライバ回路を提供する。

【解決手段】分岐回路10は、送信すべき入力信号SINを複数の経路12に分岐する。各タイミング調節回路20は、それぞれが対応する経路に分岐された送信すべき信号Saのポジティブエッジおよびネガティブエッジの少なくとも一方に遅延を与える。合成出力回路30は、複数のタイミング調節回路20の出力信号Sbを合成し、合成された信号SOUTを伝送線路3に出力する。

(もっと読む)

駆動回路

【課題】電源部品を減らし、安価な構成の駆動回路。

【解決手段】一次巻線Npと第1の二次巻線S1と第1の二次巻線の極性とは逆極性を持つ第2の二次巻線を有する2以上の二次巻線とを有し一次巻線に駆動信号が印加されるトランスDT1、第1の二次巻線からの信号によりオンオフ制御される第1スイッチング素子Qh、第2の二次巻線からの信号によりオンオフ制御される第2スイッチング素子Ql、第1の二次巻線の一端と第1スイッチング素子の制御端子との間に接続され第1スイッチング素子を駆動する第1駆動部Q11,Q12、第2の二次巻線の一端と第2スイッチング素子の制御端子との間に接続され第2スイッチング素子を駆動する第2駆動部Q21,Q22、第1の二次巻線電圧を倍電圧整流平滑して第1駆動部に供給する倍電圧整流平滑回路D11,D12,C11,C12、第2の二次巻線電圧を倍電圧整流平滑して第2駆動部に供給する倍電圧整流平滑回路D21,D22,C21,C22を有する。

(もっと読む)

カレントミラー回路、電流生成回路及び発光装置

【課題】負荷に供給する電流を精度よく出力する。

【解決手段】ゲート電極とドレイン電極が短絡されている第1トランジスタTr1と、第1トランジスタTr1のゲート電極に、ゲート電極が接続された第2トランジスタTr2と、を備えるカレントミラー回路10において、第1トランジスタTr1と第2トランジスタTr2は、絶縁膜12を介してゲート電極1の上部に設けられてチャネル領域が形成される半導体膜2と、半導体膜2上のチャネル領域を覆う領域に設けられる保護膜3と、半導体膜2のチャネル領域を挟む一対の端部に離間して設けられるとともに保護膜3の一部に重なって設けられソース電極6及びドレイン電極7とをそれぞれ有するとともに、少なくとも第2トランジスタTr2は、ソース電極6の保護膜3に対するチャネル長方向への重なり長がドレイン電極7の保護膜3に対する重なり長より長い構造を有する。

(もっと読む)

電源電圧監視回路

【課題】簡易な回路で正確な出力信号を出力する電源電圧モニター回路を提供すること。

【解決手段】クランプ回路15で電圧がクランプされる前は第1の定電圧Vref1と電源電圧Vccの電位差を比較することなく、LレベルのRST信号を出力するが、クランプ回路15で電圧がクランプされた後は第1の差動回路13で第1の定電圧Vref1と電源電圧Vccの電位差を比較し、Hレベル又はLレベルのRST信号を出力することが可能となる。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

プリエンファシス機能を含む出力回路と半導体装置

【課題】プリエンファシス機能を有する出力回路において、デエンファシス時における差動出力信号のコモンモード電圧のプリエンファシス時のコモンモード電圧からの変動を抑制する。

【解決手段】入力信号とその相補信号とを差動入力して差動出力し、差動出力信号のうち高電位側の出力信号にデエンファシスをかける際に、当該デエンファシス電流を供給するトランジスタ(N3、N4)に流れる電流を絞る回路(N5、N6、R3)を備え、デエンファシス時の前記出力信号のハイレベルの前記出力信号のプリエンファシス時のハイレベルからの変化量を縮減させ、デエンファシス時の前記差動出力信号のコモンモード電圧をプリエンファシス時のコモンモード電圧に近づける。

(もっと読む)

送信ドライバ回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できる送信ドライバ回路を提供する。

【解決手段】PチャネルMOSFET22のドレインをグランドに接続して、NチャネルMOSFET21,PチャネルMOSFET22のソースをそれぞれ信号線3H,3Lに接続する。第1データ電圧設定部41は、信号出力部がハイレベル信号を出力すると、ゲート21G,22G間の電位差を(2・R1・Iref)にする電圧信号を設定し、第2データ電圧設定部42は、信号出力部がロウレベル信号を出力すると、ゲート21G,22G間の電位差をゼロにする電圧信号を設定する。これらの作用により、伝送線路3を構成する信号線3H,3L間の電圧を変化させて差動信号を伝送する。

(もっと読む)

集積回路装置及び電子機器

【課題】通常動作モード、低消費電力動作モードでの省電力化等を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第1の電源電圧VDDAを出力する第1のレギュレーターRG1と、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第2の電源電圧VDDBを出力する第2のレギュレーターRG2と、第1の電源電圧VDDAが供給され、通常動作モード及び低消費電力動作モードにおいて動作する第1のロジック回路LG1と、第2の電源電圧VDDBが供給され、通常動作モードにおいて動作し、低消費電力動作モードでは非動作になる第2のロジック回路LG2を含む。

(もっと読む)

ドライバ回路

【課題】差動入力信号の振幅中心電圧が高い場合でも、差動出力信号の振幅変動やジッタを抑制することができるドライバ回路を提供することである。

【解決手段】本発明にかかるドライバ回路は、トランジスタM1と、トランジスタM1のソースと電源端子との間に接続された負荷素子R1と、トランジスタM1とカレントミラー回路を構成するトランジスタM2と、入力された差動入力信号に応じた差動出力信号を出力すると共に、トランジスタM2によりソースにバイアス電流が供給される一対のトランジスタを備える差動対と、トランジスタM2のソースと電源端子との間に接続された負荷素子R2と、非反転入力端子がトランジスタM1のソースと接続され、反転入力端子がトランジスタM2のソースと接続され、出力が差動対を構成する一対のトランジスタのバックゲートに接続されたオペアンプAMP1と、を有する。

(もっと読む)

駆動装置、及び表示装置

【課題】並列接続された複数の出力アンプ回路において所望の駆動能力を実現することができる駆動装置、及び表示装置を提供すること。

【解決手段】本発明に係る駆動装置(ソースドライバ1)は、並列接続された複数の出力アンプ回路10と、複数の出力アンプ回路10に、バイアス電圧供給源25からバイアス電圧を供給するバイアス配線(幹バイアス配線22)と、複数の出力アンプ回路10に、電源電圧供給源35から電源電圧を供給する電源配線31と、複数の出力アンプ回路10に供給される電源電圧とバイアス電圧との差が所望となるように、バイアス電圧にオフセット電圧を重畳する補正手段(バッファ26)とを備えた。

(もっと読む)

電流スイッチ回路及びこれを用いたディジタル−アナログ変換器

【課題】差動の電流スイッチ回路においてグリッチを効果的に低減とする。

【解決手段】相補的にレベルが変化する信号D,D_によりスイッチM1,M2において入力電流Iinをスイッチングして2つのスイッチ電流に分流し、分流されたスイッチ電流にスイッチングの遷移期間に生じるグリッチ成分をグリッチ同相化回路15により出力電流Iom,Iopにおいて同相にし、出力電流Iom,Iopを差動信号として観測したときにグリッチ成分をキャンセルする。

(もっと読む)

半導体集積回路

【課題】ゲート面積を増大させることなく、電界効果トランジスタ間のしきい値電圧のバラツキを自律的に補正させる。

【解決手段】補正回路12は、電子回路11に含まれる半導体素子間の電気的特性の差が所定の周期内の電気的特性の劣化量より大きい場合、その電気的特性の劣化量の小さい方の半導体素子の劣化を進行させ、電子回路11に含まれる半導体素子間の電気的特性の差が所定の周期内の電気的特性の劣化量より小さい場合、その電気的特性に差のある半導体素子の劣化を所定の周期ごとに交互に進行させる。

(もっと読む)

電流スイッチ回路及びそれを用いたD/Aコンバータ、半導体集積回路及び通信機器

【課題】電流加算型D/Aコンバータに用いられる電流スイッチ回路において、低電源電圧時にしきい値電圧の低いトランジスタを用いた際に課題となるダイナミックレンジの低下を改善し、出力電圧範囲を大きく取る。

【解決手段】電流スイッチ回路1は、差動スイッチ12を構成する第1及び第2のトランジスタTr121、Tr122を有する。しきい値電圧制御回路5は、その出力端子Vboutから前記差動スイッチ12を構成する2個のトランジスタTr121、Tr122のサブストレート端子に出力するサブストレート電圧を制御して、前記差動スイッチの2個のトランジスタのしきい値電圧を制御する。従って、電流スイッチ回路1の電源電圧を低減させても、特性劣化を生じることなく、差動スイッチ12内の2個のトランジスタのしきい値に依存する電流スイッチ回路1の出力電圧範囲を大きく取ることができる。

(もっと読む)

半導体集積回路

【課題】専用回路部が誤動作を起こすことを防止する半導体集積回路を提供することを目的とする。

【解決手段】電源部11と、制御回路部12と、専用回路部13を有する半導体集積回路であって、前記電源部に設けられ第1電源を生成して前記専用回路部に供給する第1電源回路11aと、前記電源部に設けられ前記第1電源より電圧の低い第2電源を生成して前記制御回路部に供給する第2電源回路11bと、前記電源部に設けられ前記第2電源が立ち上がったのちリセット解除を指示するリセット信号を生成して前記専用回路部に供給するリセット回路11cとを有し、前記制御回路部が動作を開始したのち前記専用回路部のリセットを解除する。

(もっと読む)

CV変換回路

【課題】コストおよび消費電力の増大をともなう高速の演算増幅器に依存することなく、IC化に適した回路でもって、高い周波数領域での静電容量挙動を高感度かつ高確度に検出できるようにし、これにより、高周波領域での誘電率挙動による物性の検査や分析を的確に行うことを可能にする。

【解決手段】2つのセンサ容量素子Cx1,Cx2を高周波クロック信号+Φ1に同期して相補的に充放電させる通電回路50と、その2つのセンサ容量素子の通電電流差分ΔIxと上記高周波クロック信号+Φ1とのアナログ乗算操作によって、上記通電電流差分に応じた直流成分を有する電圧Vo1を出力する同期検波回路10と、この同期検波回路10の検波出力電圧を平滑処理しながら増幅する演算増幅器30とを備え、この演算増幅器30の出力から上記2つのセンサ容量素子の静電容量差分ΔCxに対応する直流出力電圧を得る。

(もっと読む)

1 - 20 / 94

[ Back to top ]