Fターム[5J055DX65]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | スイッチの形態 (2,011) | 差動型、エミッタ・ソース結合型 (183) | コレクタ、ドレイン出力 (51)

Fターム[5J055DX65]の下位に属するFターム

一石を介して帰還しているもの

Fターム[5J055DX65]に分類される特許

1 - 20 / 51

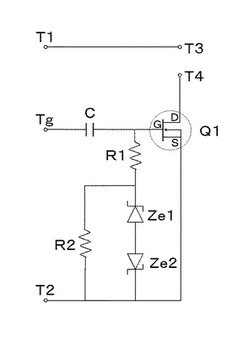

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

リセット回路

【課題】マイコンのリセット端子をトランジスタによってグランドに接続することによりマイコンにリセットをかけるリセット回路において、リセット動作不能な電源電圧の領域を無くす。

【解決手段】リセット回路10は、マイコン11のリセット端子13を電源電圧(以下、VM)にプルアップする抵抗R1と、VMが所定値未満のときにトランジスタT1をオンしてリセット端子13を0Vにするリセット信号出力回路15とに加え、オンすることで抵抗R1の上流側にVMを供給するトランジスタT2と、抵抗R1の上流側とグランドとの間に接続された抵抗R2と、トランジスタT1がオン可能なVMの最低値(Vbe)より高く、上記所定値よりは低い電圧(Vbe+ダイオードD1のVf)を動作閾値電圧とし、VMがその動作閾値電圧未満である場合にトランジスタT2をオフさせておいて、マイコン11のリセットを確保する回路T3,D1,R3,R4とを備える。

(もっと読む)

リセット回路

【課題】複数の電源電圧を駆動電圧とするSoC IC(System on a Chip Integrated Circuit)に対し、負荷変動やノイズに影響されること無く、複数の電源電圧の供給とリセット解除タイミングとのシーケンスを守ってリセットを行う。

【解決手段】供給ラインL1とリセット端子16との間においてエミッタを供給ラインL1に向けつつコレクタをリセット端子16に向けて介挿されたトランジスタTr1と、トランジスタTr1のベースとグランドとの間においてコレクタをトランジスタTr1のベースに向けつつエミッタをグランドに向けて介挿されたトランジスタTr2と、トランジスタTr1のコレクタとグランドとの間においてコレクタをトランジスタTr2のコレクタに向けつつエミッタをグランドに向けて介挿されたトランジスタTr3とを備える。

(もっと読む)

マルチステートドライブ回路による半導体スイッチのスイッチング方法および回路

【課題】半導体スイッチがオフ状態からオン状態へ、或いはオン状態からオフ状態へ切換えられるときに半導体スイッチの損失を低減する新規な半導体スイッチの多段ドライブ回路を実施するための方法及び装置を提供する。

【解決手段】損失の低減は、半導体スイッチが切換える第1の時間期間中に半導体スイッチ両端のdv/dtに影響を与えることなく達成される。この損失の低減は、従って半導体スイッチが切換えるときの第1の時間期間中の急速なdv/dtによって発生する雑音をごくわずかしか増大させずに達成される。スイッチングロスのこの低減を達成するための回路の構成は、同様の結果を達成するための他の半導体スイッチドライブ方式よりも製造中の許容誤差及び温度の影響を受けにくい利点を有する。

(もっと読む)

レギュレータ用半導体集積回路

【課題】 外部から回路をオン、オフ制御するための制御端子を有するレギュレータ用ICにおいて、制御信号による起動直後に出力端子に向かってラッシュ電流が流れるのを防止できるようにする。

【解決手段】 制御回路のオン、オフを指示する制御信号が入力される外部制御端子(CE)とを備えたレギュレータ用ICにおいて、電圧入力端子または出力端子と接地電位端子との間に直列に接続された電流源(Tr0,R3)と基準電圧回路(Tr2,Tr3)を設け、該電流源と基準電圧回路との接続ノードは外付けのコンデンサが接続される外部端子(CS)に接続し、基準電圧回路はデプレッション型MOSトランジスタとエンハンスメント型MOSトランジスタが直列に接続され、それらのトランジスタのしきい値電圧の差に相当する電圧を出力するように構成した。

(もっと読む)

情報処理装置

【課題】 電源遮断機能を有するLSIにおいて、電源遮断をオンオフするときにリーク電流による電流が急激に変化すると電源線にノイズを生ずる。

【解決手段】 情報処理装置であって、回路ブロックと、前記回路ブロックに電源を供給するためのローカル電源線と、電源線と、前記電源線と前記ローカル電源線の間にそのソース―ドレイン経路が設けられる第1のトランジスタとを有し、前記第1のトランジスタは、第1の状態においてはオフ状態に制御され、第2の状態においてはオン状態に制御され、前記第1の状態から前記第2の状態に移行する際に、前記第1のトランジスタは、前記第1のトランジスタのソース―ドレイン経路を流れる電流の変化率が、所定の値を超えないように制御されることを特徴とする。

(もっと読む)

電子回路

【課題】 充電回路の動作を安定化させる。

【解決手段】 充電回路(100)は、第1出力信号を出力するTr制御回路(24)と、第1出力信号が入力されて動作するトランジスタ(Tr)及びコンデンサ(C1)と、その状態を検出し、その結果としての第2出力信号を出力するコンパレータ(21)と、第2出力信号に基づいて、Tr制御回路をして前記第1出力信号を出力させるかどうかを決定する第3出力信号をTr制御回路に供給するフリップフロップ(24)と、を備え、フリップフロップの入出力特性の遷移帯は、Tr制御回路の入出力特性の遷移帯と重ならない。

(もっと読む)

液晶表示装置、及び液晶表示装置を具備した電子機器

【課題】駆動回路におけるトランジスタの特性劣化を抑制することを課題の一つとする。

【解決手段】第1のトランジスタと、ゲート並びにソース及びドレインの一方に第2の信号が入力される第2のトランジスタと、ゲートが第1のトランジスタのソース及びドレインの他方に電気的に接続され、オン又はオフになることにより出力信号の電圧状態を設定するか否かを制御する第3のトランジスタと、ゲートが第2のトランジスタのソース及びドレインの他方に電気的に接続され、オン又はオフになることにより出力信号の電圧状態を設定するか否かを制御する第4のトランジスタと、を有する。

(もっと読む)

高周波スイッチ及び受信回路

【課題】簡単な構成でセルフミキシング信号の発生を低減する高周波スイッチ及びこれを用いた受信回路を提供する。

【解決手段】ゲート端子が入力端子側に接続され、ドレイン端子が出力端子側に接続され、ソースが接地された電界効果トランジスタと、前記電界効果トランジスタのゲート端子側に接続されるゲートバイアス電圧調整手段とドレイン端子側に接続されるドレインバイアス電圧調整手段の少なくともいずれか一方を備え、前記ゲート端子と入力端子との間及び前記ドレイン端子と出力端子との間の少なくともいずれか一方に整合回路を備え、導通状態における反射特性と前記遮断状態における反射特性とが略等しくなるように、スイッチを構成している。

(もっと読む)

発光素子のドライバ回路

【課題】発光素子のドライバ回路における消費電力を抑制する。

【解決手段】発光素子202と、発光素子202と直接に接続された電流制限用インダクタ24との直列接続部と、直列接続部に並列に接続され、電流制限用インダクタ24に蓄えられたエネルギーを回生する回生用ダイオード28と、発光素子202及び電流制限用インダクタ24に流れる電流を制御するトランジスタ26と、トランジスタ26の動作を制御する制御部22と、電流制限用インダクタ24と電磁気的に結合し、制御部22に電源電力の少なくとも一部を供給する電源用インダクタ30と、を備える。

(もっと読む)

直流過電流遮断装置

【課題】直流給電において、負荷に過電流が流れた場合、負荷電流路を瞬時に自動的に遮断する。さらに、負荷短絡が発生した場合でも、瞬時に自動的に負荷電流路を遮断する。

【解決手段】第1コイルの一端に外部の直流電源の一方の極の電位が印加され、第1半導体素子の他端に外部の直流電源の他方の極の電位が印加されているとき、第1コイルの他端と第2コイルの他端間に所定の電流値を超えた電流が流れると、第1半導体素子の一端の電位により、第2制御端を制御し、さらに第2半導体素子の一端の電位により、第1制御端を制御し、第1半導体素子が有する電流路を遮断する。

(もっと読む)

出力回路、出力方法、出力回路の製造方法、および電子機器

【課題】 ノイズを発生させ難い出力回路等を提供する。

【解決手段】 出力回路(10)は、入力ノード(IN)と、出力ノード(OUT)と、入力ノードと出力ノードとの間に配置され、第1のゲート(13)を有する第1の出力トランジスタ(12)と、入力ノードと出力ノードとの間に配置され、第2のゲート(16)を有する第2の出力トランジスタ(15)と、入力ノードと出力ノードとの間に配置され、第3のゲート(19)を有する第3の出力トランジスタ(18)と、を備える。第1のゲート(13)および第2のゲート(16)は、第1の方向(DR1)に、第3のゲート(19)を介さず、互いに接続される。第2のゲート(16)および第3のゲート(19)は、第1の方向とは異なる第2の方向(DR2)に、第1のゲート(13)を介さず、互いに接続される。第1のゲート(13)および第3のゲート(19)は、第2のゲート(16)を介して接続される。

(もっと読む)

スイッチング回路

【課題】 IC化を容易にでき、特性を安定化させることができるスイッチング回路を提供すること。

【解決手段】 制御信号生成する構成は、スイッチング素子M1の制御信号のターンオン時の作動閾値電圧近傍までの昇圧を、電源V2からの注入で早めるパルス発振器P2、トランジスタQ1、電源V2と、スイッチング素子M1の制御信号のターンオフ時の作動閾値電圧近傍までの降圧を、電流経路101と別の電流経路102,103で電流を流すことで早めるダイオードD2、トランジスタQ2、電源V3を備えた。

(もっと読む)

負荷制御装置

【課題】負荷を駆動する場合に、電源電圧が変動してしまったときでも、制御の対象の負荷の変動を抑えることができる技術が求められている。

【解決手段】負荷制御装置10は、定電圧源が省かれており、デューティ比調整手段として第12の抵抗R12とツェナーダイオードZD1を有している。従来、定電圧源の出力に接続していた第1のトランジスタQ1、第2のトランジスタQ2、第3のトランジスタQ3、第3の抵抗R3、第6の抵抗R6、第9の抵抗R9、第11の抵抗R11の端子が、バッテリBTの正極端子に接続される。また、第12の抵抗R12の一方の端子がバッテリBTの正極端子に接続され、他方の端子がツェナーダイオードZD1のカソードに接続され、ツェナーダイオードZD1のアノードは、第2の比較器CP2の非反転入力端子に接続される。

(もっと読む)

スイッチ回路

【課題】スイッチ回路のポート数が増加しても挿入損失を増加させず、且つ歪みによる高調波の影響を低減することのできるスイッチ回路を提供する。

【解決手段】1個の共通出力ポートと、一端が第1ノードで共通接続されたM(Mは2以上の整数)個の第1スイッチと、一端が共通出力ポートに共通接続されたN(N≧1の整数)個の第2スイッチと、一端が共通出力ポートに接続され、他端が第1ノードに接続された第3スイッチと、第1スイッチの他端にそれぞれ接続されたM個の第1入出力ポートと、第2スイッチの他端にそれぞれ接続されたN個の第2入出力ポートとを備え、第1入出力ポート及び第2入出力ポート中の選択されたいずれか1つのポートのみを共通出力ポートに接続させるように駆動され、第1入出力ポートのいずれかが選択された時には、第3スイッチを閉塞することを特徴とするスイッチ回路とした。

(もっと読む)

半導体素子駆動回路

【課題】電圧クランプ機能を備える場合に、電源電圧が低下した場合のバイアスを十分に行うことができると共に、消費電力の増加も抑制できる半導体素子駆動回路を提供する。

【解決手段】クランプ用FET駆動部18は、FET4をオン状態に制御するため外部より制御信号が与えられ、出力段のFET2をオンさせる場合はFET4のゲート電位をクランプするが、コンパレータ14により電源電圧が閾値未満であると判断されると、上記電圧クランプ機能を無効化する。具体的には、FET9を遮断状態にすると共にスイッチ回路6を導通状態にして、クランプ機能を無効化すると同時に定電流源7によりFET5を駆動する。

(もっと読む)

負荷駆動回路、半導体集積回路およびICテスタ

【課題】大電流の出力およびこの電流レンジでの測定を安定した動作で実現することのできる負荷駆動回路、電流測定レンジを小電流から大電流まで幅広い範囲で実現することのできる負荷駆動回路を提供する。

【解決手段】負荷(Rdut,Cdut)に対して制御信号に応じた電圧で電流供給を行うとともにこの供給電流の測定が可能な負荷駆動回路である。制御信号に応じた電圧で電流出力を行う反転アンプ(OP1,R1,R2)と、反転アンプの出力電流を検出するための検出抵抗R3と、検出抵抗R3の両端電圧に比例した電流を出力する電圧制御型電流源(減算回路2、レベルシフト回路3,4、ソース側電流源5、シンク側電流源6)とを備え、反転アンプの出力電流ISC_R1,ISK_R1と電圧制御型電流源の出力電流ISC_Q5,ISK_Q6とが合算されて負荷に出力される構成とした。

(もっと読む)

分配器

【課題】出力ポートに接続された後段回路のインピーダンスが変動した場合でも、定在波比、及び、通過特性の周波数特性の悪化を低減することができる分配器を提供する。

【解決手段】 1つの入力ポートPinと、後段回路21、22が接続される2つの出力ポートPout1、Pout2とを有し、前記入力ポートPinから入力された信号を前記2つの出力ポートPout1、Pout2に分配して出力する分配器1であって、前記入力ポートPinから分岐した2つの出力端であるノードN1、N2を有し、入力ポートPinからみたインピーダンスを、前記後段回路21、22の第1インピーダンスに整合する分配回路10を備え、前記2つのノードN1、N2のそれぞれに、互いに等しい電気長Lc及び所定の特性インピーダンスZcを有する移相器13、14を設け、前記移相器13、14の出力端のそれぞれを前記出力ポートPout1、Pout2に接続する構成とした。

(もっと読む)

1 - 20 / 51

[ Back to top ]