Fターム[5J055DX12]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442)

Fターム[5J055DX12]の下位に属するFターム

N型 (195)

P型 (99)

閾値 (83)

構造 (11)

MOSFET、MISFET (1,263)

MESFET (9)

接合型FET (6)

GaAsFET (12)

デュアルゲートFET (10)

Fターム[5J055DX12]に分類される特許

1 - 20 / 754

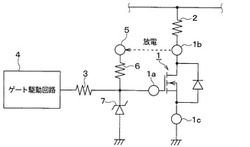

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

半導体スイッチ

【課題】半導体スイッチにおいて、エネルギー効率を高くする。

【解決手段】半導体スイッチ1は、LED2を駆動回路3により駆動して発光させ、LED2から発光された光を受光部4により受光する。駆動回路3は、バイポーラトランジスタ31と、コイル32と、ダイオード33等を有する。バイポーラトランジスタ31は、導通状態と非導通状態とに切換えられ、導通状態のときに、電源からLED2に電流が供給される状態にし、非導通状態のときに、電源からLED2に電流が供給されない状態にする。コイル32は、LED2に直列に接続されており、バイポーラトランジスタ31が導通状態から非導通状態になったときに、自己誘導作用によって誘導起電力を発生する。ダイオード33は、LED2及びコイル32に並列に接続されており、バイポーラトランジスタ31が非導通状態のときに、コイル32が発生する誘導起電力によって、LED2に電流を還流させる。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路のレギュレータ回路では、出力電圧の制御精度を十分に高めることができない問題があった。

【解決手段】本発明の半導体集積回路は、制御端子に与えられるインピーダンス制御信号で示される制御値PLに応じて負荷電流Iloadの大きさに対する出力電圧VDDMの大きさを制御する複数の出力トランジスタPMと、出力電圧VDDMの電圧値を示す出力電圧モニタ値VMを出力する電圧モニタ回路12と、出力電圧VDDMの目標値を示す参照電圧Vrefと、出力電圧モニタ値VMと、の間の誤差値の大きさに応じて制御値PLの大きさを制御し、当該制御値PLにより複数の出力トランジスタPMいずれを導通状態とするかを制御する制御回路10と、を有し、制御回路10が負荷電流Iloadの変更を事前に通知する事前通知信号PACCに応じて、誤差値に対する制御値の変化ステップを一定期間の間大きくする。

(もっと読む)

スイッチング回路及び電源装置

【課題】 半導体スイッチが故障することを抑制することのできるスイッチング回路を提供する。

【解決手段】

電源装置1は、電流路内に配置されオン・オフ動作可能なメインFET131と、メインFET131にオン・オフ動作を行わせる制御部19と、メインFET131の温度を検出する第1サーミスタ134と、電流路内においてメインFET131と並列に配置されオン・オフ動作可能なサブFET132と、を備え、制御部19は、メインFET131の温度が所定温度を超えた場合に、オン・オフ動作を行わせるFETをメインFET131からサブFET132に切り替える。

(もっと読む)

高周波スイッチ

【課題】通過損失を低減するためにオン状態時の抵抗を小さくしても、十分なアイソレーション量を確保する高周波スイッチを得る。

【解決手段】トランジスタ5a,5bのオフ容量Coffと同一の容量Ccを有するクロスカップルキャパシタ8a,8bを設ける。

クロスカップルキャパシタ8a,8bにより、トランジスタ5a,5bのオフ容量Coffをキャンセルすることができるので、アイソレーションを大きく改善することができる。したがって、通過損失を低減するためにトランジスタ5a,5bのオン抵抗Ronを小さくしても、十分なアイソレーション量を確保することができる。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

駆動回路

【課題】駆動電圧を調整可能な駆動回路を提供すること。

【解決手段】駆動回路10は、チャージポンプ回路部14を備えている。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、キャパシタC1に充電された充電電圧に基づいて駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成する。チャージポンプ回路部14では、指示信号S1に基づいてキャパシタC1に充電される充電電圧が調整可能に構成されている。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

スイッチング電源装置

【課題】大型化することなく、アーム短絡および損失増大の問題を解消したスイッチング電源装置を構成する。

【解決手段】ローサイドスイッチング制御部81は、ローサイドスイッチング素子(Q1)へ駆動電圧信号を出力している期間にトランスの巻線電圧の極性反転を検出したときに、遅延時間(td1)の後にローサイドスイッチング素子(Q1)をターンオフさせるローサイドターンオフ回路を備え、ハイサイドスイッチング制御部61は、トランスの巻線電圧の極性が反転してからハイサイドスイッチング素子(Q2)をターンオンさせるまでの時間(td2)を遅延させる。そして、ローサイドターンオフ遅延回路の遅延時間(td1)はハイサイドターンオン遅延回路の遅延時間(td2)よりも短く設定されている。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

スイッチ回路

【課題】多くの個別素子による回路を用いることなく、容易に簡素な回路構成で端子外れ検出を行うことが可能なスイッチ回路の提供。

【解決手段】ゲートがセンサ回路に接続され、ドレインが第1の電圧制限抵抗に接続された第1の出力ドライバと、物理量検出信号出力端子と接地端子の間に接続された第2の電圧制限抵抗と、非反転入力端子が第1の基準電圧回路に接続され、反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第1の比較器と、反転入力端子が第2の基準電圧回路に接続され、非反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第2の比較器と、ゲートが前記論理回路の出力に接続され、ドレインが断線診断信号出力端子に接続された第2の出力ドライバで構成した。

(もっと読む)

ゲート駆動回路、電力変換回路、3相インバータ、及びゲート駆動方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】ハイサイドトランジスタ21とローサイドトランジスタ22の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路11、12の少なくとも一方は、正電源から供給される第1電源電圧VDDと、負電圧源30から供給され接地電圧GNDよりも低い第2電源電圧VNEGとに応じた駆動電圧GH、GLを、ノーマリオン型のトランジスタのゲートに出力する。制御回路40は、第2電源電圧VNEGが参照電圧Vrefよりも高い場合、ハイサイドトランジスタ21に流れるドレイン電流を遮断する。

(もっと読む)

ソレノイドの通電制御装置

【課題】ソレノイドに流れる電流を検出するタイミングと、PWM信号を出力するタイミングとのずれを抑制可能なソレノイドの通電制御装置を提供する。

【解決手段】ソレノイドの通電制御装置100は、ソレノイド50に流れる電流の電流値の取得用の電流取得用タイマ10と、当該電流取得用タイマ10の計数結果に基づいて、ソレノイド50の通電を制御するスイッチング素子51を駆動するPWM信号の1周期内において予め設定された回数だけ電流値を取得する電流値取得部11と、PWM信号の出力用のPWM制御用タイマ20と、1周期内に取得された電流値に基づき、次の1周期にスイッチング素子51に通電する通電時間を設定し、当該設定した通電時間に応じたPWM信号を出力するPWM制御部21と、PWM制御用タイマ20の計時結果に基づき、電流取得用タイマ10の計時値を更新する計時値更新部41と、を備える。

(もっと読む)

不揮発性プログラマブルロジックスイッチ

【課題】メモリの選択的な書き込みを行う際のパストランジスタのゲート絶縁膜の破壊を防ぐとともにパストランジスタのゲート絶縁膜を薄くすることを可能にし、かつメモリの微細化によって書き込み効率が損なわれない不揮発性プログラマブルロジックスイッチを提供する。

【解決手段】第1端子と、第2端子と、メモリ状態を制御する制御信号を受ける第3端子とを有する第1メモリと、ソース/ドレインの一方が第2端子に接続される第1トランジスタと、第1トランジスタのソース/ドレインの他方にゲートが接続される第2トランジスタとを備えた、第1セルおよび第2セルを有する。第1セルの第1メモリの第3端子と、第2セルの第1メモリの第3端子は共通に接続され、第1セルに書き込みを行う場合、第3端子が書き込み電源に接続され、第1セルの第1端子は接地電源に接続され、第2メモリの第1端子は書き込み防止電源に接続される。

(もっと読む)

過電流保護回路

【課題】過電流検出抵抗の温度特性の影響をキャンセルすることのできる過電流保護回路を提供する。

【解決手段】基準抵抗と第1定電流源との第1接続点には、該第1接続点の電位の温度特性が、過電流検出抵抗の電圧検出端子の電位の温度特性と等しくなるように、第1接続点に対して正の温度特性を有する第2定電流を供給する第2定電流源が接続されている。第2定電流源は、負の温度特性を有する第3定電流を供給する第3定電流源と、温度特性を有さない第4定電流を供給する第4定電流源と、第3定電流源に対して直列接続された第1トランジスタと、第4定電流源に対して直列接続された第2トランジスタと、により構成された第1カレントミラー回路と、第4定電流源と第2トランジスタとの接続点に接続され、第1接続点に第2定電流を供給するための電流経路と、を有する。第3定電流源は、過電流検出抵抗と同じ基板に形成されている。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

半導体集積回路

【課題】外部から印加された電圧のノイズを減少させて電圧を安定化させる半導体集積回路を提供する。

【解決手段】本発明は、電圧ノイズを減少させて電圧を安定化させる半導体集積回路において、第1電流が流れる第1内部回路と、第2電流が流れる第2内部回路と、前記第1電流のうちの一部と前記第2電流のうちの一部は第1接地パッドに流れ、残りの前記第1電流と残りの前記第2電流は第2接地パッドに流れるように構成された電圧安定化部とを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】ハイサイド駆動回路が負バイアス駆動を行いつつ、ブートストラップコンデンサによりハイサイド駆動回路に駆動電圧を供給することができる半導体装置を得る。

【解決手段】基準電圧回路3は、ハイサイド駆動回路1の高圧端子VBの電圧と低圧端子VEの電圧との間の基準電圧を生成して、ハイサイドスイッチング素子Q1とローサイドスイッチング素子Q2の接続点に供給する。充電用スイッチング素子Q3のドレインがハイサイド駆動回路1の低圧端子VEに接続され、ソースが接地されている。

(もっと読む)

半導体スイッチ回路

【課題】簡易な構成によりスイッチ切替時間のさらなる高速化を図る。

【解決手段】外部から供給される外部制御信号に応じて、高周波スイッチ回路101のFET1,2のオン、オフ状態を制御する駆動制御信号を出力する論理制御回路104と、FET1,2が論理制御回路104によりオフ状態からオン状態とされる際にパルス電圧を出力する切替加速回路102,103とは、それぞれの出力信号が共にFET1,2の駆動制御信号として、それぞれへ印加可能に設けられ、論理制御回路104は、定常状態においてFET1,2をオン状態とする電源電圧とほぼ等しい駆動制御信号を出力するよう構成され、切替加速回路102,103は、ピークが電源電圧を超えるパルス電圧を出力する一方、そのパルス電圧が論理制御回路104の出力信号の電圧レベルを下回った際には、その出力が遮断されるよう構成されたものとなっている。

(もっと読む)

半導体装置

【課題】発光装置に含まれる発光素子の発光輝度を周囲の情報に応じて調節する表示シス

テムを提供する。

【解決手段】本発明において、センサー2011が周囲の情報を電気信号として検出し、

これをCPU2013は、あらかじめ設定しておいた比較データに基づきEL素子の発光

輝度を補正するための補正信号に変換する。この補正信号が電圧可変器2010に入力さ

れることにより、電圧可変器2010が所定の補正電位をEL素子に印加する。以上の表

示システムによりEL素子2003の発光輝度を制御することができる。

(もっと読む)

1 - 20 / 754

[ Back to top ]