Fターム[5J055DX12]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442)

Fターム[5J055DX12]の下位に属するFターム

N型 (195)

P型 (99)

閾値 (83)

構造 (11)

MOSFET、MISFET (1,263)

MESFET (9)

接合型FET (6)

GaAsFET (12)

デュアルゲートFET (10)

Fターム[5J055DX12]に分類される特許

41 - 60 / 754

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

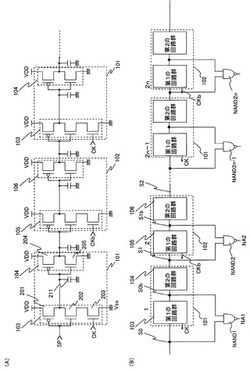

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮し、オーバドライブによらず速度の向上と電力効率の向上を図り得るスイッチング回路を提供する。

【解決手段】半導体スイッチ素子20a、20dがON(OFF)のとき残りの半導体スイッチ素子がOFF(ON)となるように、各半導体スイッチ素子の入力端子にパルス状信号が印加される。スイッチング回路は、半導体スイッチ素子20bの出力端子と半導体スイッチ素子20dの入力端子の間に接続されるキャパシタンス素子60と、半導体スイッチ素子20bの入力端子と半導体スイッチ素子の出力端子20dの間に接続されるキャパシタンス素子61とを備える。キャパシタンス素子60,61は、半導体スイッチ素子20b、20dの各々の入力端子と出力端子間の寄生容量を、半導体スイッチ素子20b、20dに供給されるパルス状信号のクロック周波数のN倍の周波数において低減する容量を有する。

(もっと読む)

半導体装置

【課題】周辺の回路構成を複雑にすることなく、繰り返しのデータの書き込みの際の劣化を低減することが可能な、不揮発性スイッチとして用いる半導体装置を提供する。

【解決手段】電源電圧が停止しても導通状態に関するデータの保持を、チャネル形成領域に酸化物半導体層を有する薄膜トランジスタに接続されたデータ保持部で行う構成とする。そしてデータ保持部は、ダーリントン接続された電界効果トランジスタ及びバイポーラトランジスタを有する電流増幅回路における、電界効果トランジスタのゲートに接続することでデータ保持部の電荷をリークすることなく、導通状態を制御する。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮する回路を提供する。

【解決手段】スイッチング回路10の入力端子21と出力端子22との間、入力端子21と共通端子23との間及び出力端子22と共通端子23との間の少なくとも一つに接続される容量抑制素子部50を備え、容量抑制素子部50は、容量抑制素子部が接続される半導体スイッチ素子20の端子間の寄生容量を、パルス状信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、容量抑制素子部が接続されていない場合より低減する。

(もっと読む)

電圧レギュレータ

【課題】ノーマリオン型のトランジスタをオンオフ駆動できるようにする。

【解決手段】電圧レギュレータは,入力電圧に接続されたノーマリオン型の第1のトランジスタと,第1のトランジスタと出力端子との間に設けられたインダクタと,第1のトランジスタとインダクタとの接続ノードとグランド電圧との間に設けられた還流回路と,第1のトランジスタのゲートに駆動信号を供給する駆動回路と,グランド電圧に接続され,第1のトランジスタのオンオフ動作により接続ノードに生成されるパルス信号に基づいて負電圧を生成し,負電圧を駆動回路に供給する負電圧生成回路とを有する。

(もっと読む)

スイッチ装置

【課題】オン抵抗を小さく抑えながらも、スイッチ素子の駆動に必要な電力を小さく抑えることができるスイッチ装置を提供する。

【解決手段】スイッチ装置1は、スイッチ素子10のドレイン電極12とソース電極13との間を流れるドレイン電流Idsを計測する電流モニタ部23を駆動回路20に備えている。制御部22は、スイッチ素子10がオンしている状態において、スイッチ素子10のオン抵抗が規定値以下になるように電流モニタ部23の計測値(ドレイン電流Ids)に応じてゲート電圧Vgsの下限値を設定する。制御部22は、設定した下限値を下回らない範囲で、電圧印加部21から印加可能な最小の大きさにゲート電圧Vgsを調節する。電圧印加部21は、制御部22に制御され、制御部22で決定された大きさのゲート電圧Vgsをスイッチ素子10に印加する。

(もっと読む)

スイッチングアンプ

【課題】 2つの出力素子の入力が共にハイレベルになり次に電源オン状態に移行する際に動作を開始することができないとい問題を解決する。

【解決手段】 電源制御手段16は、スイッチングアンプ10が電源オフ状態に移行する場合に、スイッチSWがオフ状態になり、コンデンサC102を強制的に放電させ、第2電源電圧V2に対する基準電位V3を強制的に低下させる。基準電位V3に対するロジック電源電圧Vddは、基準電位V3と同じだけ低下していくので、基準電位V3から見たロジック電源電圧Vddは固定される。定電流回路は、第2電源電圧V2に対する基準電位V3の低下に伴い、定電流Iを減少させ、第1の電流I1および第2の電流I2を減少させる。従って、基準電位V3から見たロジック電源電圧Vddが低下しないうちに、第1の電流I1、第2の電流I2を減少させ、パルス発生手段の動作を正常な状態で終了できる。

(もっと読む)

差動入力バッファ

【課題】動作モード切り換え時におけるノイズを抑制する。

【解決手段】差動入力バッファ1は、動作モードを通常状態又は省電力状態のいずれかに切り換える電源回路MN1,MN2と、ソースフォロア回路を構成する半導体素子MP1,MP3及びMP2,MP4のそれぞれの寄生容量の合計である第1の寄生容量に対応する第2の寄生容量を有する半導体素子MP7,MP8により構成されるダミー回路とを有し、動作モードの切り換え時に第1の寄生容量に起因して発生する電流の流通方向と、動作モードの切り換え時に第2の寄生容量に起因して発生する電流の流通方向とが共通の配線において相反する構成を有する。

(もっと読む)

リセット回路

【課題】ウォッチドッグのための特殊な構成を追加することなく、マイコンラッチ時に自動的かつ確実にマイコンにリセットをかける

【解決手段】水晶振動子Xtalを用いた水晶発振回路からクロック信号を入力されるマイコン200のリセット回路100であって、マイコン200は、出力がHighとLowとで周期的に変動するGPIO端子201を備え、クロック信号の入力が停止されたときに自動的にリセット状態となる構成とされ、リセット回路100は、GPIO端子201の出力をコンデンサを用いて平滑し、平滑電圧がHighとLowの中間電位のときは水晶振動子Xtalの負性抵抗より小さい抵抗を発生して水晶振動子Xtalに印加し、平滑電圧がHighとLowのいずれかになると水晶振動子Xtalの負性抵抗以上の抵抗を発生して水晶振動子Xtalに印加する。

(もっと読む)

スイッチング回路

【課題】スイッチング素子の動作に起因するノイズの大きさが低減された、小型で製造コストの低いスイッチング回路を提供する。

【解決手段】スイッチング素子と、一定周期でパルス波のドライバ信号を出力するドライバ信号出力回路と、ドライバ信号のパルス波の周期を複数含む一定期間内において駆動力を変化させながら、ドライバ信号の周期に同期してスイッチング素子を駆動する駆動回路とを備える。

(もっと読む)

スイッチング回路及び半導体モジュール

【課題】スイッチング制御する制御回路の負担を軽減するスイッチング回路を提供する。

【解決手段】第1のスイッチング素子の制御電極と第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、第2のスイッチング素子の高電位側電極は、第1のスイッチング素子の制御電極に電気的に接続され、第2のスイッチング素子の低電位側電極は第1のスイッチング素子の低電位側電力端子に電気的に接続され、第2のスイッチング素子の制御電極は、抵抗と制御回路の間に接続されている。

(もっと読む)

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

表示装置

【課題】表示装置の走査信号線の駆動回路において、走査信号線の出力波形なまりを改善し、表示品質を高めた表示装置を提供する。

【解決手段】表示装置は、複数の信号線Gnに対して、順に画素トランジスタを導通させる電位であるアクティブ電位を印加する駆動回路210を備え、前記駆動回路210は、前記複数の信号線のうちの一の信号線である出力信号線の一端に、より上位の前記出力信号線において出力されるアクティブ電位が入力されることに起因して、クロック信号を印加してアクティブ電位を出力させる主駆動回路240と、前記出力信号線の他端、及び前記クロック信号の信号線が、ソース/ドレインを介して接続されたトランジスタである補助トランジスタを含む補助駆動回路250と、を有する。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

スイッチング回路

【課題】ゲート電流を抑制し且つ高速動作が可能なスイッチング回路を提供する。

【解決手段】窒化物半導体層の主面上に、第1の主電極Dswと第2の主電極Sswの間に配置された制御電極Gswを有するスイッチング素子Tswと、スイッチング素子Tswの第1の主電極Dswにアノード端子が接続された第1の整流素子D1、第1の整流素子D1のカソード端子に第1の主電極DD1が接続され、スイッチング素子Tswの制御電極Gswに第2の主電極SD1が接続された第1の駆動素子TD1、スイッチング素子Tswの制御電極Gswに第1の主電極DD2が接続され、スイッチング素子の第2の主電極Sswに第2の主電極SD2が接続された第2の駆動素子TD2、及び、第1の駆動素子TD1の制御電極GD1と第2の駆動素子TD2の制御電極GD2にそれぞれ入力される制御信号を受信する入力端子IN_H,IN_Lを有する駆動回路10とを備える。

(もっと読む)

電子制御装置

【課題】電流検出用の抵抗を使用せず、簡易回路で負荷ショートの保護が可能な電子制御装置を得る。

【解決手段】パルス発生源3と第2のスイッチング素子21との間に接続されたコンデンサ23を有するトリガ回路と、負荷4と第1のスイッチング素子11との交点と第2のスイッチング素子21のベース端子との間にダイオード25を介して接続されるラッチ回路を有する制御回路を備え、パルス発生源が駆動信号を出力時は、トリガ回路を介し所定時間第2のスイッチング素子21をオンし、第1のスイッチング素子11もオンさせ、前記交点の電圧で、ラッチ回路を介し第2のスイッチング素子21のオン状態を継続させる。駆動信号の停止時は、第1、第2のスイッチング素子は共にオフとし、負荷ショートが発生した時は、パルス発生源3の駆動信号が出力されている場合でも、交点の電圧で、ラッチ回路を介して第2のスイッチング素子21をオフし、第1のスイッチング素子11もオフする。

(もっと読む)

デジタル入力回路およびシステム監視回路

【課題】消費電力を低減させることを目的とする。

【解決手段】デジタル入力回路の分圧回路11において、システム4からの入力信号が伝搬する信号ラインL1から分岐される分岐ラインL2にスイッチング素子23を設け、このスイッチング素子23をマイクロコントローラ3の動作タイミングに応じてオンオフ制御する。これにより、スイッチング素子23がオフとされている期間において、分圧回路11に流れる電流を遮断でき、消費電力を低減させることが可能となる。

(もっと読む)

高周波スイッチモジュール

【課題】スイッチポート切替時間が短く、かつ低消費電力、低面積を同時に満たす高周波スイッチモジュールを提供する。

【解決手段】デコーダ3は、前記スイッチポートを切替える制御信号CNTに応答し、スイッチ7を制御するためのスイッチ制御信号SWCNTを生成して、スイッチ切替タイミング検出器は、スイッチ制御信号SWCNTに応答し、スイッチ切替え検出信号t_swを生成し、周波数制御信号生成器は、スイッチ切替え検出信号t_swに応答し、周波数制御信号ICONT、CCONTを生成し、負電圧発生回路は、周波数制御信号ICONT、CCONTに応答し、前記負電圧発生回路内で生成したクロック信号の周波数を2つ以上のそれぞれ異なる周波数に切替つつ、負電圧出力信号NVG_OUTを生成し、スイッチ7は、スイッチ制御信号SWCNTと前記負電圧出力信号NVG_OUTに応答し、複数の高周波信号ポート間の経路を切替える。

(もっと読む)

スイッチ制御回路、及び印刷装置

【課題】スイッチがオフ状態(非導通状態)である場合の消費電力を低減する。

【解決手段】スイッチ制御回路は、制御端子に印加される電圧に基づいて、第1の電源線VDDから供給される電力を出力状態と非出力状態との間で切り替えるP−FET11と、第1の電源線VDDと制御端子との間に接続される抵抗R1と、制御端子と第2の電源線との間に、第1のコンデンサーC1と第2のコンデンサーC2が直列に接続されているコンデンサー分圧回路13と、第1のコンデンサーC1と並列に接続され、自素子の両端間の電位差が、予め定められた閾値以上である場合に導通状態になり、電位差が閾値未満である場合に非導通状態になる制御素子(ZD)と、第2のコンデンサーC2と並列に接続され、自スイッチの両端間を導通状態と非導通状態との間で切り替えるスイッチSWと、を備える。

(もっと読む)

41 - 60 / 754

[ Back to top ]