Fターム[5J055DX14]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442) | P型 (99)

Fターム[5J055DX14]に分類される特許

1 - 20 / 99

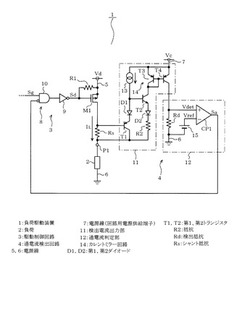

過電流検出回路および負荷駆動装置

【課題】回路用電源電圧としてむやみに高い電圧を用いることなく、シャント抵抗の低電位側端子の電圧がグランド電位付近となる異常が原因で生じる過電流を検出する。

【解決手段】検出電流出力部11は、シャント抵抗Rsの各端子電圧を入力し、その入力した電圧から負荷2に流れる電流に応じた検出電流を出力する。過電流判定部12は、検出電流に基づいて負荷2に過電流が流れているか否かを判定する。検出電流出力部11において、通常時に駆動用電源電圧Vdに近い電圧が印加される部分と、回路用電源電圧Vcに近い電圧が印加される部分との間の経路に第1ダイオードD1および第2ダイオードD2を逆方向に介在させることにより、第1トランジスタT1および第2トランジスタT2がブレークダウンして電流が流れることを阻止する。

(もっと読む)

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

チョッパ型コンパレータ

【課題】動作時の貫通電流を低減させ、かつ動作スピードをあまり損なわないチョッパ型コンパレータを得る。

【解決手段】インバータと接地電圧端子間にNチャネル型MOSトランジスタ8を接続し、そのゲート端子に可変電圧源9を接続する。インバータと電源電圧端子間にPチャネル型MOSトランジスタ7を接続し、そのゲート端子に可変電圧源10を接続する。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

スイッチング回路

【課題】スイッチング回路のデッドタイム制御における電力効率を向上させる。

【解決手段】スイッチング制御部2は、パルス信号Aがロウレベルの時に、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち上がったのを検出してから、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち上がるように、スイッチング部Wを制御し、パルス信号Aがハイレベルの時に、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち下がったのを検出してから、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち下がるように、スイッチング部Wを制御する。

(もっと読む)

小型電気機器

【課題】モータの起動時のうなり音を回避し、使用者に不快感を与えることなく使用できる小型電気機器を提供することを課題とする。

【解決手段】DCモータ11の起動時に、DCモータ11の回転数が安定した安定動作時のスイッチングパルス幅と同等のスイッチングパルス幅でスイッチング素子13をスイッチング制御し、DCモータ11が安定動作しているときと同等の駆動電圧をDCモータ11に供給してDCモータ11を起動するように構成される。

(もっと読む)

バッファ回路

【課題】スルーレートが高いバッファ回路を提供する。

【解決手段】単極性の複数のトランジスタと、容量素子と、を有し、該バッファ回路の利得が、前記複数のトランジスタのすべての利得により決定される構成としたバッファ回路を提供する。駆動能力が高く、且つ高周波における利得が高いバッファ回路を得ることができる。このようなバッファ回路はスルーレートも高いものとなる。該バッファ回路を構成する単極性の複数のトランジスタはPチャネル型トランジスタであってもよいし、Nチャネル型トランジスタであってもよい。

(もっと読む)

ワイヤ遷移を検出し支援する回路および方法

【課題】ワイヤ上の信号遷移を支援する回路及び方法を提供する。

【解決手段】回路は、第1のサブ回路を含み、サブ回路は、回路の出力(34)に結合されている第1のトランジスタ(16)を、立ち上がり遷移の間ターンオンさせ、その後ターンオフさせる。第1のトランジスタ(16)は、出力(34)を高状態に駆動して、立ち上がり遷移を支援する。回路は、第2のサブ回路を含み、第2のサブ回路は、回路の出力(34)に結合されている第2のトランジスタ(25)を、立ち下がり遷移の間ターンオンさせ、その後ターンオフさせる。第2のトランジスタ(25)は、出力(34)を定状態に駆動して、立ち下がり遷移を支援する。

(もっと読む)

電流源回路

【課題】矩形波の信号入力に応じて出力する出力電流の波形を矩形波に近づけることが可能な電流源回路を提供する。

【解決手段】電流源回路は、電圧端子に一端が接続された第1のMOSトランジスタと、第1のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第2のMOSトランジスタと、電圧端子に一端が接続された第3のMOSトランジスタと、第3のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第4のMOSトランジスタと、を備える。この電流源回路は、第1のMOSトランジスタおよび第4のMOSトランジスタに電流が流れるように第1の入力端子にバイアス電圧が印加された状態で、第2の入力端子に印加されるスイッチ電圧に応じて、第2のMOSトランジスタおよび第3のMOSトランジスタのオン/オフを同期して制御する。

(もっと読む)

双方向スイッチシステム、双方向スイッチ、スイッチングマトリックスおよび医療用刺激装置を制御する制御回路構造ならびに方法

高電圧差動信号方式のためのドライバ回路

高電圧差動信号方式のためのドライバ回路(200)。この回路は、入力に応答して第1の出力で第1の正の遷移を生成する第1の正のドライバ(205A)を含む。この回路は更に、第1の正のドライバに結合され、電流の生成を可能にする第1の電流要素(210A)を含む。更に、この回路は、第1の電流要素(210A)に結合され、第1の電流要素に起因して、入力及び電流に応答して、第1の正の遷移の速度に類似する速度で、第2の出力で第1の負の遷移を生成する、第1の負のドライバ(215A)を含む。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】1つの回路ブロックに対して設けた複数の電源スイッチを順次オンさせていく構成において、スイッチオンのタイミングを適切に制御可能な半導体装置を提供する。

【解決手段】半導体装置は、内部回路と、内部回路へ電流を供給する複数の並列な経路にそれぞれ設けられ、導通状態又は非導通状態に制御される複数の電源スイッチと、内部回路への電源を遮断する指示又は電源を供給する指示を行なう命令部と、内部回路に電源スイッチを介して供給される電流が定常状態であるか否かを検知して検知結果を出力する変動検知部と、命令部の電源供給指示に応答して、複数の電源スイッチを順次導通状態にして内部回路への電流供給量を増やしていく際に、複数の電源スイッチを導通させるタイミングを検知結果に応じて制御する論理回路とを含む。

(もっと読む)

半導体装置及びその耐圧制御方法

【課題】従来の半導体装置では、チップ面積を小さくすることができない問題があった。

【解決手段】本発明の半導体装置は、第1の電圧VHと、第1の電圧VHよりも低い第2の電圧VLと、第1の電圧VHと第2の電圧VLとの間の第3の電圧VMとに基づき動作する半導体装置であって、第2の電圧VLから第1の電圧VHに至る振幅を有する信号がゲートに入力されるトランジスタを少なくとも1つ含む出力回路20と、出力回路20に含まれるトランジスタのゲートの電圧を制御する第1の制御信号と、トランジスタのバックゲート領域の電圧を制御する第2の制御信号と、ディープウェル領域の電圧を制御する第3の制御信号と、を生成する制御回路10と、を有し、制御回路10は、第1の制御信号と第2の制御信号との電圧差を第1の電圧VHと第3の電圧VMとの電圧差及び第2の電圧VLと第3の電圧VMとの電圧差のうち大きな電圧差以下とする。

(もっと読む)

スイッチング素子の駆動回路、コンバータ

【課題】 FETを駆動する駆動回路の動作を安定化する。

【解決手段】 FETを駆動する駆動回路であって、FETのオン時にFETに印加される電圧を保持するコンデンサと、FETのオフ期間に、コンデンサに保持された電圧が供給されてFETをオフさせるトランジスタを有する。

(もっと読む)

電子制御装置

【課題】誘導性負荷に通電される電流値をPWM制御する電子制御装置において、負荷の個体差、温度特性によるインダクタンスと抵抗値のばらつきがあってもオーバーシュート・アンダーシュートの発生を回避でき、短時間に精度よく電流制御を行える方法を提供する。

【解決手段】直前のPWM周期の電圧を印加する区間の電流計測値の最大値および電圧を印加しない区間の電流計測値の最小値を計測する電流計測部244と、電流最大値と電流最小値から負荷11のインダクタンスと抵抗値を推定する負荷R・L推定部245と、負荷のインダクタンス値と抵抗値とから次PWM周期の電圧印加時間による誘導性負荷に通電される電流を予測して、目標電流設定部243で設定された目標電流と比較することにより、次PWM周期のデューティ比を決定するPWM設定部246とを備え、次PWM周期のデューティ比でPWM駆動回路を駆動する。

(もっと読む)

線形サンプリングスイッチ

【課題】 線形サンプリングスイッチ

【手段】 サンプリング回路はpチャネル及びnチャネル電界効果トランジスタ(FET)で構成される。pチャネルFET(42)のソースノードはnチャネルFET(40)のドレインノードに結合され、pチャネルFET(42)のドレインノードはnチャネルFET(40)のソースノードに結合される。サンプリングクロックは各FETのゲートノードに結合される。線形サンプリング回路の第1の側はアナログまたはRF信号源に接続され、そして線形サンプリング回路の向う側は保持キャパシタ(44)に接続される。nチャネルFETはnチャネル幅を有する。pチャネルFETはpチャネル幅を有する。結果としてスイッチのオン抵抗の線形性を増加させるために、pチャネル幅はnチャネル幅よりも大きい。

(もっと読む)

半導体集積回路装置

【課題】電圧パルスで振動子を駆動する送信回路において、誤送信や波形オーバーシュートを改善するため出力がハイインピーダンス状態にならない回路構成を提供し、且つ複数チャネルを集積化した半導体集積回路装置を実現する。

【解決手段】最も絶対値の大きい正電圧VPP1及び負電圧VNN1が供給された従来のパルス発生回路部10と、2番目に絶対値が大きい正電圧VPP2が供給されたP型アナログスイッチタイプのパルス発生回路部20と、2番目に絶対値が大きい負電圧VNN2が供給されたN型アナログスイッチタイプのパルス発生回路部30と、接地電位が供給されたN型アナログスイッチタイプの接地レベルダンピング回路部40とを備える送信回路において、10、20、30、及び40がそれぞれ出力端子OUTに接続される。スイッチ制御信号S1〜S5によって10、20、30、及び40を各別にオンオフして超音波振動子50を駆動する。

(もっと読む)

半導体集積回路および電源装置

【課題】電源線や接地線に重畳されるスイッチングノイズを低減することのできる半導体集積回路および電源装置の提供を図る。

【解決手段】第1電源線VINと第2電源線GNDとの間に直列に設けられた複数組の第1スイッチ素子Tp1〜Tp3および第2スイッチ素子Tn1〜Tn3を有し、基準電圧Vrに基づいて前記第1および第2スイッチ素子をオン/オフ制御する半導体集積回路であって、前記各第1スイッチ素子を、それぞれ遅延時間を設けて順に制御する制御回路14を有するように構成する。

(もっと読む)

短絡検査装置、および負荷駆動装置

【課題】出力バッファ回路を構成する各出力トランジスタの破損や劣化を回避しつつ、短絡の有無を検査することを可能にする。

【解決手段】高電位電源線と低電位電源線との間に4個の出力トランジスタをブリッジ接続してなる出力段を有するアンプにて、高電位電源線と、この出力段の一方の出力端子OUTMとの間に抵抗R1およびスイッチSW1を直列に介挿するとともに、出力端子OUTMと低電位電源線との間に抵抗R2およびスイッチSW2を直列に介挿する。そして、上記各出力トランジスタをオフにして、スイッチSW1をオフに、かつスイッチSW2をオンにした場合に出力端子OUTMの電圧が閾値電圧を超えているか否かにより天絡の有無を判定し、スイッチSW1をオンに、かつスイッチSW2をオフにした場合に出力端子OUTMの電圧が閾値電圧を下回っているか否かにより地絡の有無を判定する。

(もっと読む)

電圧検出回路

【課題】小さい回路規模の電圧検出回路を提供する。

【解決手段】最低動作電源電圧と等しい閾値電圧の絶対値Vtpを有するPMOS11は、ゲートを接地端子に接続され、ソースを電源端子に接続され、ドレインをPMOS12のソースに接続される。PMOS12は、ゲートを基準電圧入力端子に接続され、ドレインを電圧検出回路の出力端子に接続される。容量15は、電圧検出回路の出力端子と接地端子との間に設けられる。インバータ41は、入力端子を電圧検出回路の出力端子に接続される。

(もっと読む)

1 - 20 / 99

[ Back to top ]