Fターム[5J055DX12]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442)

Fターム[5J055DX12]の下位に属するFターム

N型 (195)

P型 (99)

閾値 (83)

構造 (11)

MOSFET、MISFET (1,263)

MESFET (9)

接合型FET (6)

GaAsFET (12)

デュアルゲートFET (10)

Fターム[5J055DX12]に分類される特許

741 - 754 / 754

半導体装置

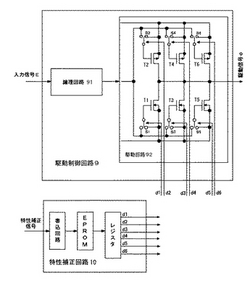

【課題】 半導体スイッチング素子のコレクタ電流の立ち上がりおよび立下り時における電流変化の傾きを変化できないため、ノイズ発生およびスイッチング損失を最適に設定できない。

【解決手段】 半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段(9)とからなる半導体装置において、前記駆動制御手段(9)に、駆動能力の異なる複数個の駆動デバイス(T1〜T6)を備え、その駆動デバイスの中からいずれか1つ、もしくは複数個を選択して用いることにより、半導体スイッチング素子の動作特性を補正する特性補正手段(10)を備える。

(もっと読む)

半導体スイッチ回路

【課題】 通過経路の伝送損失を低減する。

【解決手段】 内部送受信アンテナ端子24、内部受信アンテナ端子21、外部アンテナ端子27、第1の受信端子25、第2の受信端子23、および送受信端子28を有する。また、内部受信アンテナ端子21と第1の受信端子25との間のFETスイッチ1、内部受信アンテナ端子21と第2の受信端子23との間のFETスイッチ2、第1の受信端子25と外部アンテナ端子27との間のFETスイッチ3、第2の受信端子23と外部アンテナ端子27との間のFETスイッチ4、内部送受信アンテナ端子24と第2の受信端子28との間のFETスイッチ5、外部アンテナ端子27と送受信端子28との間のFETスイッチ6、内部送受信アンテナ端子24と送受信端子28との間のFETスイッチ7を備える。そのFETスイッチ1〜7の導通/非導通を制御するデコーダ51を備える。

(もっと読む)

直流モータの電流制御回路およびこの回路を具備する直流モータ

【課題】 PWM駆動のHブリッジ回路を採用してモータ駆動電流を精度良く検出し、直流モータを効率よく正転、逆転制御すると共にモータ駆動電圧を大きく設計することができる直流モータの電流制御回路およびこの回路を具備する直流モータを提供する。

【解決手段】 シャント抵抗RSを用いてモータ電流を検出するパルス幅変調(PWM)駆動方式のHブリッジ回路を用いた直流モータの電流制御回路において、シャント抵抗RSの両端を分圧回路より成る2個のアッテネータ21a、21bのそれぞれの一端に接続し、アッテネータ21a、21bの他端とシャント抵抗RSの何れか一方の側との間にアッテネータ駆動回路を接続し、アッテネータ駆動回路の予め設定した倍率で増幅してアッテネータ出力を生成し、2個のアッテネータの分圧回路それぞれの中点a、bの電圧を差動増幅器23で増幅してモータ電流IMを検出する直流モータの電流制御回路。

(もっと読む)

高周波集積回路

【課題】 送信用高周波増幅器と高周波スイッチ回路を集積化した高周波集積回路において回路簡素化、半導体チップ面積の低減及びアイソレーション特性を向上させた高周波集積回路を提供することを目的とする。

【解決手段】 送信用高周波増幅器1から高周波スイッチ回路2へ、増幅された高周波信号と同一伝搬線路を介してプルアップ電位を給電して、高周波スイッチ回路2のFETスイッチ回路をプルアップする。

(もっと読む)

リセット回路

【課題】 パワーダウン時のパワーダウンリセット信号のタイミング制御を容易にし、繰り返し電源をオン/オフした時の起動不良を防ぐことを課題とする。

【解決手段】 リセット回路は、電源検出回路とパワーダウン検出回路と出力回路とを有する。電源検出回路は、パワーオン及びパワーダウン時に電源電圧(VDD)に応じた第1の電圧が第1のしきい値より大きいと第1の信号を出力し、低いと第2の信号を出力する。パワーダウン検出回路は、パワーダウン時に第2の信号が出力された後、電源電圧(VDD)に応じた第2の電圧が第2のしきい値より小さくなると第3の信号を出力する。出力回路は、パワーオン時に第1の信号が出力されるとローレベルからハイレベルに変化するパワーオンリセット信号(POR)を出力し、パワーダウン時に第3の信号が出力されるとハイレベルからローレベルに変化するパワーダウンリセット信号(POR)を出力する。

(もっと読む)

パルス幅変調されるモーター・コントローラの利得エラー相殺のための電力供給変動の抑止

ディスクドライブ・システムのボイスコイルモーター(22)の位置決めドライバ(32)が開示される。パルス幅変調される前段ドライバ(46)が、ボイスコイルモーター(22)を駆動するため「H」ブリッジに配置されるパワー・トランジスタ(50PH、50NH、50PL、50NL)に結合され、電力供給電圧(VM)でバイアスがかけられる。パルス幅変調される前段ドライバ(46)は、エラー増幅器(36)からのエラー信号とランプ・クロック生成器(48)で生成されるランプ・クロック信号(RMP)との比較に従ってパワー・トランジスタ(50PH、50NH、50PL、50NL)を駆動する。ランプ・クロック生成器(48)は、電力供給電圧(VM)の変動に応答してランプ・クロック信号(RMP)の高及び低限界を変調する制御回路を含む。高及び低限界のこの変調が、電力供給電圧(VM)の変動に起因するパワー・トランジスタ(50)の利得の変動を補償する。制御回路は、例えば、一定の周波数を維持するため、電力供給電圧(VM)の変動に従ってランプ・クロック信号(RMP)の勾配も変調し得る。  (もっと読む)

(もっと読む)

リーク電流低減方法

データ保持モードのために回路をパワー・ダウンする方法は、電源電圧ノードを能動状態の電源電圧レベルから非能動状態の電源レベルに変更する工程と、Pチャネル・デバイスのソースを電源電圧ノードに接続する工程と、Pチャネル・デバイスのバック・ゲートに保持用電源電圧レベルを供給する工程と、Pチャネル・デバイスのドレイン電圧を保持用電源電圧レベルとは異なる基準電圧レベルに変更する工程と、Pチャネル・デバイスのゲート電圧を基準電圧レベルに変更する工程とを含む。  (もっと読む)

(もっと読む)

移相回路、高周波スイッチ並びに移相器

小型でかつ広帯域な特性を持つ移相回路を提供するもので、スルーとキャパシタンスの容量とを切り替える第1のスイッチング素子と、スルーとグランドに対するキャパシタンス

の容量とを切り替える第2のスイッチング素子と、インダクタンスをもつ第1および第2のインダクタとを備え、第1と第2のスイッチング素子の一端同士を第1のインダクタで接続し、第1と第2のスイッチング素子の他端同士を第2のインダクタで接続し、第1のスイッチング素子の一端を高周波信号入力端子に接続し、第1のスイッチング素子の他端を高周波信号出力端子に接続して、定の条件をを満たす移相器を構成する。

(もっと読む)

低静止電流ラジオ周波数スイッチデコーダ

【課題】低静電流及び高スイッチング速度を有するオンチップのロジックデコーダを備えたRFスイッチを提供する。

【解決手段】RFスイッチのデコーダロジックは第1及び第2エンハンスメント型トランジスタとデプレション型トランジスタとを含む。デプレション型トランジスタ及び第1エンハンスメント型トランジスタのソースはVDD供給端に接続する。デプレション型トランジスタのゲートのドレイン及びゲートは第1エンハンスメント型トランジスタのゲートに接続する。第2エンハンスメント型トランジスタは接地端及びデプレション型トランジスタのドレインに接続する。活性状態では、デプレション型トランジスタは高電圧を第1エンハンスメント型トランジスタのゲートに供給してオンにして、RFスイッチをVDD供給端に接続する。

(もっと読む)

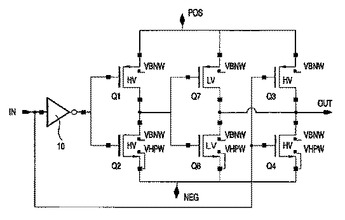

高速低電圧動作の高電圧駆動回路

不揮発性メモリなどの装置のための高電圧駆動回路。ここでは、低電圧ドライバが2つの異なる態様で高電圧ドライバと組み合わせられる。1つには、入力非依存型の実施例があり、低電圧ドライバ(Q7,Q8)が、高電圧ドライバと直接並列に接続され、これにより、高電圧動作のために高電圧信号パスを提供し、低電圧動作のために低電圧信号パスを提供する。代替の部分的入力依存型実施例では、低電圧ドライバが高電圧ドライバ(Q9,Q10)の出力に接続され、これが部分的レベルシフタ(Q1,Q6)を有することができる。この低電圧ドライバ(Q9,Q10)の出力は、全体のステージの出力端子を形成し、部分的レベルシフタ(Q1,Q6)が正又は負のレベルシフトの高電圧ドライバであるかどうかに基づいて、プルアップ/プルダウントランジスタ(Q11)を有する。

(もっと読む)

(もっと読む)

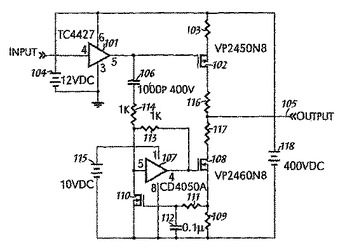

静電結合を用いた高電圧パルスドライバ

高電圧システムに共通する、高電源リプルにおいて有用である静電結合を用いた高電圧ドライバである。それは、デューティサイクルの最大範囲を許容するが、変圧器の磁気の制限はなく、または、光学式の結合方法における複雑さの増加もない。それはまた、出力駆動ラインにアークする高電圧によって作成される過渡電圧においても、強固である。本発明はまた、特に例示的ディスプレイの応用における使用のために、低コストでの静電結合の使用を再構築するが、静電結合に特有の制限はない。  (もっと読む)

(もっと読む)

特に半導体素子のためのクロック受信器回路デバイス

本発明は、受信器(特にクロック受信器回路デバイス(1))を有する半導体素子、および、受信器(特にクロック受信器回路デバイス(1))に関する。上記受信器回路デバイスは、半導体素子の第1端子(3a)に接続されるように構成された第1入力部(9a)と、半導体素子の第2端子(3b)に接続されるように構成された第2入力部(8a)とを備えており、複数の、特に4つ以上のトランスファーゲート(4、5、6、7)を備えていることを特徴とする。  (もっと読む)

(もっと読む)

不足電流検出装置および方法

オン状態低電流検出器は、メインセル(32)およびセンスセル(34)を有するトランジスタを使用する。フィードバック回路(36)は、メインセルの目標電圧値を生成するレベルを負荷電流が下回るときにメインセル(32)両端間の電圧をほぼ一定の目標値に維持するように作用する。目標電圧値は、低電流検出比較器(18)の電圧を容易に測定できるように十分に高い。  (もっと読む)

(もっと読む)

ノイズ低減回路

【課題】 クロストークノイズを安定して減少させることができ、クロストークノイズに起因する回路誤動作を確実に防止できるノイズ低減回路を提供する。

【解決手段】 電源側に並列に接続された第一及び第二のトランジスタと、前記第二のトランジスタの出力側に直列接続された抵抗手段とを設け、前記抵抗手段の出力側と前記第一のトランジスタの出力側とを出力ノードで接続し、前記出力ノードから出力される出力電圧の変化が段階的になるように前記第一及び第二のトランジスタのオン/オフ動作タイミングを制御する制御回路を備えた。

(もっと読む)

741 - 754 / 754

[ Back to top ]