Fターム[5J055DX13]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442) | N型 (195)

Fターム[5J055DX13]に分類される特許

1 - 20 / 195

負荷駆動装置

スイッチング素子の駆動回路

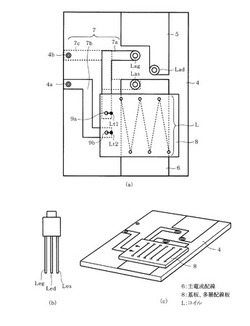

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

スタック電圧耐性を高めるためのキャパシタンス調整

【課題】 印加されるRF電圧Vswに制御可能に耐えるRFスイッチ、又はこのようなスイッチの製造方法を提供する。

【解決手段】 スイッチは直列接続された構成FETのストリングを有し、このストリングのノードは隣接するFETの各対の間にある。方法は、各構成FETにわたって分布するRFスイッチ電圧の不一致を減らすよう、容量的にストリングを有効に調整すべくストリングの異なるノードの間のキャパシタンスを制御し、それによって、スイッチ・ブレイクダウン電圧を高める。キャパシタンスは、例えば、ストリングのノードの間に容量特性配置することによって、及び/又は異なる構成FETの設計パラメータを変化させることによって、制御される。各ノードについて、ノードに現れるVswの比率による各有意なキャパシタの積の和は、おおよそ零になるよう制御され得る。

(もっと読む)

チョッパ型コンパレータ

【課題】動作時の貫通電流を低減させ、かつ動作スピードをあまり損なわないチョッパ型コンパレータを得る。

【解決手段】インバータと接地電圧端子間にNチャネル型MOSトランジスタ8を接続し、そのゲート端子に可変電圧源9を接続する。インバータと電源電圧端子間にPチャネル型MOSトランジスタ7を接続し、そのゲート端子に可変電圧源10を接続する。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

半導体装置

【課題】しきい値電圧のばらつきの影響を低減する。

【解決手段】トランジスタのゲート・ソース間に設けられた容量素子に電荷を充電し、その後容量素子に充電された電荷を放電することで該トランジスタのしきい値電圧を取得し、その後負荷に電流を流す半導体装置において、容量素子の一方の端子の電位は、ソース線の電位より大きく設定し、ソース線の電位は電源線の電位及び負荷のカソード側の電位よりも小さい電位に設定する。

(もっと読む)

ブートストラップ回路

【課題】飛び込みの影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第4TRから構成され、第1TRにおいて、一方のS/D領域は第2TRの一方のS/D領域に接続され、他方のS/D領域には、2相のクロックのうち一方のクロックが印加され、ゲート電極は、第3TRの一方のS/D領域に接続され、第2TRにおいて、他方のS/D領域は電圧供給線に接続され、第3TRにおいて、他方のS/D領域には入力信号が印加され、ゲート電極には他方のクロックが印加され、第1TRのゲート電極と第3TRの一方のS/D領域とは、第3TRがオフ状態になると浮遊状態となるノード部を構成し、第4TRにおいて、一方のS/D領域は、反転回路の入力側に接続されると共に、該反転回路の出力側と第2TRのゲート電極とが接続されており、他方のS/D領域は入力信号が印加され、ゲート電極には他方のクロックが印加される。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

電流制御用半導体素子およびそれを用いた制御装置

【課題】ゲインa、およびオフセットbの変動を動的に補正することで、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】

同一半導体チップ上に、トランジスタ4と、電流−電圧変換回路22とADコンバータ23とを有する。参照電流生成回路6,6’は、負荷2の電流に電流パルスIcを重畳して、ADコンバータが出力する電圧デジタル値を変動させる。ゲインオフセット補正部8は、参照電流生成回路6,6’による電圧デジタル値の変動を信号処理して、ADコンバータ23が出力する電圧デジタル値と負荷の電流デジタル値の線形関係式におけるゲインa,a’及びオフセットb,b’を動的に取得する。電流デジタル値演算部12は、ゲインオフセット補正部8により取得されたゲイン及びオフセットを用いて、ADコンバータが出力する電圧値を補正する。

(もっと読む)

パワーMOSFETの駆動回路およびその素子値決定方法

【課題】パワーMOSFETを高速駆動する場合であっても、寄生インダクタンスに流れる電流の時間変化に応じて発生する電圧に起因したセルフターンオンの発生を防止できるようにしたパワーMOSFETの駆動回路、また、その素子値決定方法を提供する。

【解決手段】制御回路が、駆動回路によってスイッチを駆動制御することで、(2)区間においてスイッチS2HおよびS2Lをオンすると共にその他をオフとし、(3)区間においてスイッチS1LおよびS3Hをオンすると共にその他をオフとする。すると、(2)〜(3)区間にかけて、ハイサイド側のMOSFETのゲートソース間を所定のインピーダンスに切り替えることができ、リカバリー後半に至ったとしてもハイサイド側のMOSFETのゲートソース間電圧Vgs1を閾値電圧Vt未満に抑制できる。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

リセット回路

【課題】減電検出を利用して確実にリセットを掛ける。

【解決手段】整流電圧V+をレギュレータ24にてレギュレートした定電圧3.3Vを駆動電圧とされるマイコン30のリセット端子に接続される端子2と抵抗R1を介して定電圧3.3Vを入力される端子4とを備え、端子4の入力電圧が第1閾値を下回るとマイコン30にリセット信号を出力するリセットIC12と、抵抗R2を介して端子4にコレクタを接続され、エミッタをグランドに接続され、スイッチングトランス21の出力が所定レベルを下回るとオンするように構成されたトランジスタQ1と、を備え、トランジスタQ1がオンすると端子4に第1閾値を下回る電圧を入力する。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

スイッチ回路及び半導体回路

【課題】 超音波診断装置等に適用され、送信信号または反射信号の電位変動に対しスイッチの誤動作や素子の破壊を起こすことなく、生体からの反射信号を広帯域、低雑音で受信回路に伝送するT/Rスイッチ回路を実現する。

【解決手段】 2つのMOSトランジスタのソースを共通に直列接続した共有ソース端子と、双方向スイッチ回路のゲート端子を共通に接続した共有ゲート端子と、2つのMOSトランジスタのドレインが入出力端子に接続されて構成される双方向スイッチ回路と、共有ゲート端子と共有ソース端子に接続され共有ソース端子の電位変動に対して共有ゲート端子の電位を同相で追従させ、スイッチのオンまたはオフ信号を共有ゲート端子に送るフローティングゲート電圧制御回路と、によりスイッチ回路を構成する。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3を介して、入力電圧Vin2がトランジスタT2のゲートに入力される。そのため、入力電圧Vin1,Vin2がともにハイとなったときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

スイッチング回路

【課題】スイッチング回路のデッドタイム制御における電力効率を向上させる。

【解決手段】スイッチング制御部2は、パルス信号Aがロウレベルの時に、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち上がったのを検出してから、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち上がるように、スイッチング部Wを制御し、パルス信号Aがハイレベルの時に、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち下がったのを検出してから、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち下がるように、スイッチング部Wを制御する。

(もっと読む)

地絡保護回路及びこれを用いたスイッチ駆動装置

【課題】部品点数の増加や出力効率の低下、セットのコストアップ、モノリシックICで実現する場合のチップ面積の増大を低減できる、スイッチ駆動装置用地絡保護回路の提供。

【解決手段】ブートストラップ回路D1、C1の充電電流IBが流れる経路上に設けられたセンス抵抗R3と、センス抵抗R3の両端間電圧ΔVと所定の閾値電圧Vthとを比較して地絡保護信号S1を生成するコンパレータ361と、前記ブートストラップ回路の正規充電動作中には地絡保護信号S1を無効としておく論理ゲート362と、を有する。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

1 - 20 / 195

[ Back to top ]