Fターム[5J055DX12]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442)

Fターム[5J055DX12]の下位に属するFターム

N型 (195)

P型 (99)

閾値 (83)

構造 (11)

MOSFET、MISFET (1,263)

MESFET (9)

接合型FET (6)

GaAsFET (12)

デュアルゲートFET (10)

Fターム[5J055DX12]に分類される特許

61 - 80 / 754

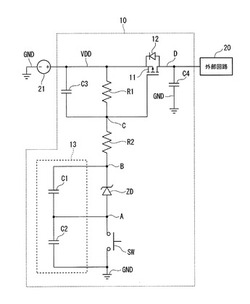

スイッチ制御回路、及び印刷装置

【課題】スイッチがオフ状態(非導通状態)である場合の消費電力を低減する。

【解決手段】スイッチ制御回路は、制御端子に印加される電圧に基づいて、第1の電源線VDDから供給される電力を出力状態と非出力状態との間で切り替えるP−FET11と、第1の電源線VDDと制御端子との間に接続される抵抗R1と、制御端子と第2の電源線との間に、第1のコンデンサーC1と第2のコンデンサーC2が直列に接続されているコンデンサー分圧回路13と、第1のコンデンサーC1と並列に接続され、自素子の両端間の電位差が、予め定められた閾値以上である場合に導通状態になり、電位差が閾値未満である場合に非導通状態になる制御素子(ZD)と、第2のコンデンサーC2と並列に接続され、自スイッチの両端間を導通状態と非導通状態との間で切り替えるスイッチSWと、を備える。

(もっと読む)

スイッチング回路装置及び制御回路

【課題】スイッチングトランジスタを適切にオフ動作する。

【解決手段】スイッチング回路装置は,高電位端子に接続されたドレインと低電位電源に接続されたソースとゲートとを有し,高電位端子と低電位電源との間に接続されたスイッチングトランジスタと,入力制御信号に応答して,スイッチングトランジスタのゲートにスイッチングトランジスタの閾値電圧より高い高電位と前記低電位電源の電位とを有する駆動パルスを出力する駆動回路とを有し,駆動回路は,スイッチングトランジスタのゲートとソースとの間に設けられた第1の駆動トランジスタを含む第1のインバータを有し,駆動パルスにより前記スイッチングトランジスタがオンからオフに変化するときに,第1の駆動トランジスタが導通してスイッチングトランジスタのゲートとソース間を短絡する。

(もっと読む)

ゲートドライブ回路

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子Q1であって、ドレインとソースとゲートとを有し、ゲートをドライブする信号とゲートとの間にコンデンサと抵抗の並列接続回路を介して接続され、オフ信号期間は、スイッチ素子Q1のゲート・ソース間を短絡するスイッチSW1とを備えることを特徴とするゲートドライブ回路。

(もっと読む)

ESD保護回路

【課題】ESDパルスをもれなく検出し、かつ通常の電源投入時やスパイクノイズ印加時の誤検出を抑制する。

【解決手段】第1検出回路7はESDパルスの印加開始時から第1所定時間だけ第1検出信号を出力する。第2検出回路9は、第1検出信号を受け、かつESDパルスの印加が第2所定時間だけ持続したときに第3所定時間だけ第2検出信号を出力する。第1所定時間は電源の立ち上がり時間よりも短い。第2所定時間は第1所定時間よりも短く、かつスパイクノイズの印加時間よりも長い。第3所定時間はESDパルスの印加時間よりも長い。クランプ回路11は、第1検出信号及び第2検出信号の少なくとも一方が出力されているときはゲート端子47をGND端子3とは絶縁する。プルアップ回路13は、ゲート端子47を、第2検出信号が出力されているときは電源端子1に接続し、第2検出信号を出力されていないときは電源端子1とは絶縁する。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】 スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路構成で実現する。

【解決手段】 トランス15の1次側をローサイドゲート駆動回路2の出力端子に接続し、トランス15の2次側をハイサイドスイッチング素子5のゲート入力側に接続する。ローサイド駆動回路2から正極性のゲート駆動電圧が出力されるとハイサイドスイッチング素子5のゲート‐ソース間には負極性の電圧が印加されてゲート電圧は閾値以下に抑えられるため、ローサイドスイッチング素子がターンオンする際にハイサイドスイッチング素子はオフ状態を維持する。

(もっと読む)

窒化物半導体装置

【課題】駆動回路への要求を緩和した使いやすい高速動作の窒化物半導体装置を提供する。

【解決手段】実施形態によれば、窒化物半導体を含む、nチャンネル型の第1〜第4トランジスタと、抵抗と、を備えた窒化物半導体装置が提供される。第1トランジスタは、第1ゲートと、第1ソースと、第1ドレインと、を有する。第2トランジスタは、第2ゲートと、第1ゲートと接続された第2ソースと、第2ドレインと、を有する。第3トランジスタは、第3ゲートと、第1ソースと接続された第3ソースと、第1ゲート及び第2ソースと接続された第3ドレインと、を有する。第4トランジスタは、第3ゲートと接続された第4ゲートと、第1ソース及び第3ソースと接続された第4ソースと、第2ゲートと接続された第4ドレインと、を有する。抵抗の一端は第2ドレインと接続され、他端は第2ゲート及び第4ドレインと接続される。

(もっと読む)

ゲート回路

【課題】本発明は、パワー素子の過電流を速やかに抑制しつつ、di/dtを小さくしてパワー素子をオフすることができるゲート回路を提供することを目的とする。

【解決手段】本発明に係るゲート回路は、パワー素子の過電流発生と同時にパワー素子のゲート電圧の一部を抵抗素子に負担させる過電流抑制手段を有する。さらに、パワー素子の過電流を抑制した後は、抵抗値の高い抵抗素子を用いてパワー素子をゆっくりオフするオフ動作遅延手段を有する。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

半導体スイッチ回路

【課題】入出力端子におけるアイソレーション劣化を抑制可能とする。

【解決手段】

第1の入出力端子51と第2の入出力端子52間に第1の単位スイッチ101が、第1の入出力端子51と第3の入出力端子間53に第2の単位スイッチ102が、それぞれ設けられ、第2の入出力端子52とグランドとの間に第1のシャントスイッチ103及び第1のDCカットコンデンサ49が、第3の入出力端子53とグランドとの間に第2のシャントスイッチ104及び第2のDCカットコンデンサ50が、それぞれ直列接続され、第1及び第2の単位スイッチ101,102を構成する第1乃至第4のFET1〜4のゲート・ドレイン間には、それぞれ付加容量41〜44が接続されると共に、第1の単位スイッチ101に対して第1の端子間連絡用抵抗器31が、第2の単位スイッチ102に対して第2の端子間連絡用抵抗器32が、それぞれ並列接続されたものとなっている。

(もっと読む)

スイッチ回路

【課題】高周波信号の伝送経路におけるインピーダンス変動の変動を抑え、高周波信号の挿入損失を向上させることができるスイッチ回路を提供すること

【解決手段】本発明にかかるスイッチ回路10は、入力端子11と出力端子12との間において信号を伝達する第1の伝送路上に設けられたFET14と、入力端子13と出力端子12との間において信号を伝達する第2の伝送路上に設けられたFET15と、入力端子13とFET15との間に一端が第2の伝送路と接続され、他端がオープンスタブ17である第3の伝送路と、第3の伝送路上に設けられたFET16と、を備え、第1の伝送路上を信号が伝達される場合、FET14及びFET16がオン状態となり、FET15がオフ状態となるように制御されるものである。

(もっと読む)

無線通信装置及び高周波スイッチ回路

【課題】回路規模が小さく、かつ消費電力の小さい無線通信装置及び高周波スイッチ回路を提供する。

【解決手段】無線通信装置100は、共用アンテナ101と、整合回路110、120と、高周波スイッチ回路130と、充電電力受電回路140と、応答器150と、から構成される。高周波スイッチ回路130は、電界効果トランジスタ131、132と、検波回路と、を備える。電界効果トランジスタ131、132のソース端子は共通接続される。検波回路は共通接続点に接続され、電界効果トランジスタ131のドレイン端子から出力された高周波信号を検波し、共通接続点の電位を基準とした検波電圧を電界効果トランジスタ131、132のゲート端子に印加する。電界効果トランジスタ131、132のドレイン端子間のインピーダンスは検波電圧に従って変化する。

(もっと読む)

半導体装置

【課題】本発明は、信号線駆動回路におけるトランジスタの特性のばらつきの影響を抑制

する技術に関する。

【解決手段】信号線駆動回路には、各々容量手段と供給手段とを有する第1電流源回路(

437)及び第2電流源回路(438)を設ける。シフトレジスタ(418)から供給さ

れるサンプリングパルスと外部から供給されるラッチパルスに従って、前記容量手段は、

n個のビデオ信号用定電流源(109)の各々から供給される電流を加算した電流を電圧

に変換し、前記供給手段は変換された電圧に応じた電流を供給することで、トランジスタ

の特性によらず、ビデオ信号に応じた電流出力を行うことを特徴とする。前記n個のビデ

オ信号用定電流源から供給される電流値は、20:21:・・・:2nに設定されて、階

調を表現することが可能となる。

(もっと読む)

スイッチング回路

【課題】電力効率を低下させずに高速動作可能なスイッチング回路を提供する。

【解決手段】スイッチング回路は、入力電圧を第1の電圧に変換する第1のDC/DCコンバータB1と、制御信号に応じて第1の電圧を出力するか否か切り替える第1のスイッチ回路C1と、第1のスイッチ回路からの電圧の過渡特性を制御する第1の制御回路D1と、高圧側電源に一端が、出力端子に他端が接続され、第1の制御回路からの電圧に応じてオンオフされる第1の能動素子A1と、入力電圧を第2の電圧に変換する第2のDC/DCコンバータB2と、制御信号に応じて第1のスイッチ回路とは相補的に第2の電圧を出力するか否か切り替える第3のスイッチ回路C3と、第3のスイッチ回路からの電圧の過渡特性を制御する第2の制御回路D2と、出力端子に一端が、低圧側電源に他端が接続され、第2の制御回路からの電圧に応じてオンオフされる第2の能動素子A2とを備える。

(もっと読む)

負荷駆動装置

【課題】スイッチ素子のオンオフ制御によって負荷を駆動する負荷駆動装置に関し、特に高いデューティ比のときに出力制御を高速に行い得る構成を実現する。

【解決手段】負荷駆動回路1には、外部からの駆動信号及び非駆動信号に応じて通電路10を流れる電流を制御するゲートドライバ6が設けられ、外部入力が非駆動信号から駆動信号に変化した直後には、コンデンサCBSからの放電に基づき、スイッチ素子M1がオン状態となるように通電路10を所定の大電流状態とし、その後の所定時期に、通電路10を流れる電流をスイッチ素子M1のオン状態が継続可能な所定の低レベルに変化させている。更に、駆動信号のデューティ比が所定値以上の場合には、ゲートドライバ6に駆動信号が入力されている間、チャージポンプ回路4によってコンデンサCBSに対する電流供給状態が維持されるようになっている。

(もっと読む)

半導体スイッチング素子の駆動回路

【課題】駆動電圧の印加に制限がある半導体スイッチング素子を高い周波数で高速にスイッチングできる駆動回路を提供する。

【解決手段】通電制御回路4が4つのスイッチS1〜S4とスイッチSa1及びSa2とを併せて制御することで、インダクタL1に電流を双方向に通電し、インダクタL1を介して流れる電流によりNチャネルFET1のゲートを充電し、また前記ゲートから放電させる。具体的にはダイオードDa1のカソードとダイオードDa2のアノードとの間に接続されるスイッチS1及びS2の直列回路と、コンデンサC1とコンデンサC2との間に接続され、共通接続点がNチャネルFET1のゲートに接続されるスイッチS3及びS4の直列回路とで構成し、インダクタL1を、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間に接続する。

(もっと読む)

半導体スイッチング素子の駆動回路

【課題】駆動電圧の印加に制限があるスイッチング素子を高い周波数で高速にスイッチングできる半導体スイッチング素子の駆動回路を提供する。

【解決手段】ダイオードDa1及びスイッチSa1,スイッチSa2及びダイオードDa2で正側,負側直列回路を夫々構成し、コンデンサC1,C2を正側,負側直列回路に夫々並列に接続し、スイッチSa1,Sa2によりゲート駆動用電源3とコンデンサC1,C2の間の接続形態を切替える。スイッチS1及びS2の共通接続点とFET1のゲートとの間に抵抗素子Rgを接続し、前記ゲートとゲート駆動用電源3の正側端子との間にスイッチS3を配置する。通電制御回路4は、スイッチSa1,Sa2,S1〜S3を制御してコンデンサC1,C2を充電する経路,FET1のゲートを充電する経路,ゲートの電位が電圧VGを超えようとする際にゲート駆動用電源3に還流電流を流す経路と、FET1のゲートを放電する経路を形成する。

(もっと読む)

マルチチャネル・パルス幅変調信号生成装置及び方法、並びにこれを具備するLEDシステム

【課題】マルチチャネル・パルス幅変調信号生成装置及び方法、並びにこれを具備するLEDシステムを提供する。

【解決手段】複数の負荷を駆動する技術に係り、具体的にはLEDのようなパルス幅変調方式で駆動される複数の負荷のターンオン・タイミングを分散させることにより、安定動作を実現可能な複数のパルス幅変調信号を生成するマルチチャネル・パルス幅変調信号生成装置及び方法、並びにこれを具備するLEDシステムに関したものであり、該生成方法は、周期及びパルス幅のうち少なくとも一つを設定する段階、及び周期及びパルス幅を有する複数のパルス幅変調信号を出力する段階を含み、該出力する段階は、周期とパルス幅との差に対応する位相差を有する少なくとも1対のパルス幅変調信号を出力する段階を含むことを特徴とし、該方法及び装置は、複数の負荷のターンオン・タイミングを分散させ、安定動作を実現可能な複数のパルス幅変調信号を提供する。

(もっと読む)

スイッチング回路および試験方法

【課題】半導体スイッチングデバイスが完全な機能を維持していることを保証するために、サービス中にそれらを試験する方法を提供する。

【解決手段】負荷および電圧源2に接続するためのスイッチング回路1であって、負荷への電力をスイッチオンおよびスイッチオフするための1つまたは複数のスイッチングデバイス6、7、...、nと、負荷を短絡し、それにより負荷を電圧源から隔離するためのプルダウンデバイス4と、一度に複数のスイッチングデバイスのうちの少なくとも1つを起動するために、電圧源が負荷から隔離されている間に動作させることができるコントローラ3とを備え、起動された前記スイッチングデバイスまたは個々のスイッチングデバイスを通って電流が流れ、この電流を測定して、起動された前記スイッチングデバイスまたは個々のスイッチングデバイスが適切に動作しているかどうかを試験することができるスイッチング回路1が開示される。

(もっと読む)

電流スイッチ回路およびDA変換器

【課題】差動出力電流のグリッチを打ち消しつつ、電源およびグランドに発生したノイズを打ち消す。

【解決手段】スイッチトランジスタM1、M2は、差動入力電圧Dip、Dimに基づいてスイッチング動作することで入力電流Iinを電流Ii1、Ii2に変換し、雑音電流発生回路1は、入力電流源2を介して流れる雑音電流を模擬したダミー電流Ibを生成し、スイッチトランジスタM3、M4は、差動入力電圧Dip、Dimに基づいてスイッチング動作することでダミー電流Ibを電流Ii3、Ii4に変換し、電流Ii1、Ii2に逆相的に重畳する。

(もっと読む)

61 - 80 / 754

[ Back to top ]