Fターム[5J055DX12]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442)

Fターム[5J055DX12]の下位に属するFターム

N型 (195)

P型 (99)

閾値 (83)

構造 (11)

MOSFET、MISFET (1,263)

MESFET (9)

接合型FET (6)

GaAsFET (12)

デュアルゲートFET (10)

Fターム[5J055DX12]に分類される特許

201 - 220 / 754

半導体装置及び無線通信装置

【課題】負バイアス発生回路中の容量に対する高速な充電手段を提供する。

【解決手段】負バイアス発生回路1中のダウンコンバータ12内に容量が存在する。高速な充電を行うためにはこの容量を小さくし必要な電荷の量を最小限にする。一方、ダウンコンバータ12内の容量とは別に外付け容量17を直接電源電圧に接続して充電する。ダウンコンバータ12内の容量の充電終了後に、並列に外付け容量17とダウンコンバータ12内の容量を接続する。これにより、充電高速化とリップルノイズへの耐性向上を両立することが可能となる。

(もっと読む)

時定数回路、スイッチ回路、DC/DCコンバータ及び表示装置

【課題】単調に減衰するだけの出力電圧特性に比べて、急峻に減衰した後に緩やかに減衰する出力電圧特性が得られる時定数回路等を提供する。

【解決手段】時定数回路10は、抵抗素子111と容量素子121との並列回路131,…が第一の端子14と第二の端子15との間に複数直列に接続されて成る直並列回路16と、第二の端子15に接続された第三の端子17と第四の端子18との間に接続された分圧用抵抗素子19と、を備えている。並列回路131は抵抗素子111と容量素子121とから成り、並列回路132は抵抗素子112と容量素子122とから成り、・・・、並列回路13nは抵抗素子11nと容量素子12nとから成る。nは、並列回路131〜13nの数であり、2以上の整数である。

(もっと読む)

チャージポンプ回路

【課題】短時間で出力電圧が昇圧規定電圧に達し、その後は小さいリップル幅を有するチャージポンプ回路を提供する。

【解決手段】チャージポンプ回路100は、制御部10と発振回路20と昇圧部30とを有する。発振回路20は、予め定められた周期のパルス信号を出力する。昇圧部30は、電圧を昇圧する複数個の昇圧回路を備え、制御部10が出力する昇圧信号に応じて電荷量を出力する。制御部10におけるコンパレータ回路13は、昇圧部30から出力される電圧と、予め定められた規定電圧とを比較し、比較結果に応じて昇圧信号Cont4〜Cont1を出力し、昇圧部30からの供給電荷量を制御する。

(もっと読む)

チャージポンプ

【課題】 高速動作するコンパレータを必要とせず、所望の電圧値の電圧を精度良く出力することができるチャージポンプを提供する。

【解決手段】 チャージポンプ1は、出力用キャパシタC1、C2、フライングキャパシタC3、入力電源HPVDD、SPVDDとの間に介在するスイッチ回路20と、制御部10とを具備する。制御部10は、スイッチ回路20を介して入力電源によるフライングキャパシタC3の充電とフライングキャパシタC3から出力用キャパシタC2への電圧の再分配を行わせる。制御部10は、入力電源SPVDDにフライングキャパシタC3の充電を行わせる際、PチャネルトランジスタP5のコンダクタンスまたは出力電流値を漸次増加させ、フライングキャパシタC3の充電電圧CPが予め与えられた基準電圧VLMTを越えたのを検出して当該トランジスタをOFFさせる充電制御手段を具備する。

(もっと読む)

半導体集積回路

【課題】PKGの設計期間を遅延させることなくクロストーク耐性を向上させることが可能な半導体集積回路を提供する。

【解決手段】複数の信号配線を有するChip20において、一の信号配線と前記一の信号配線に隣接する一方の隣接信号配線と前記一の信号配線に隣接する他方の隣接信号配線との間で生じるクロストークの発生量を抑制するための補正係数31と、前記一の信号配線に送出される一の信号、前記一方の隣接信号配線に送出される一方の隣接信号、および前記他方の隣接信号配線に送出される他方の隣接信号の組み合わせパターンと、に基づいて、前記一の信号のスルーレートの低減度合を示す補正量を演算する補正量演算部42a〜42cと、前記補正量に基づいて、前記一の信号のスルーレートを調整するドライバ41a〜41cと、を備える。

(もっと読む)

駆動装置、及び表示装置

【課題】並列接続された複数の出力アンプ回路において所望の駆動能力を実現することができる駆動装置、及び表示装置を提供すること。

【解決手段】本発明に係る駆動装置(ソースドライバ1)は、並列接続された複数の出力アンプ回路10と、複数の出力アンプ回路10に、バイアス電圧供給源25からバイアス電圧を供給するバイアス配線(幹バイアス配線22)と、複数の出力アンプ回路10に、電源電圧供給源35から電源電圧を供給する電源配線31と、複数の出力アンプ回路10に供給される電源電圧とバイアス電圧との差が所望となるように、バイアス電圧にオフセット電圧を重畳する補正手段(バッファ26)とを備えた。

(もっと読む)

半導体集積回路装置

【課題】超音波診断システム等に用いられる送信ドライバにて、出力トランジスタの製造ばらつきに依存せず、一定の出力波形の傾きを得る半導体集積回路装置を提供する。

【解決手段】出力トランジスタのゲート幅を縮小し模造したレプリカを同一基板上に作成しかつ近接して配置することで両者が同じ製造ばらつきを持つ特徴を利用し、レプリカのオン抵抗が理想値と同じになるゲートソース電圧を、出力トランジスタのゲートソース間に与える電位差にする。

(もっと読む)

負荷駆動装置

【課題】通常動作時におけるスイッチングロスの低減と、過電流保護動作時における出力トランジスタの保護を両立することが可能な負荷駆動装置を提供する。

【解決手段】誘導性負荷Y2に流す出力電流IOUTをオン/オフする負荷駆動部Y10と、出力電流IOUTが過電流状態であるか否かを検出する過電流保護回路Y20と、を有して成り、負荷駆動部Y10は、誘導性負荷Y2の一端に接続される出力トランジスタY11と、入力信号SAに応じて出力トランジスタY11の制御信号SBを生成するプリドライバY12と、を有して成り、プリドライバY12は、通常動作時に出力トランジスタY11をオン/オフする第1駆動部Y121と、過電流保護動作時に第1駆動部Y121よりも緩やかに出力トランジスタY11をオフする第2駆動部Y122と、を有して成る。

(もっと読む)

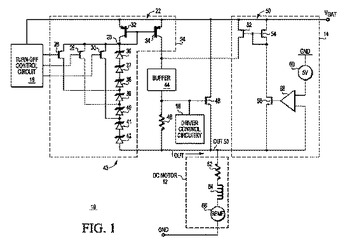

ターンオフ制御を有する電力トランジスタおよびその動作方法

回路が、電力トランジスタ48、駆動制御回路16、可変クランプ回路24、およびターンオフ制御回路18を有する。電力トランジスタが、第1電源端子に接続される第1電流電極、回路の出力50としての第2電流電極、および制御電極を有する。駆動制御回路が、電力トランジスタの制御電極に接続される出力を有して、回路のアクティブモードの間、電力トランジスタを制御する。可変クランプ回路は、回路の出力と第1電源端子との間に接続される。ターンオフ制御回路は、可変クランプ回路に接続され、回路をアクティブモードから非アクティブモードに移行する間、可変クランプ回路のクランプレベルを選択する。  (もっと読む)

(もっと読む)

負荷制御装置

【課題】スイッチ素子の発熱を抑制して小型化を図りつつ、開閉タイミングを正確に制御して、調光制御等の高度な負荷制御を行うことができる負荷制御装置を提供する

【解決手段】操作部28に入力された操作に応じて、制御部13が交流電源の1/2周期のうちトランジスタ構造の主開閉部11を導通させるために計数される主開閉部導通時間を設定し、電圧検出部18が第3電源部16に入力される電圧が所定の閾値に達したときから計数される第1所定時間と、主開閉部導通時間とが重複している時間だけ、主開閉部11を導通させることにより調光制御する。

(もっと読む)

負荷制御装置

【課題】負荷への電力投入時における突入電流による素子の破壊又は劣化を防止しうる負荷制御装置を提供する。

【解決手段】操作スイッチ4から起動信号を受信したときに、制御部13は、第1電源部14への電力を供給する電源が第2電源部15から第3電源部16に切り替わる前に、主開閉部11に対して主スイッチ素子11aを導通させるための初期駆動信号を出力する。

(もっと読む)

サンプリングミキサ回路

【課題】サンプリングパルスの周波数を高めたりデューティ比を特別に絞り込むことなく実効的にデューティ比の小さいサンプリングパルスを得ることができ、従って、高域までの周波数特性に関する要求水準が緩和されたサンプリングミキサ回路を提供する。

【解決手段】サンプリングに適用する各キャパシタC1〜C4の充電経路となる各電流パス113−1,113−2,113−3,113−4を第1スイッチおよび第2スイッチの直列接続回路を含むように構成し、これら各電流パスが所定の各位相差で順次周期的に導通すると共に各電流パス毎の第1および第2スイッチが所定の位相差でオンになる多相のサンプリングパルスを各対応する第1スイッチおよび第2スイッチに供給することによって、各電流パスにおける導通状態の繰り返しに関するデューティ比が上記サンプリングパルスのデューティ比よりも小さくなるようにする。

(もっと読む)

半導体集積回路

【課題】本発明は、中央処理装置の低消費電力モード時に外部から供給されるアナログ信号の正確なAD変換を行うことができる半導体集積回路を提供することを目的とする。

【解決手段】割込み信号のエッジ検出を行ってエッジ検出信号を生成するエッジ検出手段11と、外部から供給されるアナログ信号をエッジ検出信号により保持し、中央処理装置13からの制御により、保持しているアナログ信号をAD変換して中央処理装置に供給するAD変換手段12とを有し、割込み信号又はエッジ検出信号によって中央処理装置が低消費電力モードからクロックを高速とする通常モードとなった後にAD変換手段12に保持しているアナログ信号をAD変換したデジタルデータを中央処理装置13に取り込む。

(もっと読む)

電気機器

【課題】動作条件によって腐食および絶縁低下が発生し、消費電流が増加するLCDモジュールを用いた場合、第1および第2設定スイッチに割り当てられている既存のポートを利用して、消費電流の増加異常を診断する電気機器の提供を目的とする。

【解決手段】液晶表示手段120と内部データを設定する複数の設定手段50、60とを備えた電気機器100において、液晶表示手段120の消費電流の増加を検出し、この検出信号に基づいて複数の設定手段50、60の出力信号を変化させる電流検出手段110と、電流検出手段110によって変化した出力信号に基づいて消費電流の異常を診断する診断手段132と、を備えたことを特徴とするもの。

(もっと読む)

ドライブ回路

【課題】低電圧の制御信号を高電圧の制御信号に変換して出力する高圧用のドライブ回路において、待機時の消費電力を削減することができるようにする。

【解決手段】低圧部1からの制御信号a1〜d1及びa2〜d2により高圧部2のトランジスタMN1〜MN8を駆動し、操作対象3に駆動信号を出力する。その際、低圧部1からの制御信号a1〜d1をそれぞれ論理積ゲートQ1〜Q4の一方の入力端子を介して高圧部2のトランジスタMN1,MN3,MN5,MN7のゲートに入力し、論理積ゲートQ1〜Q4の他方の入力端子には高圧部2のオン/オフ信号を入力する。

(もっと読む)

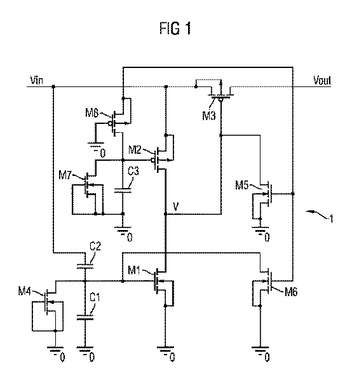

低歪みのプログラマブルゲインアンプ用の動的スイッチドライバ

NチャネルMOSFETMB)及びPチャネルMOSFE(MA)を含む少なくとも1つのスイッチであって、NチャネルMOSFETMB)及びPチャネルMOSFE(MA)の各々は、スイッチのオン/オフ状態を変化させるための駆動信号を受けるように構成されたゲートを有する、少なくとも1つのスイッチと、スイッチのオン/オフ状態を変化させるための1対の駆動信号を選択的に加えるように構成され配置された駆動回路(5DC)であって、(a)スイッチのオン/オフ状態を変化させるのに十分な1対のDC信号成分と、(b)1対の時間変動信号成分(Vonn、Vonp)との関数として、上記駆動信号を発生させるように構成され配置された駆動回路とを備え、前記1対の時間変動信号成分は、各MOSFETのソース端子上に存在する信号の少なくとも部分的な複製としての1対の時間変動信号成分であり、DC信号とともにnチャネルMOSFET及びpチャネルMOSFETのゲートにそれぞれ加えられたときに、上記駆動信号は、スイッチのオン/オフ状態を保持し、各MOSFETのゲート−ソース電圧をMOSFETのゲート−ソース絶縁破壊限界内に維持するように、適切なレベルになる、時間変動入力信号をスイッチするためのスイッチング回路。  (もっと読む)

(もっと読む)

スイッチング駆動回路の短絡保護回路

【課題】誤検出を防止しながら、大電流を流し続けることによる素子の劣化および破損を防止できるスイッチング駆動回路用の短絡保護回路を提供する。

【解決手段】スイッチング駆動回路4の出力側に、短絡状態を検出する短絡検出回路1が接続され、ブランキング回路2により短絡状態がブランキング期間を経過した場合に短絡状態の信号が出力され、その信号に基づいてスイッチング駆動回路4の動作の停止および復帰を制御回路3により制御する。この制御回路3が、停止信号発生回路31および復帰信号発生回路32の他に、第1のブランキング期間より短い時間の第2のブランキング期間を設定するブランキング期間の変更回路33を有しており、さらに、停止および復帰の回数が所定回数(n回)連続して繰り返した場合に、スイッチング駆動回路4の動作を完全に停止させて自動復帰させない非復帰信号発生回路を有している。

(もっと読む)

特に圧電式のマイクロジェネレータを有しているエネルギ自立型のマイクロシステムのためのトリガ回路及び整流器

本発明は、十分に大きい電圧レベルを検出するため、また、十分な出力を供給するためのトリガ回路に関する。更に本発明は、従来の解決手段に比べて、同じ出力電圧で効果的により多くの出力を供給する整流器に関する。トリガ回路及び整流回路は、特に圧電式のマイクロジェネレータを有するエネルギ自立型のマイクロシステムにおいて使用することができる。  (もっと読む)

(もっと読む)

パルス幅変調を有するチャージポンプ回路

電圧調整器のチャージポンプ回路の各スイッチング素子は、並列に接続される比較的大型のMOSトランジスタと関連付けられた、比較的小型のMOSトランジスタを備える。第1の動作モードにおいて、小型のトランジスタのみがスイッチングされ、一方、第2の動作モードにおいて、大型のトランジスタがスイッチングされる。このようにして、第1の動作モードにおけるスイッチング損失を減少させることができる。  (もっと読む)

(もっと読む)

半導体装置、高周波回路、および高周波電力増幅装置

【課題】マルチバンド又はマルチモードに適した半導体装置、高周波回路を提供する。

【解決手段】半導体基板301上に電界効果型トランジスタを形成してなる半導体装置であって、電界効果型トランジスタのソース電極およびドレイン電極としてのオーミック電極501a、501bと、前記オーミック電極501a、501bに挟まれた位置に設けられた、前記電界効果型トランジスタのゲート電極としてのショットキー電極601a、601cと、ショットキー電極601a、601cに挟まれた位置に設けられたショットキー電極601bとを備え、ショットキー電極601bが接地されている。

(もっと読む)

201 - 220 / 754

[ Back to top ]