Fターム[5J055FX33]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 最初に動作する検出回路の素子、回路 (2,393) | ダイオード (316)

Fターム[5J055FX33]の下位に属するFターム

ツェナー、定電圧ダイオード (91)

Fターム[5J055FX33]に分類される特許

1 - 20 / 225

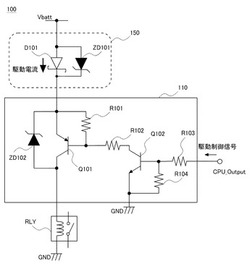

リレー装置

【課題】バッテリ逆接続でのリレー動作防止を実現するとともに、リレー回路の駆動電流経路の電圧降下を抑制する技術を提供する。

【解決手段】リレー装置100では、電源電圧VbattからグランドGNDに向けて、逆流防止回路150、リレー駆動回路110及びリレー回路RLYが直列に配置されている。逆流防止回路150は、ショットキーダイオードD101とツェナーダイオードZD101とを備えている。ショットキーダイオードD101とツェナーダイオードZD101とは並列に接続されており、順方向が同じである。

(もっと読む)

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

半導体スイッチ

【課題】半導体スイッチにおいて、エネルギー効率を高くする。

【解決手段】半導体スイッチ1は、LED2を駆動回路3により駆動して発光させ、LED2から発光された光を受光部4により受光する。駆動回路3は、バイポーラトランジスタ31と、コイル32と、ダイオード33等を有する。バイポーラトランジスタ31は、導通状態と非導通状態とに切換えられ、導通状態のときに、電源からLED2に電流が供給される状態にし、非導通状態のときに、電源からLED2に電流が供給されない状態にする。コイル32は、LED2に直列に接続されており、バイポーラトランジスタ31が導通状態から非導通状態になったときに、自己誘導作用によって誘導起電力を発生する。ダイオード33は、LED2及びコイル32に並列に接続されており、バイポーラトランジスタ31が非導通状態のときに、コイル32が発生する誘導起電力によって、LED2に電流を還流させる。

(もっと読む)

入力装置

【課題】主に自動車内の各種電子機器の操作に用いられる入力装置に関し、誤検出がなく、確実な操作が可能なものを提供することを目的とする。

【解決手段】第一の端子17と第二の端子18の間に複数のダイオード13〜16を直列に接続すると共に、第一の端子17とダイオード13〜16に複数のスイッチ5〜8を接続し、制御手段19がスイッチ5〜8の操作に応じた第一の端子17と第二の端子18からの電圧を減算して、操作されたスイッチを検出することによって、接続された電子機器30が異なる抵抗値の抵抗31や32が設けられた機器に取替えられた場合でも、制御手段19がどのスイッチが操作されたかを、値が一定のダイオードの電圧降下によって検出しているため、誤検出がなく、確実な操作が可能な入力装置を得ることができる。

(もっと読む)

半導体チップ及びこれをパッケージングした半導体装置

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

スイッチ制御装置

【課題】互いにオンオフ状態が反転するように制御すべき2つのスイッチング素子の特性に応じて容易にデッドタイムを調整可能なスイッチ制御装置を提供する。

【解決手段】互いにオンオフ状態が反転するように制御する第1及び第2のスイッチング素子を備えるスイッチ制御装置であって、前記第1及び第2のスイッチング素子の内、一方のスイッチング素子に出力する制御信号をオフレベルに切替えた時点から、コンデンサの容量で設定される設定期間後に他方のスイッチング素子に出力する制御信号をオンレベルに切替える信号を出力する制御信号生成回路を備える。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

電子機器装置

【課題】電子機器装置において、減電圧状態になった場合及び過電圧状態になった場合に、より確実に回路を保護する。

【解決手段】電子機器装置1は、第1の規定電圧値以下の電圧が電子機器装置1に供給される減電圧状態になった場合に、マイコン8をリセットさせ、第2の規定電圧値以上の電圧が電子機器装置1に供給される過電圧状態になった場合に、ヒューズ10を溶断させる減電圧/過電圧検出回路11を備える。減電圧/過電圧検出回路11は、平滑用のコンデンサ4により平滑化された電圧(1次側電圧出力ラインL1から出力された電圧)を監視し、平滑用のコンデンサ4により平滑化された電圧に基いて、減電圧状態、及び過電圧状態を検出する。そして、減電圧/過電圧検出回路11は、過電圧状態を検出した場合には、マイコン8をリセットさせ、過電圧状態を検出した場合には、ヒューズ10を溶断させる。

(もっと読む)

負荷駆動装置

【課題】負荷電流検出手段により検出された負荷電流を用いてリーク故障を確実に検出する。

【解決手段】駆動回路33a、33bの出力端子Ta2、Tb2から電源線6に至る還流経路内にシャント抵抗9a、9bを接続し、電源線5と給電分岐点Nsとの間に共通のシャント抵抗24を接続する。駆動制御回路32は、MOSFET7a、7bをPWM駆動し、負荷電流検出回路12a、12bから負荷電流Ia、Ibを入力し、総電流検出回路23から総電流Isを入力する。検出負荷電流Ia、Ibに対しそれぞれ対応するPWM駆動信号のオフ駆動期間をマスク処理し、マスク処理した検出負荷電流Iam、Ibmを加算した加算電流Icmと検出総電流Isとを比較する。両者が等しい場合には正常状態と判定し、異なる場合にはショート故障またはリーク故障が生じたと判定する。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

リセット回路

【課題】マイコンのリセット端子をトランジスタによってグランドに接続することによりマイコンにリセットをかけるリセット回路において、リセット動作不能な電源電圧の領域を無くす。

【解決手段】リセット回路10は、マイコン11のリセット端子13を電源電圧(以下、VM)にプルアップする抵抗R1と、VMが所定値未満のときにトランジスタT1をオンしてリセット端子13を0Vにするリセット信号出力回路15とに加え、オンすることで抵抗R1の上流側にVMを供給するトランジスタT2と、抵抗R1の上流側とグランドとの間に接続された抵抗R2と、トランジスタT1がオン可能なVMの最低値(Vbe)より高く、上記所定値よりは低い電圧(Vbe+ダイオードD1のVf)を動作閾値電圧とし、VMがその動作閾値電圧未満である場合にトランジスタT2をオフさせておいて、マイコン11のリセットを確保する回路T3,D1,R3,R4とを備える。

(もっと読む)

半導体スイッチ回路

【課題】高いESD保護耐圧を確保しつつ、ESD保護素子の静電容量を極力小さくし、しかも、集積化の際における占有サイズを小さくする。

【解決手段】ESD保護回路103は、共通端子41とグランドとの間に設けられており、共通端子41側から順に、ESD保護スイッチ素子としての複数の直列接続された電界効果トランジスタ31−1〜31−4と、逆接続された一組のESD保護素子としてのダイオード32−1,32−2が直列接続されると共に、電界効果トランジスタ31−1〜31−4は、ゲートが相互に接続されてグランドに接続されており、ESD保護素子のダイオード32−1,32−2による静電容量を低減し、高いESD保護耐圧の確保が可能となっている。

(もっと読む)

トランジスタ駆動回路

【課題】より簡単な構成で、出力トランジスタを確実にオフ状態に維持できるトランジスタ駆動回路を提供する。

【解決手段】NチャネルMOSFET5とコイル2との共通接続点;出力端子OUTとグランドとの間にフライホイールダイオード3を接続する。FET5のゲートには、NPNトランジスタ6及びPNPトランジスタ7のプッシュプル回路により制御信号を出力し、トランジスタ7のベースとグランドとの間にNPNトランジスタ11を接続し、トランジスタ11のベースとグランドとの間にNチャネルMOSFET14を接続して、FET14にPWM信号を入力する。ダイオード13は、FET14がオフ状態になるとトランジスタ11のベースにベース電流を供給し、ダイオード15をダイオード13のアノードとトランジスタ6及び7のベースとの間に接続する。NPNトランジスタ22をFET5のゲートと出力端子との間に接続し、トランジスタ22をPWM信号に応じてFET5がオフする際にオンさせる。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】スイッチ部と、駆動回路と、電源回路と、を備えた半導体スイッチが供給される。前記スイッチ部は、共通端子と複数の高周波端子との接続を切り替える。前記駆動回路は、端子切替信号に基づいて前記スイッチ部に制御信号を出力する。前記電源回路は、温度に応じて変化する基準電位基づいて、前記制御信号の電位であって温度制御された第1の電位を生成して前記駆動回路に出力する。

(もっと読む)

スイッチング素子の駆動装置及びスイッチング素子の駆動方法

【課題】スイッチング損失の増大を抑制しつつ、より高い周波数帯で発生するスイッチングノイズを抑制できるスイッチング素子の駆動装置を提供する。

【解決手段】スルーレート調整部は、NチャネルMOSFETを介してDCモータに出力される電圧波形のスルーレートを変化させ、キャリア周波数によって決まる周波数帯よりも高い周波数帯域に現れるスイッチングノイズの周波数成分を分散させてピークレベルを低下させる。

(もっと読む)

スイッチング回路及び半導体モジュール

【課題】スイッチング制御する制御回路の負担を軽減するスイッチング回路を提供する。

【解決手段】第1のスイッチング素子の制御電極と第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、第2のスイッチング素子の高電位側電極は、第1のスイッチング素子の制御電極に電気的に接続され、第2のスイッチング素子の低電位側電極は第1のスイッチング素子の低電位側電力端子に電気的に接続され、第2のスイッチング素子の制御電極は、抵抗と制御回路の間に接続されている。

(もっと読む)

半導体装置および電子機器

【課題】良好な逆回復特性と良好なEMCとを同時に実現することが出来て、かつ、従来の半導体装置よりも安価である半導体装置及び電子機器を提供する。

【解決手段】半導体装置1は、FET3のソースとMOSFET4のドレインとが接続されるとともに、一端が、FET3のゲートに接続され、他端が、MOSFET4のソースに接続される抵抗Rgsと、アノードが、FET3のゲートに接続され、カソードが、MOSFET4ソースに接続されるダイオードD1とを備える。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

1 - 20 / 225

[ Back to top ]