Fターム[5J055DX09]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 絶緑ゲート型、IGBT (323)

Fターム[5J055DX09]に分類される特許

1 - 20 / 323

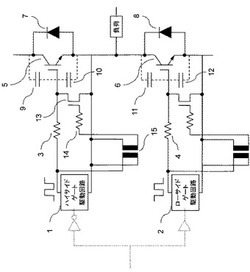

誘導性負荷の駆動回路

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

ゲート駆動回路

【課題】逆導通IGBTに内蔵されたダイオードで発生するリカバリ電流を低減させる。

【解決手段】逆導通IGBTに内蔵されているダイオードに順方向電流が流れている間に、逆導通IGBTのゲート−エミッタ間にゲート閾値電圧よりも低い電圧を印加することで、逆導通IGBTのドリフト領域への正孔の注入を抑制し、リカバリ電流を低減させる。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

半導体装置

【課題】スイッチング素子のターンオン直後における、過電流保護回路の誤動作防止と過電流検出遅れ防止とを両立させる。

【解決手段】半導体装置は、スイッチング素子1のセンス端子に流れるセンス電流を電圧(センス電圧)に変換するセンス抵抗4と、センス電圧が閾値を越えたときにスイッチング素子1の保護動作を行う過電流保護回路3とを備える。過電流保護回路3は、上記閾値を、第1基準電圧VREF1またはそれよりも低い第2基準電圧VREF2に切り替えることができる。過電流保護回路3は、スイッチング素子1が定常状態のときは、上記閾値を第2基準電圧VREF2とし、スイッチング素子1のターンオン直後のミラー期間のときは、上記閾値を第1基準電圧VREF1に設定する。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

ブートストラップ回路、半導体装置

【課題】ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を提供する。

【解決手段】ブートストラップ部用電源供給部10は、抵抗R1からなる回路である。抵抗R1の一方の端子は、P母線と接続している。抵抗R1の他方の端子は、コンデンサC1およびツェナーダイオードD1の並列回路の一端と接続している。コンデンサC1は、充電された電圧をスイッチング素子駆動用回路(HVIC4)に印加する。抵抗R1は、メイン電源母線に一方の端子が接続し、他方の端子がコンデンサC1と接続して、メイン電源母線の電圧をコンデンサC1に印加する。抵抗R1によって、メイン電源側からブートストラップ回路のコンデンサC1を充電することができる。

(もっと読む)

半導体集積回路及びそれを備えた駆動装置

【課題】絶縁素子を介した信号伝達に誤動作を生じさせ得る異常を検出して制御対象に停止信号をすることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、外部から供給される送信データVINに応じた送信信号を生成し出力する送信回路Tx1と、受信信号に基づいて送信データVINを再生する受信回路Rx1と、送信回路Tx1と受信回路Rx1とを絶縁するとともに、送信信号を受信信号として伝達する絶縁素子ISO1と、絶縁素子ISO1を介した信号伝達に誤動作を生じさせ得る異常を検出する異常検出部DT1と、異常検出部DT1により異常が検出された場合には、外部から送信回路Tx1に供給される送信データVINに関わらず停止信号を出力する制御部CT1と、を備える。

(もっと読む)

半導体装置

【課題】フォトカプラの一次側に流れる電流を制限するため抵抗を回路基板上に実装することなく、フォトカプラの一次側に流れる電流を制限できるようにする。

【解決手段】制御IC11a〜11cには、フォトカプラ21a〜21cの一次側に流れる電流を制限する抵抗17a〜17cをそれぞれ内蔵し、トランジスタ16a〜16cがそれぞれ導通した時に流れる電流を抵抗17a〜17cをそれぞれ介して発光素子22a〜22cに導くことにより、フォトカプラ21a〜21cの一次側に流れる電流を制限する。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

半導体装置

【課題】駆動用のスイッチ素子によって出力端子からの出力を制御する半導体装置において、端子に静電気が印加されたときに、スイッチ素子をより確実に保護し得る構成を、装置構成の大型化を抑えて実現する。

【解決手段】半導体装置1は、高電位側電源又は低電位側電源の一方からなる基準部にスイッチ素子の第1端子が接続され、出力端子P1にスイッチ素子の第2端子が接続されている。また、スイッチ素子と並列に第1保護素子が設けられている。また、基準部とは逆側の電源(他方部)と出力端子の間には第2保護素子が接続されている。そして、基準部とは逆側の電源(他方部)側には無効化手段が接続され、出力端子へのサージ電圧の印加によって駆動電圧が発生した場合に、当該駆動電圧の発生後の所定時間、制御入力端子への通電信号の入力を無効化し、所定時間の経過後に無効化を解除するように機能している。

(もっと読む)

半導体スイッチの制御装置

【課題】半導体スイッチ素子に並列に接続される保護回路の異常を検出できる半導体スイッチ素子の制御回路を得る。

【解決手段】半導体スイッチに印加される電圧を抑制するために半導体スイッチに並列に接続された保護回路と、駆動回路の出力ゲート電圧が予め設定された電圧以上あることを検出し、半導体スイッチのオン・オフ状態を判別するゲート電圧検出手段と、半導体スイッチの主端子電圧を検出する主電圧検出手段と、駆動回路に与えられた駆動信号により、駆動指令がオン指令の場合はゲート電圧状態を選択し、駆動指令がオフ指令の場合は主電圧状態を選択する選択手段と、選択手段の出力を絶縁して低圧回路に伝達する第一の信号絶縁手段と、選択手段が選択して出力したゲート電圧状態・主電圧状態と半導体スイッチの駆動指令とを比較し、半導体スイッチの正常又は異常を判別する判別手段とを備える。

(もっと読む)

半導体スイッチ及びスイッチ装置

【課題】電流変動が大きな箇所の半導体スイッチにおいて耐電流と損失を最適化する。

【解決手段】電気的特性及び種類が互いに異なるFET11とIGBT12を並列接続することで半導体スイッチ1aを形成する。端子5及び6間を接続するとき、FET11及びIGBT12は同時にオンされる。端子5及び6間の電流が小電流であるときには、FET11の内部抵抗がIGBT12よりも小さいため、FET11側に優先的に電流が流れて低損失が実現される。端子5及び6間の電流が増大するにつれて、FET11では発熱が内部抵抗増大を招くがIGBT12では内部抵抗が殆ど変化しないため、或る電流値以上では、IGBT12側に優先的に電流が流れる。結果、大電流がFET11側に流れることによるFET11の劣化又は破損が回避される。

(もっと読む)

半導体素子駆動装置及び方法

【課題】並列に駆動される複数の半導体素子の特性差によって生じる、ターンオンやターンオフ時のスイッチングにおける電流の偏りを緩和すること。

【解決手段】電圧変換器14は、IGBT13−1乃至13−3の各々のエミッタセンス電流を電圧信号に変換する。平均値演算器17や誤差演算器18等の演算器は、LPF15から出力される、IGBT13−1乃至13−3の各々に対応する電圧信号の平均値を求め、それぞれの電圧信号についての平均値に対する誤差を演算する。PWM波形生成部11は、IGBT13−1乃至13−3の各々を駆動するための駆動信号(パルス信号)を出力する。差動増幅器12の各々の駆動信号を、当該IGBT13−1乃至13−3の各々に対応する誤差に基づいて調整して、当該IGBT13−1乃至13−3の各々に供給する。

(もっと読む)

ゲート駆動回路

【課題】過電流や短絡発生時に絶縁ゲート型トランジスタへの遮断の遅延を抑制し、安全に絶縁ゲート型トランジスタを保護できるゲート駆動を提供する。

【解決手段】対を成すNPNトランジスタ15、PNPトランジスタ17によるトーテムポール回路9に駆動信号が入力され、回路9の出力が絶縁ゲート型トランジスタ3のゲート3Aに接続され、トランジスタ3のゲート3Aの電位を下げて保護動作をする保護回路11が備えられたゲート駆動回路1であって、トーテムポール回路9のトランジスタ15、17ごとに独立して設けられて駆動信号をベース15A、17Aに入力するベースライン29A、29Bと、保護回路11の保護動作の間、トーテムポール回路9の上アーム側のトランジスタ15のベース電位を下げる電位強制低下回路13と、を備える。

(もっと読む)

電力変換装置

【課題】本発明の課題は、電力変換装置における温度検出素子の時間変化率を検出し、温度上昇の事前予測によりフェールセーフをかけることで、発熱半導体素子の発熱抑制とモジュールケースの冷却構造最適化を実現することである。

【解決手段】上記課題を解決するために、前記半導体素子のモジュールケースまたは素子自体の温度の時間変化率を検出する検出手段と、素子のゲート抵抗値を可変にする抵抗可変回路とを設け、前記検出温度の時間変化率が所定の設定値以上になったと判断されたときは、ゲート抵抗値を前記抵抗可変回路により低減することを特徴とする電力変換装置を提供する。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

スイッチング素子の駆動回路

【課題】パワーデバイス(メインスイッチM)のゲートの印加電圧をバッテリ12の正電圧より高い電圧と負電圧との双方の電圧とする場合、電源装置の小型化が困難なこと。

【解決手段】バッテリ12、端子T3、スイッチング素子SW1、コンデンサC、スイッチング素子SW2、逆流防止用ダイオードD1、端子T1および充電用抵抗体14によって、メインスイッチMのゲート充電経路が構成される。また、放電用抵抗体16、端子T2、逆流防止用ダイオードD2、スイッチング素子SW3、コンデンサC,スイッチング素子SW4、および端子T4によって、メインスイッチMのゲート放電経路が構成される。さらに、端子T3、スイッチング素子SW6、逆流防止用ダイオードD4、コンデンサC、逆流防止用ダイオードD3、スイッチング素子SW5および端子T4によって、コンデンサCの充電経路が構成される。

(もっと読む)

1 - 20 / 323

[ Back to top ]