Fターム[5J056KK00]の内容

論理回路 (30,215) | 図面(フローチャート他) (2,063)

Fターム[5J056KK00]の下位に属するFターム

Fターム[5J056KK00]に分類される特許

1 - 20 / 147

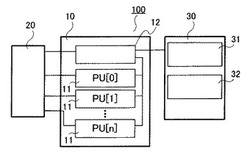

半導体装置及びその動作電源電圧制御方法

【課題】半導体装置及びその動作電源電圧制御方法を提供する。

【解決手段】動作電圧を可変とする複数の処理ユニットと、これら処理ユニットを制御するコントローラを有するLSIと、LSIからの処理ユニット毎に対応した電源供給の要求に応じて電源電圧を処理ユニットに供給する電源制御ユニットと、処理ユニット毎に電源制御ユニットに指示する電源電圧指示値を保持する書き換え可能な不揮発メモリと、を備え、コントローラは、処理ユニット毎に不揮発メモリに保持された電源電圧指示値を取得し、取得した電源電圧指示値を電源制御ユニットに転送する半導体装置。

(もっと読む)

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

半導体集積回路

【課題】不良回路ブロックを特定する時間を短くでき、また、各回路ブロックの信頼性加速試験での特性劣化を精度良く測定できる半導体集積回路を提供することを目的とする。

【解決手段】複数の回路ブロックB1、B2、・・・Bnと、複数の回路ブロックに対応し、回路ブロックと電源端子2との接続を制御する複数のスイッチ回路Sa1、Sa2、・・・Sanと、複数のスイッチ回路に対応し、スイッチ回路へ回路ブロック選択信号を出力する複数のフリップフロップ回路DFF1、DFF2、・・・DFFnとを備え、複数のフリップフロップ回路は、シフトレジスタ回路を構成し、外部信号の入力に基づいて、2以上のスイッチ回路を選択して回路ブロック選択信号を出力し、当該回路ブロック選択信号を入力された2以上のスイッチ回路は、当該2以上のスイッチ回路それぞれに対応する回路ブロックと電源端子とを接続する半導体集積回路100。

(もっと読む)

出力回路及びそのドライブ能力テスト方法。

【課題】容量性負荷が外部端子に接続されている場合でも、出力バッファのドライブ能力の診断が可能な出力回路とテスト方法を提供する。

【解決手段】外部負荷が接続される第1、第2の外部端子と、前記第1、第2の外部端子に接続される前記外部負荷を駆動する出力バッファ部と、第1の制御信号に応じてオン状態となることで、前記第1、第2の外部端子を導通させるスイッチ部と、テスト時において、前記出力バッファ部により、前記第1、第2の外部端子に対して互いに逆相の信号を出力させ、且つ、前記第1の制御信号により前記スイッチ回路をオン状態とするテスト制御部と、を有する出力回路。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】スタンバイ状態への設定と解除が頻繁に繰り返されることにより、消費電力が増大することを避けることのできる半導体装置を提供する。

【解決手段】内部回路50と、第1制御信号を受けて内部回路への電源供給を制御する電源制御回路40と、第2制御信号を受けて第1制御信号を出力する制御信号発生回路30と、を備え、制御信号発生回路30は、第2制御信号の非活性期間が第1の期間未満であるときに第1制御信号を非活性状態とせず、第1の期間以上であるときに第1制御信号を非活性状態とする。

(もっと読む)

二段電圧レベルシフト

【課題】追加の大きなハードウェア要件なしに、ブースト電圧レベルを提供できるようにする。

【解決手段】第1の電圧レベルから第2の電圧レベルに、次に追加のブーストされた第2の電圧レベルに出力信号をシフトするための電圧レベルシフタが開示される。電圧レベルシフタは、入力信号を受信するための入力、出力信号を出力するための出力、前記第1の電圧レベルを供給する第1の電圧源に接続するための第1のパワーサプライ入力、前記第2の電圧レベルを供給する第2の電圧源に接続するための第2のパワーサプライ入力、前記ブーストされた第2の電圧レベルを供給する第3の電圧源に接続するための第3のパワーサプライ入力を含み、前記電圧レベルシフタは、前記出力から前記第1のパワーサプライ入力を隔離するため、及び前記出力に前記第2のパワーサプライ入力を接続するために前記入力信号の所定の変化に応える。

(もっと読む)

回路シミュレーション装置、回路シミュレーション方法及びプログラム

【課題】位相同期回路を含む回路シミュレーションにおいて、フィードバックループに分周器が存在している場合であっても正確にシミュレートできるようにすること。

【解決手段】フィードバックループに設けられた分周器の分周比を測定するための第1のクロック信号を生成する測定クロック生成部と、分周器が第1のクロック信号を受信して分周して出力した第2のクロック信号と、第1のクロック信号とを参照して、分周器の分周比を測定する分周比測定部と、入力クロック信号を受信し、入力クロック信号の周期と予め設定された逓倍比と測定された分周比の逆数に相当する逓倍比とに応じて、入力クロック信号を逓倍して第3のクロック信号として出力する逓倍クロック生成部と、第1のクロック信号及び第3のクロック信号を受信し、いずれかを出力クロック信号として出力するクロック出力制御部とを有する。

(もっと読む)

半導体集積回路

【課題】より信頼性の高い半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、入力信号DINを記憶保持する複数のフリップフロップF1と、複数のフリップフロップF1からの出力の多数決結果MJを出力する多数決回路7と、複数のフリップフロップF1の出力不一致を検出し、エラー信号を出力するエラー検出回路2と、エラー検出回路2からのエラー信号を監視する監視回路3と、を備え、監視回路3は、エラー検出回路2からのエラー信号をもとに、複数のフリップフロップF1のうち、出力不一致が発生しているフリップフロップF1に対して書き戻しを行うリフレッシュ動作を指示するとともに、リフレッシュ動作により書き戻らなかった場合には外部に通知を行うものである。

(もっと読む)

半導体集積回路及びその制御方法

【課題】従来技術の半導体集積回路では、電源遮断領域において発生する電圧降下等を抑制することができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、高電位側電源ライン14及び低電位側電源ライン15と、部分電源ライン13a,13bと、高電位側電源ライン14と部分電源ライン13aとの間に設けられた電源スイッチSWA1〜SWAmと、部分電源ライン13aと低電位側電源ライン15との間に設けられた内部回路12aと、高電位側電源ライン14と部分電源ライン13bとの間に設けられた電源スイッチSWB1〜SWBnと、部分電源ライン13bと低電位側電源ライン15との間に設けられた内部回路12bと、部分電源ライン13a,13b間に設けられ、電源スイッチSWA1〜SWAm,SWB1〜SWBnがオンの場合にオンに制御される電源スイッチSWX1〜SWXpと、を備える。

(もっと読む)

インターフェイス回路、LSI、サーバ装置、およびインターフェイス回路のトレーニング方法

【課題】 波形整形のための信号処理機能を有するインターフェイス回路において、波形整形のために付加される回路の影響で、消費電力が大きくなってしまう。また、システム内では複数の基板がバックプレーンに接続されるため、距離が近いものから遠いものまでが混在することになるが、距離に応じて基板を換えるわけではなく、共通の基板を用いるため、インターフェイス回路は最も遠い場合に対応する構成で準備する必要がある。すなわち、最も距離が長いものに対応した波形整形回路を準備し、それらを伝送距離が短い場所でも使用することになり、全体の消費電力が増大するという問題が生じる。

【解決手段】 本発明のインターフェイス回路は、波形整形回路の一部または全ての動作を停止させる。これにより、伝送距離に応じて、インターフェイス回路内の波形整形回路の動作範囲の切りかえを可能とし、波形整形回路の中の動作範囲を制限することができ、インターフェイス回路、インターフェイス回路を含むLSIやサーバ装置の消費電力を低減できる。

(もっと読む)

半導体集積回路の設計方法及びプログラム

【課題】タイミング制約を満たすためにセルの物理的な位置やRTL(Register Transfer Level)を変更する必要がなく、回路の最適化を短時間に行うことができ、半導体集積回路の設計期間を短縮することができる半導体集積回路の設計方法、設計プログラムを提供する。

【解決手段】半導体集積回路のネットリストに対して静的タイミング解析を行うことにより、所定のタイミング制約を満たさないタイミングエラーパスを検出し、前記タイミングエラーパスを含む第1の論理ブロックと、フリップフロップを介して前記第1の論理ブロックに接続され、所定のタイミング制約を満たす第2の論理ブロックとを抽出し、前記第1の論理ブロックと前記第2の論理ブロックとの間のフリップフロップが正相/逆相フリップフロップである場合は、当該正相/逆相フリップフロップを逆相/正相フリップフロップに変更する。

(もっと読む)

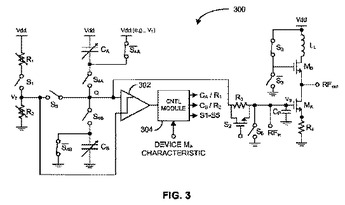

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

集積回路装置及び電子機器

【課題】通常動作モード、低消費電力動作モードでの省電力化等を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第1の電源電圧VDDAを出力する第1のレギュレーターRG1と、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第2の電源電圧VDDBを出力する第2のレギュレーターRG2と、第1の電源電圧VDDAが供給され、通常動作モード及び低消費電力動作モードにおいて動作する第1のロジック回路LG1と、第2の電源電圧VDDBが供給され、通常動作モードにおいて動作し、低消費電力動作モードでは非動作になる第2のロジック回路LG2を含む。

(もっと読む)

半導体装置

【課題】開発の早期において、様々な条件におけるクロストーク耐性を確認することができる半導体装置を提供する。

【解決手段】信号発生回路3と、遅延回路40、41、42、43、…、4mと、遅延回路50、51、52、53、…、5mと、出力バッファ70、71、72、73、…、7mそれぞれに対応して設けられ、遅延回路40、41、42、43、…、4mから出力された信号または遅延回路50、51、52、53、…、5mから出力された信号のいずれかを選択して対応する出力バッファ70、71、72、73、…、7mに出力する選択回路60、61、62、63、…、6mと、を備える。

(もっと読む)

半導体集積回路

【課題】デジタル回路とアナログ回路とを混載して成る半導体集積回路において、前記デジタル回路によってメモリなどの外部負荷を駆動するにあたって、グランドバウンスによるアナログ回路への影響を抑えつつ、前記外部負荷がデジタル回路からの矩形波パルスを受信するにあたって、ON/OFF(「1」/「0」)判定のマージンを最大にする。

【解決手段】外部負荷3を駆動するメインドライバ回路7を、複数段のインバータINV1〜INV3を備える多段階電圧制御型のプリドライバ回路6を介して駆動するようにし、そのインバータINV1〜INV3の使用段数を切換え回路12で切換えられるようにする。そして、雑音検出回路13によって検出されるグランドバウンスのレベルが、小さいときにはインバータINV3のみを使用して前記矩形波パルスの鈍りを小さくし、大きいときにはインバータINV1〜INV3を使用して、グランドバウンスを抑える。

(もっと読む)

検知システム並びにそれを用いた半導体装置および情報処理装置

【課題】 低電力モードを有するLSIにおいて、低電力モードで電力が低減されていない場合にも、LSIを搭載する機器が性能劣化等に至るのを防止することが可能なLSIを提供する。

【解決手段】 動作モードを指示し、そのモードの通りに動作しているかを検出する回路であって、低電力モード時の電流を擬似的に測定し、低電力モードに移行したにもかかわらず実際には電流が低減されていない場合に警告信号を発する。

(もっと読む)

伝送装置

【課題】従来は、ヒータの制御を主制御部が行うようにしていたため、低温起動時において、装置内が所定の温度以上に加熱され装置動作に入る前の段階で、装置全体に電力を供給することになり、消費電力が多くなるという課題があった。

【解決手段】伝送装置を、主制御部と、消費電力が主制御部よりも小さい副制御部と、伝送装置外部との間で信号を送受信するインタフェース部と、該インタフェース部で受信した信号を増幅する増幅部と、伝送装置内を所定の温度に加熱する加熱部と、伝送装置内の温度を検出する温度検出部とから構成し、伝送装置の起動時において、まず副制御部が起動され、副制御部が増幅部への電力供給を行うとともに、温度検出部により伝送装置内の温度を検出し、伝送装置内が所定の温度以上である場合は、主制御部の起動を行い、伝送装置内が所定の温度未満である場合は、加熱部を加熱制御し、伝送装置内が所定の温度以上になると主制御部の起動を行うようにする。

(もっと読む)

1 - 20 / 147

[ Back to top ]