Fターム[5J056KK03]の内容

論理回路 (30,215) | 図面(フローチャート他) (2,063) | 特性図 (395)

Fターム[5J056KK03]に分類される特許

1 - 20 / 395

レベルシフト回路

【課題】レベルシフト回路を高速動作する。

【解決手段】一つの実施形態によれば、レベルシフト回路は、第一のトランジスタ、第二のトランジスタ、第一のコンデンサ、及び第二のコンデンサが設けられる。第一のトランジスタは、制御端子に入力電圧が入力される。第二のトランジスタは、制御端子に入力電圧の反転信号が入力される。第一のコンデンサは、一端が第一のトランジスタの第一の端子に接続され、他端に入力電圧の反転信号が入力され、入力電圧の立ち上りのときに電荷を蓄積して第一のトランジスタの第一の端子側から一端側へ第一の電流を発生する。第二のコンデンサは、一端が第二のトランジスタの第一の端子に接続され、他端に入力電圧が入力され、入力電圧の立ち下りのときに電荷を蓄積して第二のトランジスタの第一の端子側から一端側へ第二の電流を発生する。

(もっと読む)

レベルシフター回路、集積回路装置、電子時計

【課題】 出力信号にスパイクノイズが乗ることや、応答速度が遅くなることを防止するレベルシフター回路を提供する。

【解決手段】 第1の高電位と第1の低電位とを電源電位とする第1の電位系の入力信号Aを受け取り、第1の電位系の信号である第1の信号XAを出力する第1の回路10と、第2の高電位と第2の低電位とを電源電位とする第2の電位系の、入力信号に応じた出力信号Yを生成する第2の回路20と、入力信号を受け取り、第1の電位系の信号であって入力信号と論理的に等価な第2の信号Bを生成するバッファー回路と、を含み、第2の回路は、第2の信号を受け取り、第3の信号XDを出力する初段インバーターと、第1の信号に基づいて、初段インバーターと第2の高電位を供給する電源又は第2の低電位を供給する電源との接続、切断を切り換える初段スイッチと、を含み、第3の信号に基づいて出力信号を生成する。

(もっと読む)

半導体装置

【課題】容量を充放電させ信号を遅延させる回路の遅延時間の温度依存性を緩和し回路規模の増大を抑制可能とした半導体装置の提供。

【解決手段】互いに異なる電源電圧を与える第1の電源(VDD)と第2の電源(VSS)の間に直列に接続され、制御電極が共通に接続された第1及び第2のFET(M11、M12)と、前記第1及び第2のFETの間に接続する第1の回路を有するインバータを備え、前記第1の回路は、互いに並列に接続された第1の抵抗素子(R12)と第3のFET(M13)を備え、前記第1の抵抗素子(R12)の抵抗値は正の温度特性を有し、前記第3のFET(M13)は、その動作範囲に、第3のFET(M13)の端子間抵抗が、第1の抵抗素子(R12)の温度特性と逆極性の負の温度特性を示す領域を含む。

(もっと読む)

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、高電源電位が入力される入力端子とグランド端子との間に接続された抵抗と、抵抗中の第1ノードに接続された第2ノードと、第2ノードと第3ノードとの間に接続されたインバータと、抵抗を通した入力端子とグランド端子との間の電気的接続をON/OFF制御するスイッチと、を備える。ターゲット反転電位は、インバータの反転電位よりも高い。入力端子の電位がターゲット反転電位の場合、第2ノードの電位がその反転電位となる。第2ノードの電位が反転電位より低い場合、インバータは低電源電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をONする。一方、第2ノードの電位が反転電位より高い場合、インバータはグランド電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をOFFする。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

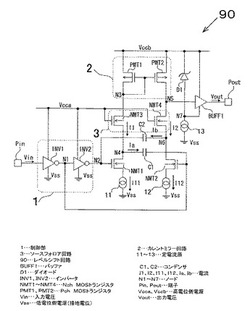

信号出力回路

【課題】広いダイナミックレンジと良好な周波数特性を得ることができる信号出力回路を提供する。

【解決手段】実施形態の信号出力回路は、ゲート端子へ一定の電圧Vgが印加され、ソース端子へ入力信号INが印加されるゲート接地型のNMOSトランジスタ1と、ゲート端子がNMOSトランジスタ1のドレイン端子に接続され、ソース端子から出力信号OUTが出力されるソースフォロワであるNMOSトランジスタ2とを備える。この信号出力回路は、バックゲートバイアス生成部3が、NMOSトランジスタ1およびNMOSトランジスタ2のバックゲート端子へ印加する共通のバックゲートバイアス電圧Vbを生成する。

(もっと読む)

低いデューティサイクル歪みを有するレベルシフタ

【課題】低いデューティサイクル歪み及び高い電源電圧マージンの高速レベルシフティング回路を提供する。

【解決手段】レベルシフタ100は、反転回路104と、クロス接続されたレベルシフティングラッチ102と、SRロジックゲートラッチ103とを含み、レベルシフティングラッチ102の第1、第2出力は、SRロジックゲートラッチ103のセット(S)入力ノード121およびリセット(R)入力ノード120に接続され、反転回路104は、レベルシフティングラッチ102の第1入力ノード112に非反転の信号を供給すると共に、第2入力ノード113に反転の信号を供給し、入力信号のロウからハイへの変化はSRロジックゲートラッチ103をリセットし、ハイからロウへの変化はSRロジックゲートラッチ103をセットするように構成されている。

(もっと読む)

半導体装置

【課題】信号伝送のより高速化を図る。

【解決手段】入力信号Vinと基準信号Vrefとを入力する第1の差動対(Q3、Q4が相当)と、第1の差動対のそれぞれ負荷となる第1及び第2のトランジスタQ2、Q1と、を含む第1の入力回路を備え、第1の入力回路の出力側となる第1のトランジスタQ2は、第2のトランジスタQ1に比べてゲート幅を長くする。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】トランシーバ回路30等の通信回路に接続される通信線10を構成するHライン通信線10H,Lライン通信線10L間にリンギング抑制回路1が設けられる。リンギング抑制回路1において、バイポーラトランジスタT1のエミッタはHライン通信線10Hに接続され、コレクタはLライン通信線10Lに接続され、ベースはコンデンサC1の一方電極及び抵抗R1の一端に接続され、コンデンサC1の他方電極はLライン通信線10Lに接続され、抵抗R1の他端はHライン通信線10Hに接続される。

(もっと読む)

CMOS論理回路

【課題】貫通電流を抑制しつつ、ドライブ能力を向上することが可能なCMOS論理回路を提供する。

【解決手段】CMOS論理回路は、第1の電圧線に一端が接続され、印加される電圧に対して非線形となるインピーダンス特性を有する抵抗性素子と、第1、第2のMOSトランジスタで構成される第1のインバータ回路を備える。CMOS論理回路は、第3、第4のMOSトランジスタからなる第2のインバータ回路を備える。CMOS論理回路は、抵抗性素子と並列に接続され、ゲートが第3のMOSトランジスタP2の他端に接続された第5のMOSトランジスタを備える。CMOS論理回路は、第1の電圧線と第1の出力端子との間に接続され、ゲートが第3のMOSトランジスタの他端に接続された第6のMOSトランジスタを備える。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

ニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器

【課題】回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器を提供すること。

【解決手段】本発明の一実施形態によると、第1のCMOS回路と、共通するローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに並列に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを共振により出力する電圧出力回路100と、電圧出力回路100の発振を制御する発振制御回路210とを含む。発振制御回路210は、第1の電源電圧VPが出力されるノード及び第2の電源電圧VMが出力されるノードのいずれか一方のノードである第1のノードN1に接続される駆動回路220と、駆動回路220を制御する制御回路230とを含む。発振制御回路210は、制御信号SCに基づいて、第1、第2の電源電圧VP、VMの振幅を可変に制御する発振制御を行う。

(もっと読む)

出力回路

【課題】差動出力電圧の振幅のばらつきを抑制した出力回路を提供する。

【解決手段】出力回路は,定電圧ノードと基準電源との間に,複数のスイッチ素子のオン,オフにより合成抵抗値が可変制御可能な複数の抵抗を有し,定電圧ノードに第1の電流を生成する定電流生成回路と,第1の電流をカレントミラーにより生成した第2の電流を,内部回路から供給される内部差動信号に応じて,出力端子対に出力する出力駆動回路と,出力端子対の出力差動電圧の差が所望の電圧差と一致するように,定電流生成回路の複数のスイッチ素子を制御するスイッチ素子制御信号を生成する出力振幅調整部とを有する。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

1 - 20 / 395

[ Back to top ]