Fターム[5J056KK03]の内容

論理回路 (30,215) | 図面(フローチャート他) (2,063) | 特性図 (395)

Fターム[5J056KK03]に分類される特許

121 - 140 / 395

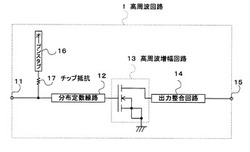

高周波回路の設計方法、高周波回路

【課題】少数の部品で高周波回路の安定性を向上させる。

【解決手段】電子回路と、該電子回路に並列に接続されたスタブと、該電子回路に並列に接続された抵抗と、を有する高周波回路において、該抵抗を分布定数回路である等価回路に置き換え、該高周波回路で用いられる第1の周波数で前記高周波回路のインピーダンスマッチングがとれており、且つ前記高周波回路が安定すべき第2の周波数で前記高周波回路が安定するように、前記スタブのインピーダンス値と、前記等価回路の抵抗値とを設定する。

(もっと読む)

半導体集積回路装置及び電源システム

【課題】パワースイッチをオンとする際に発生する電源ノイズが許容値を超えないようにし、かつ、内部回路に与える電源電圧の立ち上がり時間を短縮することができるようにした半導体集積回路装置を提供する。

【解決手段】信号処理回路15に対する電源投入時に、パワースイッチをなすNMOSトランジスタ21−1〜21−4、22−1〜22−4のうち、まず、NMOSトランジスタ21−1〜21−4をオンとする。その後、信号処理回路15が出力端子20−1に出力する出力信号OUTの電圧変化を検出し、電源ノイズがピーク値に達したことが検出されると、NMOSトランジスタ22−1〜22−4をオンとする。

(もっと読む)

半導体集積回路およびその動作方法

【課題】低高のしきい値電圧のトランジスタが混在する半導体集積回路で、電源電圧VDDの制御で速度制御を実行する際に各トランジスタの動作速度を適切に制御する。

【解決手段】半導体集積回路は、内部回路13、測定回路14、15、16を具備する。内部回路は低高のしきい値電圧のMOSトランジスタを含み、低しきい値電圧のトランジスタのばらつきは高しきい値電圧のトランジスタのばらつきより大きい。測定回路は低高のしきい値電圧のトランジスタが、ともに、高速の状態Fast、典型の状態Typical、低速の状態Slowのいずれかを検出する。高速の検出結果で小さな変化勾配β[V/σ]の低いレベルVDD−ΔVDDに、典型の検出結果で中間的なレベルVDD±0に、低速の検出結果で大きな変化勾配α[V/σ]の高いレベルVDD+ΔVDDに、電源電圧VDDが設定される。

(もっと読む)

電子回路

【課題】 充電回路の動作を安定化させる。

【解決手段】 充電回路(100)は、第1出力信号を出力するTr制御回路(24)と、第1出力信号が入力されて動作するトランジスタ(Tr)及びコンデンサ(C1)と、その状態を検出し、その結果としての第2出力信号を出力するコンパレータ(21)と、第2出力信号に基づいて、Tr制御回路をして前記第1出力信号を出力させるかどうかを決定する第3出力信号をTr制御回路に供給するフリップフロップ(24)と、を備え、フリップフロップの入出力特性の遷移帯は、Tr制御回路の入出力特性の遷移帯と重ならない。

(もっと読む)

終端抵抗調整回路

【課題】入力差動信号のコモン電圧が変化しても、終端抵抗を一定に保持でき、かつ、簡易な回路構成の終端抵抗調整回路。

【解決手段】抵抗値を調整可能な第1の終端抵抗回路と、第1の終端抵抗回路と並列に接続され、抵抗値を調整可能な第2の終端抵抗回路と、第1及び第2の終端抵抗回路の抵抗値を調整するための調整用抵抗回路と、調整用抵抗回路により定まる第1の電圧と、外部に接続された基準抵抗により定まる第2の電圧とが入力され、両電圧が等しくなるように動作するとともに、第1及び第2の終端抵抗回路に対し抵抗調整信号を出力する第1の増幅回路と、第1の終端抵抗回路が接続された第1の端子と、第2の終端抵抗回路が接続された第2の端子と、第1及び第2の端子に与えられる差動信号のコモン電圧に基づく電圧と、第1又は第2の電圧とが入力され、両電圧が等しくなるように動作する第2の増幅回路と、を備える終端抵抗調整回路。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の動作速度を向上し、アクティブ時の消費電力、スタンバイ時の消費電力を共に低減し、チップ面積を小さくする。

【解決手段】半導体集積回路は、クロックにより制御される第1、第2、第3フリップフロップ回路、第1論理回路段及び第1論理回路段より段数の少ない第2論理回路段を有する。第1電位を有する第1電位組を動作電源とする第1論理ゲートと第1電位より小さい第2電位を有する第2電位組を動作電源とする第2論理ゲートを含む。第1論理ゲートを構成する第1MISトランジスタはウエル領域に第1電位組の何れかの電位が与えられる。第2論理ゲートを構成する第2MISトランジスタはウエル領域に第1電位組の何れかの電位が与えられる。第2論理回路段は、第1論理回路段より第2論理ゲートの数が多い。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路は、クロスオーバー電圧の変動幅が増大するという問題があった。

【解決手段】本発明にかかる半導体集積回路は、差動入力の一方に基づいて第1及び第2の信号を生成するプリドライバ4cと、差動入力の他方に基づいて第3及び第4の信号を生成するプリドライバ回路4dと、VDDとVSSとの間に設けられ、第1の信号に基づいて制御されるMN4と、第2の信号に基づいて制御されるMP4と、からなる出力回路5aと、VDDとVSSとの間に設けられ、第3の信号に基づいて制御されるMN8と、第4の信号に基づいて制御されるMP8と、からなる出力回路5bと、VDDに応じた第1の制御信号を生成する制御信号生成回路6と、を備える。さらに、プリドライバ4cは、第1の制御信号に基づいて第1の信号を制御し、第2のプリドライバ4dは、第1の制御信号に基づいて第3の信号を制御する。

(もっと読む)

レベルシフタ、集積回路、システム、およびレベルシフタの動作方法

【課題】 レベルシフタ、集積回路、システムおよびレベルシフタの動作方法を提供する。

【解決手段】 第1電圧状態から第2電圧状態への第1状態遷移を含む入力電圧信号を受けるように構成された入力端、第3電圧状態から入力電圧信号の第1状態遷移に対応した第2電圧状態への第2状態遷移を有する出力電圧信号を出力するように構成された出力端、及び入力端と出力端の間に結合され、第1トランジスタと第2トランジスタを含み、第1電圧状態と第2電圧状態の電圧レベルの約平均値に対応した時間からほぼ直ちに、第2電圧状態がトランジスタのゲートに実質的に印加されることがなくなり、第1トランジスタを実質的にオフにするドライバ段を含むレベルシフタ。

(もっと読む)

半導体装置

【課題】オフリーク電流の温度特性が互いに異なる複数の回路ブロックに対して電源制御を行うことにより、消費電力を低減する。

【解決手段】オフリーク電流が第1の温度特性を有するトランジスタによって構成された第1のXデコーダ12と、オフリーク電流が第2の温度特性を有するトランジスタによって構成されたプリデコーダ13及び周辺回路14と、スタンバイ時において温度が第1のしきい値を超えている場合、Xデコーダ12を非活性化させる電源制御回路16と、スタンバイ時において温度が第2のしきい値を超えている場合、プリデコーダ13及び周辺回路14を非活性化させる電源制御回路17とを備える。本発明によれば、複数の回路ブロックに対する電源制御の有無を、互いに異なる温度を基準として判断していることから、各回路ブロックに対して最適な電源制御を行うことが可能となる。

(もっと読む)

半導体装置

【課題】出力バッファの出力電流が一定の範囲内に収まるように制御できる半導体装置を提供する。

【解決手段】出力バッファ1と、出力バッファと直列に接続された電流制御トランジスタM0と、電流制御トランジスタを介して出力される出力電流をモニタして電流制御トランジスタのオン抵抗を制御する出力電流制御回路2と、を備える。温度や電源電圧の変動等により出力バッファ自体のオン抵抗が変動したとしても、出力バッファの出力電流は、電流制御トランジスタにより決まり、電流制御トランジスタに流れる電流は出力電流制御回路によって一定の範囲内に収まるように制御される。出力バッファ自体の高速なスイッチング動作が損なわれることもない。

(もっと読む)

半導体装置

【課題】相補電界効果トランジスタのオフ電流の周囲温度の変動に伴う変動を抑制する。

【解決手段】CMOSを構成するNチャンネルMOSトランジスタの基板電圧VPWを生成する基板電圧生成回路31と、上記NチャンネルMOSトランジスタのレプリカであり、かつダイオード接続されたレプリカトランジスタ32と、レプリカトランジスタ32のアノード−カソード間に所定の電圧値VFの電圧を印加する電圧印加部33とを備え、レプリカトランジスタ32の基板電圧は基板電圧生成回路31が生成する基板電圧VPWであり、基板電圧生成回路31は、レプリカトランジスタ32に流れる電流の電流値が所与の目標値となるよう、生成する基板電圧VPWを制御する。

(もっと読む)

半導体集積回路、半導体集積回路の駆動方法、表示装置および電子機器

【課題】高耐圧化可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、電源電位と接続された出力ノードと、出力ノードと電源電位より低電位である接地電位との間に直列に接続された第1のnチャネル型トランジスター、第2のnチャネル型トランジスターおよび第3のnチャネル型トランジスターを有し、第1のnチャネル型トランジスターの一端は、接地電位に接続され、他端は、第2のnチャネル型トランジスターの一端に接続され、ゲート端子は、入力ノードに接続され、第2のnチャネル型トランジスターの他端は、第3のnチャネル型トランジスターに接続され、ゲート端子は、電源電位と接地電位との間に位置する第1中間電位に接続され、第3のnチャネル型トランジスターの他端は出力ノードに接続され、ゲート端子は電源電位に接続されている。

(もっと読む)

高周波スイッチ及び受信回路

【課題】簡単な構成でセルフミキシング信号の発生を低減する高周波スイッチ及びこれを用いた受信回路を提供する。

【解決手段】ゲート端子が入力端子側に接続され、ドレイン端子が出力端子側に接続され、ソースが接地された電界効果トランジスタと、前記電界効果トランジスタのゲート端子側に接続されるゲートバイアス電圧調整手段とドレイン端子側に接続されるドレインバイアス電圧調整手段の少なくともいずれか一方を備え、前記ゲート端子と入力端子との間及び前記ドレイン端子と出力端子との間の少なくともいずれか一方に整合回路を備え、導通状態における反射特性と前記遮断状態における反射特性とが略等しくなるように、スイッチを構成している。

(もっと読む)

バッファ回路

【課題】低電圧と高電圧とを相反する論理信号として出力し、前記高電圧として、異なる2以上の電圧を出力可能であって、安定して動作するバッファ回路。

【解決手段】論理制御回路と、第1の高電圧VDDLを与える電源と出力端子との間に設けられ、ゲートに前記論理制御回路から出力された第1の高電圧VDDLレベルの制御信号が入力され、バックゲートに第1の高電圧VDDLが与えられた第1のMOSトランジスタM9と、第2の高電圧VDDHを与える電源と出力端子との間に設けられ、ゲートに論理制御回路から出力された第2の高電圧VDDHレベルの制御信号が入力され、バックゲートに第2の高電圧VDDLが与えられた第2のMOSトランジスタM11と、第1のMOSトランジスタM9と出力端子との間に設けられ、第2の高電圧VDDLレベルの制御信号によりオンオフが制御される第1のスイッチ回路SW1と、を備えるバッファ回路。

(もっと読む)

入力回路および半導体集積回路

【課題】電磁波による誤動作を低減することのできる入力回路および半導体集積回路の提供を図る。

【解決手段】入力端子2に供給される入力信号を受け取る入力回路10aであって、一端が前記入力端子に接続された容量42と、前記入力信号を、当該入力信号と同じ正論理の信号に変換し、前記容量の他端に供給して駆動する容量駆動回路51,52,41と、を有するように構成する。

(もっと読む)

レベルシフト回路、スイッチング素子駆動回路及びインバータ装置

【課題】レベルシフト回路の電圧変動等に起因するコモンモードノイズ発生時でもクランプすることなく、信号を伝達できるレベルシフト回路、スイッチング素子駆動回路及びインバータ装置を提供する。

【解決手段】セットパルス及びリセットパルスを発生するパルス発生回路と、セットパルスを電流に変換する第1スイッチング素子及びリセットパルスを電流に変換する第2スイッチング素子と、浮動電位側にあり、第1スイッチング素子で電流に変換された信号を電圧に変換するセット用負荷及び第2スイッチング素子で電流に変換された信号を電圧に変換するリセット用負荷と、セット用負荷の信号レベルおよびリセット用負荷の信号レベルから、制御パルス信号を再生するパルス再生回路を備えるレベルシフト回路において、セット用負荷及びリセット用負荷として非線形の負荷特性を有する回路を用いる。

(もっと読む)

半導体集積回路

【課題】差動アンプ回路の出力信号の出力をより正確に制御することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第4のMOSトランジスタと第5のMOSトランジスタとの間の接点の第1の電圧に応じた信号とイネーブル信号とが入力され、イネーブル信号が第1のレベルであり且つ第1の電圧が規定電圧以上の場合に差動アンプ回路の出力信号を出力端子に出力するための第1の信号を出力し、イネーブル信号が第2のレベルまたは第1の電圧が規定電圧未満の場合に第2の信号を出力する演算回路と、差動アンプ回路の出力信号と演算回路が出力した信号とが入力され、第1の信号が入力された場合には、出力信号を出力端子に出力し、第2の信号が入力された場合には、出力端子へ或る論理に固定した信号を出力する出力バッファ回路と、を備える。

(もっと読む)

CMOSインバータ回路

【課題】低電圧CMOSインバータ回路における製造プロセスバラツキや温度バラツキの影響をオンチップで検知して、製造プロセスバラツキや温度バラツキの影響をキャンセル補正し、論理反転閾値のバラツキを大幅に抑制する低電圧CMOSインバータ回路を提供する。

【解決手段】pMOSFETの論理反転閾値とnMOSFETの論理反転閾値のプロセスバラツキによる変動の差電圧を、そのまま出力電圧変動とする閾値電圧差バラツキモニタ回路を備え、前記閾値電圧差バラツキモニタ回路の出力電圧をCMOSインバータの電源ラインに供給する。また、CMOSインバータ回路における出力電圧の後段に、さらに論理値レベル補正部が設けられ、電源電圧の変動を抑制する。

(もっと読む)

レシーバ回路

【課題】簡易な回路構成であり、かつ、レールツーレール入力の小振幅差動信号を受信して、低消費電力、低ゆがみ、高速に増幅出力することができ、電圧が異なる複数の電源が存在する系においても使用することができるレシーバ回路を提供する。

【解決手段】NMOS/PMOSの差動回路を有し、それぞれの差動回路により、レールツーレールの小振幅差動入力信号を受け取ってIO系電源のレールツーレールの差動出力信号を生成する差動増幅回路と、差動出力信号の同相入力電圧レベルに応じて、差動回路のテールカレントを補償する電流補償ミラー回路と、差動増幅回路によって生成されたIO系電源のレールツーレールの差動出力信号を、コア系電源のレールツーレールの差動信号にレベルシフトして出力するレベルシフタとを備えている。

(もっと読む)

混成信号回路のデジタル式プログラム可能な最適化のための方法

【課題】混成信号回路のデジタル式プログラム可能な最適化のための方法を提供する。

【解決手段】混成信号回路の1つ又はそれ以上のトランジスタ素子100を、1つ又はそれ以上のトランジスタ区分T1、T2、・・・Tnに、それぞれのトランジスタ区分がボディタイバイアス端子を含むようにして、分割することを含んでいる。それぞれのボディタイバイアス端子は、少なくとも1つの電圧バイアスに、それぞれのボディタイバイアス端子を混成信号回路の1つ又はそれ以上のバイアスノードと信号連通させるか、又はそれぞれのボディタイバイアス端子を非精密バイアス電圧ソースと信号連通させるかの何れかによって、連結される。各々のボディタイ端子は、更に、1つ又はそれ以上のデジタル式プログラム可能な記憶要素の別々の1つと信号連通するように配置される。

(もっと読む)

121 - 140 / 395

[ Back to top ]