国際特許分類[H03K17/08]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 過電流または過電圧に対するスイッチ回路の保護のための変形 (526)

国際特許分類[H03K17/08]の下位に属する分類

出力回路から制御回路への帰還のないもの

出力回路から制御回路への帰還によるもの

国際特許分類[H03K17/08]に分類される特許

1 - 10 / 526

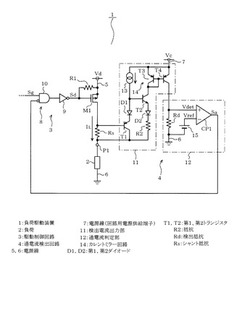

過電流検出回路および負荷駆動装置

【課題】回路用電源電圧としてむやみに高い電圧を用いることなく、シャント抵抗の低電位側端子の電圧がグランド電位付近となる異常が原因で生じる過電流を検出する。

【解決手段】検出電流出力部11は、シャント抵抗Rsの各端子電圧を入力し、その入力した電圧から負荷2に流れる電流に応じた検出電流を出力する。過電流判定部12は、検出電流に基づいて負荷2に過電流が流れているか否かを判定する。検出電流出力部11において、通常時に駆動用電源電圧Vdに近い電圧が印加される部分と、回路用電源電圧Vcに近い電圧が印加される部分との間の経路に第1ダイオードD1および第2ダイオードD2を逆方向に介在させることにより、第1トランジスタT1および第2トランジスタT2がブレークダウンして電流が流れることを阻止する。

(もっと読む)

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

自動回復回路付き制御IC、制御ICの自動回復回路、パワ変換システム及び制御ICの自動回復方法

【課題】予備電源を備えなくても、制御ICが保護モードにて出力以外に自動復元の動作を行って、一定時間後自動に正常動作する。

【解決手段】システムまたは制御ICの異常状態を検出する異常状態検出部110と、異常状態の検出に応じて、保護モードに変更し、該保護モードにて自動回復信号を入力されて動作モードに変更するプロテクション部120と、入力電源からの電力の供給後、IC電源が予め決められた高電圧に到達すると、電力供給遮断信号に応じて入力電源からの電力の供給を遮断し、入力電源からの電力の供給及び遮断を繰り返すIC電源部130と、保護モードの開始に応じて、IC電源部130の電力供給信号及び電力供給遮断信号が交互に繰り返されるクロックをカウントし、該カウント数が予め決められた値に到達すると、プロテクション部120に自動回復信号を供給する自動再開部140とを含む。

(もっと読む)

半導体チップ及びこれをパッケージングした半導体装置

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

スイッチング電源装置

【課題】大型化することなく、アーム短絡および損失増大の問題を解消したスイッチング電源装置を構成する。

【解決手段】ローサイドスイッチング制御部81は、ローサイドスイッチング素子(Q1)へ駆動電圧信号を出力している期間にトランスの巻線電圧の極性反転を検出したときに、遅延時間(td1)の後にローサイドスイッチング素子(Q1)をターンオフさせるローサイドターンオフ回路を備え、ハイサイドスイッチング制御部61は、トランスの巻線電圧の極性が反転してからハイサイドスイッチング素子(Q2)をターンオンさせるまでの時間(td2)を遅延させる。そして、ローサイドターンオフ遅延回路の遅延時間(td1)はハイサイドターンオン遅延回路の遅延時間(td2)よりも短く設定されている。

(もっと読む)

ゲート駆動回路

【課題】逆導通IGBTに内蔵されたダイオードで発生するリカバリ電流を低減させる。

【解決手段】逆導通IGBTに内蔵されているダイオードに順方向電流が流れている間に、逆導通IGBTのゲート−エミッタ間にゲート閾値電圧よりも低い電圧を印加することで、逆導通IGBTのドリフト領域への正孔の注入を抑制し、リカバリ電流を低減させる。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

半導体装置

【課題】スイッチング素子のターンオン直後における、過電流保護回路の誤動作防止と過電流検出遅れ防止とを両立させる。

【解決手段】半導体装置は、スイッチング素子1のセンス端子に流れるセンス電流を電圧(センス電圧)に変換するセンス抵抗4と、センス電圧が閾値を越えたときにスイッチング素子1の保護動作を行う過電流保護回路3とを備える。過電流保護回路3は、上記閾値を、第1基準電圧VREF1またはそれよりも低い第2基準電圧VREF2に切り替えることができる。過電流保護回路3は、スイッチング素子1が定常状態のときは、上記閾値を第2基準電圧VREF2とし、スイッチング素子1のターンオン直後のミラー期間のときは、上記閾値を第1基準電圧VREF1に設定する。

(もっと読む)

過電圧保護回路

【課題】過電圧保護回路を提供することを課題とする。

【解決手段】過電圧保護回路であって、電圧源とポータブル電子デバイスの間に提供された入力電圧が該ポータブル電子デバイスの許容定格耐電圧を超えないように設計する過電圧保護(overvoltage protection)を提供する。該回路は入力ユニットを通じて該電圧源から発生した入力電圧を受け、該入力電圧が分圧モジュールを通じて分圧電圧を生成することで、電圧安定モジュールが第1のスイッチングユニットを短絡状態、或いは、開路状態に入ることができる第1の制御信号を生成させ、また間接的に第2のスイッチングユニットを該第1のスイッチングユニットと逆の短絡状態、或いは、開路状態に入るよう制御し、該入力電圧が該定格電圧を上回った時、該第2のスイッチングユニットを通じて該入力電圧を該ポータブル電子デバイスに供給停止することで、温度の影響を受けることなく過電圧保護を実現できる。

(もっと読む)

演算増幅器

【課題】従来に比してより少ない追加素子数で、消費電流を増加させることなく、出力電流の最大値を、回路定数の調整によって、他の諸特性に影響を及ぼすことなく設定可能とする。

【解決手段】入力信号に対して差動増幅を行う差動増幅回路101と、差動増幅回路101の出力を電圧・電流変換して出力するプリドライバ回路103と、プリドライバ回路103の出力により駆動される出力段106とを有してなる演算増幅器であって、プリドライバ回路103を構成するプリドライバ用トランジスタ3のベース電流の増加を抑圧し、出力電流(出力ソース電流)の過電流保護を可能とした過電流保護回路104が設けられたものとなっている。

(もっと読む)

1 - 10 / 526

[ Back to top ]