Fターム[5J055AX25]の内容

Fターム[5J055AX25]の下位に属するFターム

サージ抑圧回路、スナバ回路 (75)

貫通電流の対策 (114)

クロストーク、漏れ信号の低減 (73)

クロックフィールドスルーの低減 (5)

Fターム[5J055AX25]に分類される特許

1 - 20 / 288

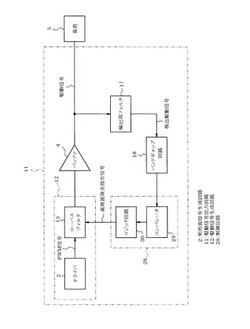

負荷駆動装置

駆動信号出力回路

【課題】負荷、電源などの動作条件が変化しても、電磁妨害等を引き起こす周波数帯域の成分が除去された駆動信号を出力する。

【解決手段】負荷5に与えられる駆動信号をハイパスフィルタまたはバンドパスフィルタからなる検出用フィルタ17を介して検出し、その検出駆動信号をバンドギャップ回路18に入力する。バンドギャップ回路18は、固有の周波数特性を有し、検出駆動信号に固有の周波数帯域内の周波数成分が含まれていると出力電圧が低下する特性を持つ。制御回路28は、バンドギャップ回路18の出力電圧を基準電圧と比較し、検出駆動信号に固有の周波数帯域内の信号成分が含まれるか否かを判定する。含まれる場合には、ローパスフィルタ13により駆動信号から当該周波数帯域内の信号成分を除去する。

(もっと読む)

電源切換装置

【課題】電圧変動の少ない電源切り換えを確実に行うことができる電源切換装置を提供する。

【解決手段】第2電源が接続される第2電源接続部、第2電源の電圧よりも高い電圧の第1電源が接続される第1電源接続部、負荷回路が接続される電源出力部、定電圧回路の出力端子と電源出力部とを接続するダイオード、第1電源接続部とダイオードとの間に挿入され第1電源の電圧を第2電源の電圧よりもダイオードの順方向電圧降下分高い電圧まで降圧する定電圧回路、第2電源接続部と電源出力部との接続をオン/オフするMOSスイッチと、第1電源接続部から電源が供給され、第2電源接続部または電源出力部の電圧と定電圧回路の出力電圧とを比較し、定電圧回路の出力電圧が第2電源接続部または電源出力部の電圧よりも高いとき、第1電源の電圧をMOSスイッチに導通することによってMOSスイッチをオフする比較回路と、を備える。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

ドライバ及びその使用方法

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

半導体装置

【課題】出力信号を高速に変化させかつオーバーシュートやアンダーシュートを抑制できるようにする。

【解決手段】入力信号を反転して出力する主ドライバ11に加えて、補助ドライバ12を設け、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、変化開始から主ドライバの出力信号がある電圧レベルを超えるまでの期間では信号変化を補助するように制御部15により補助ドライバの動作を制御し、主ドライバの出力信号がある電圧レベルを超えてから第2の電圧レベルになるまでの期間に信号変化を抑制するように制御部により補助ドライバの動作を制御するようにして、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制できるようにする。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

半導体装置

【課題】体格及びコストの増大が抑制された半導体装置を提供する。

【解決手段】直流電源とグランドとの間に直列接続された2つの単位回路と、単位回路を制御する制御部と、を備え、2つの単位回路の中点に誘導性負荷が接続された半導体装置であって、2つの単位回路それぞれは、第1スイッチ素子と、第1スイッチ素子と逆並列接続された還流ダイオードと、還流ダイオードと第1スイッチ素子それぞれと並列接続されたバイパス部と、を有し、バイパス部は、直列接続された第2スイッチ素子及び抵抗を有し、制御部は、2つの単位回路の第1スイッチ素子をOFF状態にするデッド期間を挟んで、2つの第1スイッチ素子を交互にON状態とし、デッド期間において、一方の第1スイッチ素子がOFF状態からON状態に移行するまで、一方の第1スイッチ素子と並列接続された第2スイッチ素子をON状態にする。

(もっと読む)

スイッチング素子の駆動装置及びスイッチング素子の駆動方法

【課題】スイッチング損失の増大を抑制しつつ、より高い周波数帯で発生するスイッチングノイズを抑制できるスイッチング素子の駆動装置を提供する。

【解決手段】スルーレート調整部は、NチャネルMOSFETを介してDCモータに出力される電圧波形のスルーレートを変化させ、キャリア周波数によって決まる周波数帯よりも高い周波数帯域に現れるスイッチングノイズの周波数成分を分散させてピークレベルを低下させる。

(もっと読む)

電源回路

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

スイッチング素子の駆動回路

【課題】パワーデバイス(メインスイッチM)のゲートの印加電圧をバッテリ12の正電圧より高い電圧と負電圧との双方の電圧とする場合、電源装置の小型化が困難なこと。

【解決手段】バッテリ12、端子T3、スイッチング素子SW1、コンデンサC、スイッチング素子SW2、逆流防止用ダイオードD1、端子T1および充電用抵抗体14によって、メインスイッチMのゲート充電経路が構成される。また、放電用抵抗体16、端子T2、逆流防止用ダイオードD2、スイッチング素子SW3、コンデンサC,スイッチング素子SW4、および端子T4によって、メインスイッチMのゲート放電経路が構成される。さらに、端子T3、スイッチング素子SW6、逆流防止用ダイオードD4、コンデンサC、逆流防止用ダイオードD3、スイッチング素子SW5および端子T4によって、コンデンサCの充電経路が構成される。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

スイッチング回路

【課題】大電流を制御可能なスイッチング回路において、部品点数を少なくしたコンパクトな構成にて、スイッチング損失を低減するとともにサージ電圧を抑制することができるスイッチング回路を提供する。

【解決手段】高電圧ラインL1と低電圧ラインL2との間においてMOSFET30,31,32,33が並列接続され、ゲート抵抗50,51,52,53の第1の端子がMOSFET30〜33のゲート電極に接続されている。MOSFET30,31,32,33毎に設けられたゲート抵抗50,51,52,53の第2の端子がゲート電圧印加ラインL3を介してパルス発生回路60と接続されている。パルス発生回路60により、ゲート抵抗50〜53を介してMOSFET30〜33のゲート電極にパルス状のゲート電圧が印加される。ゲート電圧印加ラインL3と高電圧ラインL1との間の1箇所にコンデンサ70が接続されている。

(もっと読む)

ゲート駆動回路

【課題】 簡便な回路構成で、高速に動作するゲート駆動回路を提供することである。

【解決手段】 パワー半導体素子のゲート端子に正電圧を印加するためのNPNトランジスタと、パワー半導体素子のゲート端子に負電圧を印加するためのPNPトランジスタと、NPNトランジスタと、PNPトランジスタとに直列に接続された遮断用抵抗器と、遮断用抵抗器に、正極がパワー半導体素子のゲート端子側となるように並列に接続された遮断用抵抗器切換え半導体スイッチとを備えたゲート駆動回路である。

(もっと読む)

1 - 20 / 288

[ Back to top ]