Fターム[5J055AX26]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | 誤動作防止 (777) | ノイズ対策 (690) | スイッチングノイズ対策 (555) | サージ抑圧回路、スナバ回路 (75)

Fターム[5J055AX26]に分類される特許

1 - 20 / 75

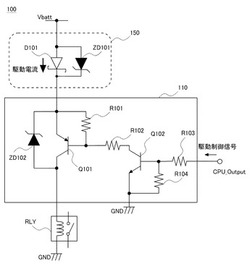

誘導性負荷の駆動回路

リレー装置

【課題】バッテリ逆接続でのリレー動作防止を実現するとともに、リレー回路の駆動電流経路の電圧降下を抑制する技術を提供する。

【解決手段】リレー装置100では、電源電圧VbattからグランドGNDに向けて、逆流防止回路150、リレー駆動回路110及びリレー回路RLYが直列に配置されている。逆流防止回路150は、ショットキーダイオードD101とツェナーダイオードZD101とを備えている。ショットキーダイオードD101とツェナーダイオードZD101とは並列に接続されており、順方向が同じである。

(もっと読む)

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

半導体スイッチ

【課題】半導体スイッチにおいて、エネルギー効率を高くする。

【解決手段】半導体スイッチ1は、LED2を駆動回路3により駆動して発光させ、LED2から発光された光を受光部4により受光する。駆動回路3は、バイポーラトランジスタ31と、コイル32と、ダイオード33等を有する。バイポーラトランジスタ31は、導通状態と非導通状態とに切換えられ、導通状態のときに、電源からLED2に電流が供給される状態にし、非導通状態のときに、電源からLED2に電流が供給されない状態にする。コイル32は、LED2に直列に接続されており、バイポーラトランジスタ31が導通状態から非導通状態になったときに、自己誘導作用によって誘導起電力を発生する。ダイオード33は、LED2及びコイル32に並列に接続されており、バイポーラトランジスタ31が非導通状態のときに、コイル32が発生する誘導起電力によって、LED2に電流を還流させる。

(もっと読む)

半導体チップ及びこれをパッケージングした半導体装置

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

スイッチング装置、スイッチングモジュール

【課題】本発明は、サージ電圧の低減及び発生ノイズの低減を可能とするスイッチング装置、スイッチングモジュールを提供することを目的とする。

【解決手段】本発明にかかるスイッチング装置は、スイッチング素子1と、エミッタ電極100と、エミッタ電極100を外部の主配線に接続するための主配線用エミッタ端子4と、エミッタ電極100と主配線用エミッタ端子4との間の主電流経路に介在する、複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7と、隣接する制御用エミッタ端子間の主電流経路に介挿されたインダクタンス8、インダクタンス9とを備えることを特徴とする。

(もっと読む)

微小電気機械システム(MEMS)アレイを含む電力切替システム

【課題】微小電気機械システム(MEMS)アレイを含む電力切替システムを提供すること。

【解決手段】切替システム(4)は、ダイオードブリッジを形成する複数のダイオードと、複数のダイオードに接近して結合された微小電気機械システム(MEMS)スイッチアレイ(12)とを含む。MEMSスイッチアレイ(12)は(M×N)アレイをなして電気的に接続される。(M×N)アレイは、第2のMEMSスイッチ脚部(44)に並列に電気的に接続された第1のMEMSスイッチ脚部(40)を含む。第1のMEMSスイッチ脚部(40)は直列に電気的に接続された第1の複数のMEMSダイを含み、第2のMEMSスイッチ脚部(44)は直列に電気的に接続された第2の複数のMEMSダイを含む。

(もっと読む)

スイッチング素子の駆動回路

【課題】定電流制御に異常が生じる場合、スイッチング素子S*#が熱破損するおそれが生じたり、スイッチング状態の切替に伴うサージが過度に大きくなったりするおそれがあること。

【解決手段】電源20から出力される正の電荷は、異常検出用抵抗体22、定電流用抵抗体24および充電用スイッチング素子32を介してスイッチング素子S*#のゲートに充電される。この際、定電流用抵抗体24の電圧降下量が規定値となるように、オペアンプ36によって充電用スイッチング素子32のゲート電圧が操作される。異常検出用抵抗体22の電圧降下量は、充電側異常判断部62に取り込まれ、これに基づき定電流制御の異常の有無が判断される。

(もっと読む)

電源供給装置、情報処理装置

【課題】

サージ電圧を効果的に低減するとともに、簡易な回路構成で消費電力を低減した電源供給装置及び情報処理装置を提供する。

【解決手段】

電源供給装置は、交流電力が入力される入力端子と、前記入力端子に入力される交流電力を整流する整流回路と、前記整流回路で整流された電力を平滑化する平滑用キャパシタと、前記平滑用キャパシタの両端子間に直列に接続される、トランス用一次巻線及びスイッチング素子と、前記トランス用一次巻線に結合されるトランス用二次巻線と、前記トランス用二次巻線に接続される出力端子と、前記スイッチング素子に並列に接続されるスナバ回路であって、第1キャパシタ及び第2キャパシタの並列回路と、前記並列回路に直列に接続される抵抗器とを有するスナバ回路とを含む。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】di/dt帰還部23は、IGBT11Uがターンオフするときに、IGBT11のコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。また、di/dt帰還部23は、IGBT11がターンオンするときに、図示せぬFWDの転流電流IFWDに基づいて、帰還電圧VFBを生成する。このようなdi/dt帰還部23は、帰還電圧VFBを駆動信号の電圧の一部として印加するタイミングを遅延させる遅延フィルタとして、LPF回路201を備えている。LPF201の遅延量、即ちインダクタンスLdを適度に調整することで、還流ダイオードの電圧におけるサージ電圧を低減させることができる。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】電子回路1は、IGBT11と、FWD12と、半導体素子駆動回路13と、を備えている。半導体素子駆動回路13は、IGBT11のゲート−エミッタ間の電圧Vgeを可変することによって、IGBT11のターンオン及びターンオフを制御する。半導体素子駆動回路13のdi/dt帰還部23は、電子回路1の主電流であるIGBT11のコレクタ電流Icの時間的変化、即ち時間微分値dIc/dtに基づき帰還電圧VFBを生成し、IGBT11のゲート−エミッタ間の電圧Vgeの一部として加算する。

(もっと読む)

電磁コイル駆動回路及びこれを備えた油圧式エレベータ装置

【課題】接点容量が大きいリレーを用いることなくリレー接点の溶着を防止可能な電磁コイル駆動回路、及びこの電磁コイル駆動回路を備えた油圧式エレベータ装置を提供する。

【解決手段】リレー接点3に並列接続されたCR回路の抵抗7と並列に、ダイオード8を設ける。ダイオード8の向きは、接点開路時に電磁コイル1の電流がダイオード8に流れコンデンサ6が充電される方向とする。接点開路時、電磁コイル1の電流は、ダイオード8を経由してコンデンサ6に流れるため、大容量のコンデンサを備えることにより、アーク発生時間を短縮できる。接点閉路時は、コンデンサ6の電荷がリレー接点3と抵抗7を経由し、突入電流として放電されるので、高抵抗を備えることにより、突入電流を低下できる。よって、接点容量の大きいリレーを採用する必要がなく、電磁コイル駆動回路の小型化、低コスト化及び長寿命化を図ることができる。

(もっと読む)

半導体装置、スナバデバイス

【課題】放熱設計や配線設計によるコストを抑制するスナバデバイスを備えた半導体装置の提供を目的とする。

【解決手段】本発明の半導体装置は、スイッチングトランジスタ1と、スイッチングトランジスタ1と同一導電性基板(フレーム)上に実装されるリカバリーダイオード2及びスナバデバイス6とを備える。スナバデバイス6は、スイッチングトランジスタ1の出力端子C−基準端子E間に接続されたSiC−MOSFET3と、SiC−MOSFET3のゲート端子G−ドレイン端子D間に形成されたツェナーダイオード4と、SiC−MOSFET3のゲート端子G−ソース端子S間に形成された抵抗器5とを備える。スイッチングトランジスタ1の基準端子E、SiC−MOSFET3のソース端子、リカバリーダイオード2のアノード端子が共通接続される。

(もっと読む)

サージ保護回路および電子機器

【課題】直流電圧が重畳された信号を伝送でき、かつ回路内でのサージ対策を少なくすることが可能なサージ保護回路、およびそのサージ保護回路を備えた電子機器を提供する。

【解決手段】電子機器100は、端子1と、インダクタ2と、信号ライン3と、サージ保護回路5と、回路部50とを備える。サージ保護回路5は、バリスタ10と、フィルター11と、ツェナーダイオード12とを含む。フィルター11は、並列LCフィルターを構成する。フィルター11のインピーダンスは、サージによる信号ライン3の電圧の上昇時間に対応するように予め定められた周波数範囲において高い。その一方で、フィルター11のインピーダンスは、周波数が0の場合および信号Sの下限周波数の場合の両方において、上記予め定められた周波数範囲におけるインピーダンスよりも低い。

(もっと読む)

電源用逆流阻止回路

【課題】高電圧の回路に対応することができ、かつ、ICチップ化の可能な電源用逆流阻止回路を提供することを目的とする。

【解決手段】逆流阻止用FETのドレイン端子を入力端子に接続し、ソース端子を出力端子に接続し、ゲート端子をバイアス端子に接続し、逆流阻止用FETの出力側に一方の差動増幅用スイッチ素子を、入力側に他方の差動増幅用スイッチ素子を接続し、入力電圧が出力電圧より高いとき他方の差動増幅用スイッチ素子をオンして逆流阻止用FETを導通し、入力電圧が出力電圧より低いとき一方の差動増幅用スイッチ素子をオンして逆流阻止用FETを非導通とする逆流阻止回路において、入力端子と他方の差動増幅用スイッチ素子との間に、スイッチ素子保護用FETを、そのドレイン端子とソース端子を接続して挿入し、このスイッチ素子保護用FETのゲート端子を基準電圧発生回路に接続する。

(もっと読む)

1 - 20 / 75

[ Back to top ]