Fターム[5J055CX07]の内容

電子的スイッチ (55,123) | 用途(負荷、信号の種類) (3,195) | 主端子に印可される電圧、電流 (739) | 電力制御用 (486)

Fターム[5J055CX07]の下位に属するFターム

単相、3相交流を制御するスイッチ (10)

Fターム[5J055CX07]に分類される特許

1 - 20 / 476

負荷駆動装置

電源回路

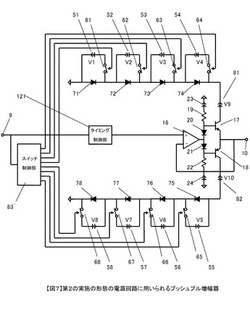

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

(もっと読む)

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

スイッチング素子の駆動回路

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

自動回復回路付き制御IC、制御ICの自動回復回路、パワ変換システム及び制御ICの自動回復方法

【課題】予備電源を備えなくても、制御ICが保護モードにて出力以外に自動復元の動作を行って、一定時間後自動に正常動作する。

【解決手段】システムまたは制御ICの異常状態を検出する異常状態検出部110と、異常状態の検出に応じて、保護モードに変更し、該保護モードにて自動回復信号を入力されて動作モードに変更するプロテクション部120と、入力電源からの電力の供給後、IC電源が予め決められた高電圧に到達すると、電力供給遮断信号に応じて入力電源からの電力の供給を遮断し、入力電源からの電力の供給及び遮断を繰り返すIC電源部130と、保護モードの開始に応じて、IC電源部130の電力供給信号及び電力供給遮断信号が交互に繰り返されるクロックをカウントし、該カウント数が予め決められた値に到達すると、プロテクション部120に自動回復信号を供給する自動再開部140とを含む。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路のレギュレータ回路では、出力電圧の制御精度を十分に高めることができない問題があった。

【解決手段】本発明の半導体集積回路は、制御端子に与えられるインピーダンス制御信号で示される制御値PLに応じて負荷電流Iloadの大きさに対する出力電圧VDDMの大きさを制御する複数の出力トランジスタPMと、出力電圧VDDMの電圧値を示す出力電圧モニタ値VMを出力する電圧モニタ回路12と、出力電圧VDDMの目標値を示す参照電圧Vrefと、出力電圧モニタ値VMと、の間の誤差値の大きさに応じて制御値PLの大きさを制御し、当該制御値PLにより複数の出力トランジスタPMいずれを導通状態とするかを制御する制御回路10と、を有し、制御回路10が負荷電流Iloadの変更を事前に通知する事前通知信号PACCに応じて、誤差値に対する制御値の変化ステップを一定期間の間大きくする。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

制御装置

【課題】電源ユニットの出力ラインにおける地絡などの故障に対し、電源の保護及び故障の検知を行う。

【解決手段】サブ電源供給ラインLSに、サブ電源101側をソースとして第1MOSFET102を直列に接続し、第1MOSFET102のドレインにドレインを接続させて第2MOSFET103を直列に接続する。制御ユニット200内のサブ電源供給ラインLSにも、サブ電源101側をソースとして第3MOSFET202を直列に接続し、第3MOSFET202のドレインにドレインを接続させて第4MOSFET203を直列に接続し、第1〜第4MOSFETを制御することで、サブ電源101の電力を負荷201に対して供給する。各MOSFETのドレイン電圧、及び、第2MOSFET103と第3MOSFET202との間の電圧をモニタし、MOSFETの故障及びサブ電源供給ラインLSの故障を診断する。

(もっと読む)

ドライバ及びその使用方法

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

過電流保護回路

【課題】過電流検出抵抗の温度特性の影響をキャンセルすることのできる過電流保護回路を提供する。

【解決手段】基準抵抗と第1定電流源との第1接続点には、該第1接続点の電位の温度特性が、過電流検出抵抗の電圧検出端子の電位の温度特性と等しくなるように、第1接続点に対して正の温度特性を有する第2定電流を供給する第2定電流源が接続されている。第2定電流源は、負の温度特性を有する第3定電流を供給する第3定電流源と、温度特性を有さない第4定電流を供給する第4定電流源と、第3定電流源に対して直列接続された第1トランジスタと、第4定電流源に対して直列接続された第2トランジスタと、により構成された第1カレントミラー回路と、第4定電流源と第2トランジスタとの接続点に接続され、第1接続点に第2定電流を供給するための電流経路と、を有する。第3定電流源は、過電流検出抵抗と同じ基板に形成されている。

(もっと読む)

半導体モジュール

【課題】半導体スイッチを小さい負担で駆動できるとともに、半導体スイッチに十分なゲート電流を流すことができ、しかも、ゲート配線のインピーダンスによる障害を回避できる半導体モジュール。

【解決手段】ゲートに印加される電圧に応じてオンオフする半導体スイッチQ1と、半導体スイッチのソース電位に対して正極性を有する正極コンデンサ110と、半導体スイッチのソース電位に対して負極性を有する負極コンデンサ111と、正極コンデンサを充電する機能を有し、半導体スイッチをターンオンさせる場合は正極コンデンサからの電流を半導体スイッチのゲートに流すターンオン制御部112と、負極コンデンサを充電する機能を有し、半導体スイッチをターンオフさせる場合は負極コンデンサからの電流を半導体スイッチのゲートに流すターンオフ制御部113を備える。

(もっと読む)

過電流検出装置

【課題】駆動に適した推奨値からずれた電気的特性を持つ負荷を駆動した場合でも誤検出を極力防止する。

【解決手段】しきい値生成回路11は、抵抗13、14にしきい値生成電流ITH、ITLを流してしきい値電圧VTH、VTLを生成し、コンパレータ12はシャント抵抗7の検出電圧Vaと比較して過電流検出信号Scを得る。しきい値補正回路17は、平均負荷電流、負荷電流の交流変化分、電源電圧VBが大きいほどしきい値電圧VTH、VTLを増やし、負荷4の温度が低いほどしきい値電圧VTH、VTLを増やす。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

負荷駆動装置

【課題】負荷電流検出手段により検出された負荷電流を用いてリーク故障を確実に検出する。

【解決手段】駆動回路33a、33bの出力端子Ta2、Tb2から電源線6に至る還流経路内にシャント抵抗9a、9bを接続し、電源線5と給電分岐点Nsとの間に共通のシャント抵抗24を接続する。駆動制御回路32は、MOSFET7a、7bをPWM駆動し、負荷電流検出回路12a、12bから負荷電流Ia、Ibを入力し、総電流検出回路23から総電流Isを入力する。検出負荷電流Ia、Ibに対しそれぞれ対応するPWM駆動信号のオフ駆動期間をマスク処理し、マスク処理した検出負荷電流Iam、Ibmを加算した加算電流Icmと検出総電流Isとを比較する。両者が等しい場合には正常状態と判定し、異なる場合にはショート故障またはリーク故障が生じたと判定する。

(もっと読む)

ハイサイドスイッチ回路

【課題】所定のスイッチング動作を実行しつつ、破壊耐性を向上することが可能なハイサイドスイッチ回路を提供する。

【解決手段】電源電圧をスイッチングして出力するハイサイドスイッチ回路100は、電源電圧Vccが印加される電源端子1に一端が接続された第1の出力MOSトランジスタM1、第1の出力MOSトランジスタの他端に一端が接続され電圧出力端子2に他端が接続された第2の出力MOSトランジスタM2、第1の出力MOSトランジスタに流れる電流の検出信号を出力する電流検出回路6、第1の出力MOSトランジスタが線形領域で動作するように第1の出力MOSトランジスタのゲートに第1の制御電圧を印加する第1のゲートドライバ4、第2の出力MOSトランジスタが線形領域で動作するように第2の出力MOSトランジスタのゲートに第2の制御電圧を印加する第2のゲートドライバ5を備える。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

1 - 20 / 476

[ Back to top ]