Fターム[5J056DD56]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | ダイオード(トランジスタのダイオード接続も含む) (282) | ツェナーダイオード (51)

Fターム[5J056DD56]に分類される特許

1 - 20 / 51

レベルシフト回路

【課題】レベルシフト回路を高速動作する。

【解決手段】一つの実施形態によれば、レベルシフト回路は、第一のトランジスタ、第二のトランジスタ、第一のコンデンサ、及び第二のコンデンサが設けられる。第一のトランジスタは、制御端子に入力電圧が入力される。第二のトランジスタは、制御端子に入力電圧の反転信号が入力される。第一のコンデンサは、一端が第一のトランジスタの第一の端子に接続され、他端に入力電圧の反転信号が入力され、入力電圧の立ち上りのときに電荷を蓄積して第一のトランジスタの第一の端子側から一端側へ第一の電流を発生する。第二のコンデンサは、一端が第二のトランジスタの第一の端子に接続され、他端に入力電圧が入力され、入力電圧の立ち下りのときに電荷を蓄積して第二のトランジスタの第一の端子側から一端側へ第二の電流を発生する。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】トランシーバ回路30等の通信回路に接続される通信線10を構成するHライン通信線10H,Lライン通信線10L間にリンギング抑制回路1が設けられる。リンギング抑制回路1において、バイポーラトランジスタT1のエミッタはHライン通信線10Hに接続され、コレクタはLライン通信線10Lに接続され、ベースはコンデンサC1の一方電極及び抵抗R1の一端に接続され、コンデンサC1の他方電極はLライン通信線10Lに接続され、抵抗R1の他端はHライン通信線10Hに接続される。

(もっと読む)

イネーブル信号生成回路

【課題】後段のイネーブル回路を確実に制御し、また電源電圧が高くなっても消費電流が増大しないようにする。

【解決手段】制御入力端子1にゲートが接続されソースがトランジスタMN2を介して接地に接続されたトランジスタMN1と、トランジスタMN1のドレインと電源VDDとの間に接続された抵抗R2と、抵抗R2の両端にソースとドレインが接続されたトランジスタMP1と、トランジスタのMP1ゲートとソース間に接続された抵抗R3と、ソースがトランジスタMP1のゲートに接続されゲートがトランジスタMP1のドレインに接続されドレインが負荷回路3に接続されたトランジスタMP2とを備え、トランジスタMP2のゲートを制御出力端子2に接続した。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

駆動回路、駆動信号出力回路及びインクジェットヘッド

【課題】出力する駆動信号の遅延を小さくし且つ小型化した安価な駆動回路、駆動信号出力回路及びインクジェットヘッドを実現することである。

【解決手段】駆動回路30は、負荷を駆動するプッシュ側のMOSFET32及びプル側のMOSFET33と、アノード、カソードがMOSFET32のゲート、ソースに接続されたツェナーダイオード38と、アノード、カソードがMOSFET33のソース、ゲートに接続されたツェナーダイオード39と、昇圧回路31の出力端とMOSFET32のゲートとに接続された抵抗36と、昇圧回路31の出力端とMOSFET33のゲートとに接続された抵抗37と、抵抗36、抵抗37に並列に接続されたスピードアップコンデンサ42,43と、を備える。MOSFET32,33のソースが高圧側、グランドに接続され、MOSFET32,33のドレインが互いに接続される。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

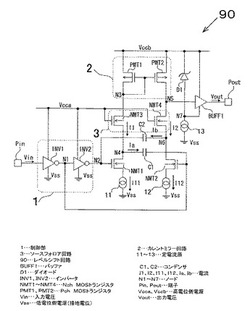

レベル生成回路

【課題】 耐圧の低いMOSFETを保護するためにゲート接地として動作する、MOSFETのゲート電圧を生成するための外部電源を不要にする。

【解決手段】 第1電源電圧から一定の大きさの第1電流を生成する定電流生成部と、第1薄膜NMOSFETと第2薄膜NMOSFETから構成され、第1電流に比例した大きさの第2電流を出力する第1カレントミラー回路部と、第2薄膜NMOSFETを保護するためにゲート接地として用いる第3薄膜NMOSFET及び第1厚膜PMOSFETと、第1電源への電流の逆流を防ぐための第1ダイオードと、第3薄膜NMOSFETのゲート−ソース間電圧がマイナスになることを防ぐための第2ダイオードとからなる保護回路部と、第2電流に比例した大きさの第3電流を出力する第2カレントミラー回路部と、第3電流により第1定電圧を生成する第1ツェナーダイオード部とを備える。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

レベルシフト回路及びそれを用いたスイッチングレギュレータ

【課題】電源電圧を高くしてもトランジスタのゲート耐圧を上げる必要がなく、低電源電圧から高電源電圧まで広範囲に使用できるレベルシフト回路を提供する。

【解決手段】レベルシフトトランジスタ105は、入力トランジスタ101と負荷トランジスタ103との間に、レベルシフトトランジスタ106は、入力トランジスタ102と負荷トランジスタ104との間にそれぞれ接続される。レベルシフトトランジスタ105,106の各ゲートGは共通接続され、その共通接続点にはレベルシフト電圧生成回路120で生成されたレベルシフト電圧Vscが電圧源V1の大きさに応動して印加される。負荷トランジスタ103,104のソース−ゲート間に印加される電圧VSGは、レベルシフト電圧Vscによって、電圧源V1が増減してもほぼ一定になるように設定される。これにより、負荷トランジスタ103,104を低耐圧のトランジスタで構成することができる。

(もっと読む)

レベルシフト回路

【課題】 簡単な回路構成にて、3.3Vのハイレベルと0Vローレベルとを有する第1制御信号を、5Vのハイレベルと0Vのローレベルとを有する第2制御信号に変換して出力する。

【解決手段】 レベルシフト回路1は、抵抗R1と、ダイオードD1と、コンデンサC1、C2と、トランジスタQ1〜Q4とを備える。レベルシフト回路1は、マイコンからの第1制御信号がローレベルのときにコンデンサC1、C2を、+3.3V電源電圧によって別個に充電させ、かつ、ローレベルの第2制御信号を出力する。レベルシフト回路1は、第1制御信号がハイレベルのときにコンデンサC1、C2の充電電圧を加算した値のハイレベルの第2制御信号を出力する。

(もっと読む)

レベルシフト回路、および電力変換装置

【課題】電源電圧の変動の際に、半導体装置の製造ばらつきがあったとしても、容易に誤動作しない低電圧側回路から高電圧側回路に制御信号を伝達するレベルシフト回路を提供する。

【解決手段】レベルシフト回路において、高電圧側の電源電圧変動dV/dtが回路のロジックレベルに影響を与える程度に発生した時において、この変動はセット側にもリセット側にも起こることを利用し、時定数生成回路、もしくは電源電圧変動が先に起こる個所からの信号によって、第1、第2の論理回路において、誤動作の信号が通過するのをマスクして防止する。このマスクするタイミングに充分、余裕をとることにより、半導体プロセスにおける製造ばらつきが個々の素子にあったとしても、高電圧側の電源電圧変動dV/dtが発生時の誤信号がフリップフロップに伝わるのを防止でき、誤動作しない低電圧側回路から高電圧側回路に制御信号を伝達する。

(もっと読む)

ドライブ回路

【課題】低電圧の制御信号を高電圧の制御信号に変換して出力する高圧用のドライブ回路において、待機時の消費電力を削減することができるようにする。

【解決手段】低圧部1からの制御信号a1〜d1及びa2〜d2により高圧部2のトランジスタMN1〜MN8を駆動し、操作対象3に駆動信号を出力する。その際、低圧部1からの制御信号a1〜d1をそれぞれ論理積ゲートQ1〜Q4の一方の入力端子を介して高圧部2のトランジスタMN1,MN3,MN5,MN7のゲートに入力し、論理積ゲートQ1〜Q4の他方の入力端子には高圧部2のオン/オフ信号を入力する。

(もっと読む)

通信システム、及びノード

【課題】差動信号の伝送路として、幹線と、該幹線からそれぞれ分岐する複数の支線とを有し、その各支線にノードが接続された通信システムにおいて、通信に必要な信号振幅を確保しつつ反射を抑制する。

【解決手段】ノード内のトランシーバ15は、回路55と抵抗56とからなる回路50を備える。回路55は、直列接続されたダイオード51,53と、同じく直列接続されたダイオード52,54とが並列に接続されたものである。バス10の電位が回路55の順方向電圧降下分以下であれば回路55に電流は流れず、バス10から見たインピーダンスは高く維持され、受信バッファ42に安定した信号を入れることができる。一方、バス10の電位が回路55の順方向電圧降下分を超えたことで回路55に電流が流れると、バス10から見たインピーダンスは抵抗56のインピーダンスとなり、インピーダンスマッチングで反射を抑制できる。

(もっと読む)

コンパレータ回路

【課題】出力電圧信号の振幅を十分にとれない場合があった。

【解決手段】本発明は、参照電圧を入力する第1、第2の端子と、基準電圧を入力する第3の端子と、検出すべき電圧を入力する第4の端子と、参照電圧の電位差に応じた電流をそれぞれ流す第1、第2のトランジスタ(以下、Tr)と、第1のTrと直列接続される第3のTrと、第2のTrと直列接続される第4のTrと、第3のTrの流す電流に応じたミラー電流を流す第5のTrと、第4のTrの流す電流に応じたミラー電流を流す第6のTrと、第6のTrと第4の端子との間に接続される第7のTrと、第5のTrと第3の端子との間に接続され、第7のTrの流す電流に応じたミラー電流を流す第8のTrと、を有し、第5、第8のTrの中間ノードの電圧に応じた電圧を出力信号として出力するコンパレータ回路である。

(もっと読む)

1 - 20 / 51

[ Back to top ]