Fターム[5J056DD12]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | FET (1,892)

Fターム[5J056DD12]の下位に属するFターム

MISFET、MOSFET、IGFET (1,327)

GaAsFET、ショットキーFET (7)

ゲート、ソース、ドレインが2以上のもの (2)

しきい値 (78)

Fターム[5J056DD12]に分類される特許

1 - 20 / 478

複数の集積回路にインタフェース信号を供給する方法および回路

半導体装置

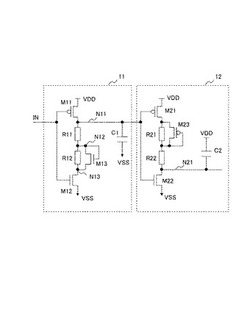

【課題】容量を充放電させ信号を遅延させる回路の遅延時間の温度依存性を緩和し回路規模の増大を抑制可能とした半導体装置の提供。

【解決手段】互いに異なる電源電圧を与える第1の電源(VDD)と第2の電源(VSS)の間に直列に接続され、制御電極が共通に接続された第1及び第2のFET(M11、M12)と、前記第1及び第2のFETの間に接続する第1の回路を有するインバータを備え、前記第1の回路は、互いに並列に接続された第1の抵抗素子(R12)と第3のFET(M13)を備え、前記第1の抵抗素子(R12)の抵抗値は正の温度特性を有し、前記第3のFET(M13)は、その動作範囲に、第3のFET(M13)の端子間抵抗が、第1の抵抗素子(R12)の温度特性と逆極性の負の温度特性を示す領域を含む。

(もっと読む)

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体装置

【課題】積層され、貫通電極で相互に接続された複数の半導体チップの出力インピーダンスのバラツキを抑える。

【解決手段】半導体装置100は、第1の被制御チップ110と、第1の被制御チップ110を制御する制御チップ120とを備える。第1の被制御チップ110は、第1の出力回路と同一の構成を持つ第1のレプリカ出力回路111と、第1のレプリカ出力回路111に接続される第1のZQ端子112と、第1のZQ端子に接続される第1の貫通電極113と、第1のレプリカ出力回路111のインピーダンスを設定する第1の制御回路114と、を含む。制御チップ120は、第1の貫通電極113に接続される第2のZQ端子121と、第2のZQ端子121の電圧と参照電圧Vrefとを比較する比較回路122と、比較回路122からの比較結果に応じて処理を行う第2の制御回路123と、を含む。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

スイッチ回路

【課題】多くの個別素子による回路を用いることなく、容易に簡素な回路構成で端子外れ検出を行うことが可能なスイッチ回路の提供。

【解決手段】ゲートがセンサ回路に接続され、ドレインが第1の電圧制限抵抗に接続された第1の出力ドライバと、物理量検出信号出力端子と接地端子の間に接続された第2の電圧制限抵抗と、非反転入力端子が第1の基準電圧回路に接続され、反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第1の比較器と、反転入力端子が第2の基準電圧回路に接続され、非反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第2の比較器と、ゲートが前記論理回路の出力に接続され、ドレインが断線診断信号出力端子に接続された第2の出力ドライバで構成した。

(もっと読む)

論理回路及びデータ処理システム

【課題】素子数が少なく、遅延が小さく、ドライバ能力を有するXORゲート回路を提供する。

【解決手段】論理回路1は、電源電位VPERIとノードn1の間に接続されたトランジスタT1と、電源電位VPERIとノードn2の間に接続されたトランジスタT2と、電源電位VSSとノードn3の間に接続されたトランジスタT3と、電源電位VSSとノードn4の間に接続されたトランジスタT4と、ノードn1とノードn3の間に直列接続されたトランジスタT5,T7と、ノードn1とノードn3の間に直列接続されたトランジスタT9,T11と、ノードn2とノードn4の間に直列接続されたトランジスタT6,T8と、ノードn2とノードn4の間に直列接続されたトランジスタT10,T12とを備える。出力信号Yは、トランジスタT5,T7の接続点及びトランジスタT6,T8の接続点から取り出される。

(もっと読む)

出力回路、信号伝送回路及び信号伝送方法

【課題】電源ノイズの低減を図ることができる出力回路を提供する。

【解決手段】本発明の実施の形態に係る出力回路Oは、論理信号を出力するCMOS回路OAと、CMOS回路OAと同じ論理信号を出力する、CMOS回路OAと並列に設けられた電流一定回路OBと、入力される選択信号Sに応じて、CMOS回路OAと電流一定回路OBのいずれか一方にデータDを入力し、データDに応じた論理信号を出力させる選択回路SLとを備え、電源ノイズを許容値以下に抑える必要がある場合に、電流一定回路OBを選択する。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

半導体集積回路

【課題】外部から印加された電圧のノイズを減少させて電圧を安定化させる半導体集積回路を提供する。

【解決手段】本発明は、電圧ノイズを減少させて電圧を安定化させる半導体集積回路において、第1電流が流れる第1内部回路と、第2電流が流れる第2内部回路と、前記第1電流のうちの一部と前記第2電流のうちの一部は第1接地パッドに流れ、残りの前記第1電流と残りの前記第2電流は第2接地パッドに流れるように構成された電圧安定化部とを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】ハイサイド駆動回路が負バイアス駆動を行いつつ、ブートストラップコンデンサによりハイサイド駆動回路に駆動電圧を供給することができる半導体装置を得る。

【解決手段】基準電圧回路3は、ハイサイド駆動回路1の高圧端子VBの電圧と低圧端子VEの電圧との間の基準電圧を生成して、ハイサイドスイッチング素子Q1とローサイドスイッチング素子Q2の接続点に供給する。充電用スイッチング素子Q3のドレインがハイサイド駆動回路1の低圧端子VEに接続され、ソースが接地されている。

(もっと読む)

半導体集積回路及びその電源制御方法

【課題】電源遮断状態からの復帰の際に、周辺回路の動作に影響を与えない半導体集積回路及び電源制御方法が、望まれる。

【解決手段】半導体集積回路は、第1及び第2の電源線と、サブ電源線と、第1の電源線とサブ電源線との間に配置される第1のスイッチ回路と、第2の電源線とサブ電源線との間に配置される論理回路と、第1の端子が第1の電源線と接続される容量素子と、容量素子の第1の端子の他方の第2の端子の接続を、第1の電源線、又は、サブ電源線、のいずれかに切り替える第2のスイッチ回路と、論理回路を非活性化状態から活性化状態に遷移させる場合に、第1のスイッチ回路により、第1の電源線及びサブ電源線の接続を遮断しつつ、第2のスイッチ回路により、第2の端子の接続を少なくても1回以上、サブ電源線に接続した後、第1の電源線に接続する制御回路と、を備えている。

(もっと読む)

半導体装置

【課題】しきい値電圧のばらつきの影響を低減する。

【解決手段】トランジスタのゲート・ソース間に設けられた容量素子に電荷を充電し、その後容量素子に充電された電荷を放電することで該トランジスタのしきい値電圧を取得し、その後負荷に電流を流す半導体装置において、容量素子の一方の端子の電位は、ソース線の電位より大きく設定し、ソース線の電位は電源線の電位及び負荷のカソード側の電位よりも小さい電位に設定する。

(もっと読む)

ブートストラップ回路

【課題】飛び込みの影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第4TRから構成され、第1TRにおいて、一方のS/D領域は第2TRの一方のS/D領域に接続され、他方のS/D領域には、2相のクロックのうち一方のクロックが印加され、ゲート電極は、第3TRの一方のS/D領域に接続され、第2TRにおいて、他方のS/D領域は電圧供給線に接続され、第3TRにおいて、他方のS/D領域には入力信号が印加され、ゲート電極には他方のクロックが印加され、第1TRのゲート電極と第3TRの一方のS/D領域とは、第3TRがオフ状態になると浮遊状態となるノード部を構成し、第4TRにおいて、一方のS/D領域は、反転回路の入力側に接続されると共に、該反転回路の出力側と第2TRのゲート電極とが接続されており、他方のS/D領域は入力信号が印加され、ゲート電極には他方のクロックが印加される。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】素子面積の増加を抑制しつつ、動作速度が向上する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、ボディ領域11a、11bと、ボディ領域11a、11b上にゲート絶縁層12a、12bを介して配置されるゲート電極13a、13bと、ボディ領域11a、11bを挟んで配置される一対のソース/ドレイン領域14a、14b、14cと、を有する電界効果型トランジスタ10a、10bを複数備え、複数のトランジスタ10a、10bは、ボディ領域11a、11b同士が電気的に接続されており、複数のトランジスタ10a、10bの内の一のトランジスタ10aのゲート電極13aのみが、複数のトランジスタ10a、10bの内の何れかのトランジスタのボディ領域と電気的に接続される。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMの少なくとも一方の振幅に応じて変化する制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含む。制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

電子回路

【課題】高い精度で所定の検査を行うことができる電子回路を提供する。

【解決手段】本実施の形態に係る電子回路1は、図1(a)に示すように、主に、主回路2への電圧Vccの供給を切り替えるスイッチ素子としてのp型トランジスタ3と、p型トランジスタ3を駆動する第1の駆動信号を出力する駆動部4と、入力側が駆動部4に電気的に接続され、出力側がp型トランジスタ3に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて第2の駆動信号を出力する第1のインバータ部5と、入力側が駆動部4に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて検査のための検査信号を出力する第2のインバータ部6と、第2のインバータ部6の出力側に電気的に接続され、検査信号を出力する第1のパッドとしての検査パッド7と、を備えて概略構成されている。

(もっと読む)

1 - 20 / 478

[ Back to top ]