Fターム[5J056GG04]の内容

論理回路 (30,215) | 制御対象、制御態様 (2,427) | 出力電流を制御するもの (174) | 段階的に制御するもの (163) | あるノードの電位を利用するもの (95)

Fターム[5J056GG04]に分類される特許

1 - 20 / 95

半導体装置

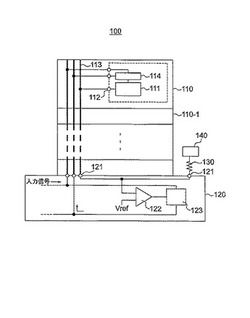

【課題】積層され、貫通電極で相互に接続された複数の半導体チップの出力インピーダンスのバラツキを抑える。

【解決手段】半導体装置100は、第1の被制御チップ110と、第1の被制御チップ110を制御する制御チップ120とを備える。第1の被制御チップ110は、第1の出力回路と同一の構成を持つ第1のレプリカ出力回路111と、第1のレプリカ出力回路111に接続される第1のZQ端子112と、第1のZQ端子に接続される第1の貫通電極113と、第1のレプリカ出力回路111のインピーダンスを設定する第1の制御回路114と、を含む。制御チップ120は、第1の貫通電極113に接続される第2のZQ端子121と、第2のZQ端子121の電圧と参照電圧Vrefとを比較する比較回路122と、比較回路122からの比較結果に応じて処理を行う第2の制御回路123と、を含む。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

半導体集積回路及びその電源制御方法

【課題】電源遮断状態からの復帰の際に、周辺回路の動作に影響を与えない半導体集積回路及び電源制御方法が、望まれる。

【解決手段】半導体集積回路は、第1及び第2の電源線と、サブ電源線と、第1の電源線とサブ電源線との間に配置される第1のスイッチ回路と、第2の電源線とサブ電源線との間に配置される論理回路と、第1の端子が第1の電源線と接続される容量素子と、容量素子の第1の端子の他方の第2の端子の接続を、第1の電源線、又は、サブ電源線、のいずれかに切り替える第2のスイッチ回路と、論理回路を非活性化状態から活性化状態に遷移させる場合に、第1のスイッチ回路により、第1の電源線及びサブ電源線の接続を遮断しつつ、第2のスイッチ回路により、第2の端子の接続を少なくても1回以上、サブ電源線に接続した後、第1の電源線に接続する制御回路と、を備えている。

(もっと読む)

半導体装置

【課題】適宜繰り返し行われるキャリブレーションに要する時間を短縮する。

【解決手段】半導体装置は、入力コマンドに応じ、出力ドライバーのインピーダンスを調整するキャリブレーションを、設定値を用いて行うキャリブレーション回路と、温度センサーと、前記出力ドライバーの温度特性情報を記憶する記憶回路と、前記温度センサーからの検出信号と前記記憶回路から読み出した前記温度特性情報とに基づいて前記設定値を変更する設定信号を生成し、前記キャリブレーション回路へ出力する設定回路と、を備える。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

出力バッファ回路

【課題】 著しい遅延の増大を招くことなく、出力バッファ回路の貫通電流を防止する。

【解決手段】 出力段駆動部100は、出力信号VOUTを立ち下げる場合、Pチャネルトランジスタ201をOFFに遷移させ、そのドレイン電流が閾値電流Ith1を下回ったとき、Nチャネルトランジスタ202をONに遷移させ、出力信号VOUTを立ち上げる場合、Nチャネルトランジスタ202をOFFに遷移させ、そのドレイン電流が閾値電流Ith2を下回ったとき、Pチャネルトランジスタ201をONに遷移させる。閾値設定部130は、入力信号VINに出力信号VOUTを立ち下げる変化があったとき、Pチャネルトランジスタ201のドレイン電流に応じた値に閾値電流Ith1を設定し、閾値設定部140は、入力信号VINに出力信号VOUTを立ち上げる変化があったとき、Nチャネルトランジスタ202のドレイン電流に応じた値に閾値電流Ith2を設定する。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

出力バッファ回路

【課題】出力信号のデューティを保ちつつ消費電流の変化を低減する。

【解決手段】出力バッファ回路は、出力回路(300)と、第1入力回路(210)と、第2入力回路(220)と、第1クランプ回路(110)と、第2クランプ回路(120)とを具備する。出力回路(300)は、第1出力トランジスタ(P301)と第2出力トランジスタ(N301)とを備え、出力信号(VOUT)を出力する。第1クランプ回路(110)および第2クランプ回路(120)のそれぞれは、カスコード接続される第1導電型のトランジスタ(P111/P121)と、第2導電型のトランジスタ(N111/N121)とを備える。第1クランプ回路(110)は、所定の期間第1入力回路(210)の出力電圧(VA1)をクランプする。第2クランプ回路(120)は、所定の期間第2入力回路(220)の出力電圧(VA2)をクランプする。

(もっと読む)

半導体装置

【課題】しきい値が従来例では動作しないような値でも動作させることが可能な半導体装置である。

【解決手段】第1乃至第3のN型トランジスタと、第1乃至第3のP型トランジスタと、アナログスイッチと、容量手段とを有し、容量手段の一方は、アナログスイッチ、第3のN型トランジスタのソース又はドレインの他方、及び第3のP型トランジスタのソース又はドレインの他方と電気的に接続され、容量手段の容量は、第1のP型トランジスタ及び第1のN型トランジスタで発生する容量より大きく、アナログスイッチには、第1のラッチ信号、第2のラッチ信号、及びデータ信号が入力され、第1のラッチ信号は、第2のP型トランジスタのゲート、及び第3のN型トランジスタのゲートに入力され、第2のラッチ信号は、第2のN型トランジスタのゲート、及び第3のP型トランジスタのゲートに入力される半導体装置である。

(もっと読む)

レベルシフタ回路および表示ドライバ回路

【課題】回路面積を大きくすることなく入力信号に対する応答速度が速いレベルシフタ回路および表示ドライバ回路を提供することである。

【解決手段】本発明にかかるレベルシフタ回路1は、第1の電圧変換回路11、第2の電圧変換回路12を備える。第1の電圧変換回路11は、電源電位GNDと電源電位VDDLとの間の振幅を有する入力信号INが入力されると共に、電源電位VDDLよりも高い電源電位VDDHが供給される。また、電源電位VDDHの電源線41から供給される電流を制限する電流制限回路34を備え、入力信号INよりも大きな振幅を有する電圧信号を入力信号INに応じて出力する。第2の電圧変換回路12は、電源電位VDDHが供給されると共に、第1の電圧変換回路11から出力された電圧信号に応じて電源電位GNDと電源電位VDDHとの間の振幅を有する出力信号を出力する。

(もっと読む)

半導体集積回路装置

【課題】簡易な構造により、MOSFETのサブスレショールドリーク電流を低減することができる半導体集積回路装置を提供すること。

【解決手段】本発明にかかる半導体集積回路装置は、被制御回路5と基板バイアス制御回路101を有する。被制御回路5は、基板上に形成される1以上のMOSFETを有する。基板バイアス制御回路101は、出力端から被制御回路5の基板に供給する基板バイアスを制御する。基板バイアス制御回路101は、N型MOSFET1及び2を有する。N型MOSFET2は、被制御回路5のMOSFETと同じ電流−電圧特性を有し、サブスレショールドリーク電流を接点Bの電圧VBに変換する。N型MOSFET1は、一端が基板バイアス制御回路101の出力端と接続され、接点Bの電圧VBに応じて基板バイアスを接地電位以下に制御する。

(もっと読む)

差動増幅器

【課題】負荷側に出力を電流で受け渡すカレントミラー回路を備える差動増幅器の動作を高速化する。

【解決手段】差動増幅器を構成し、差動増幅器に対する2つの入力の内のそれぞれ1つが与えられる各トランジスタの端子の内で、差動増幅器の出力点となりうるそれぞれの端子の間に接続される回路素子を備える差動増幅器は、カレントミラー回路においてモニタ電流が流れるトランジスタに接続されるとともに、カレントミラー回路においてコピー電流が流れる第1のトランジスタと、前記出力が受け渡される負荷としての抵抗との間に接続される前記2つの入力のうちいずれか1つが与えられるトランジスタへの入力がLの時にオフとなる第2のトランジスタと、第1のトランジスタと第2のトランジスタとの接続点とアースとの間に接続される電流源とをさらに備えることにより、上記課題の解決を図る。

(もっと読む)

半導体集積回路

【課題】回路本体のリーク電流を速やかに低減させる。

【解決手段】半導体集積回路100は、回路本体101、回路本体101の電源端101bに接続された疑似電源線VA、疑似電源線VAにNチャネルMOSトランジスタMS1を介して接続された低電位電源線V1、回路本体101の電源端101aに接続された高電位電源線V2、導通時に疑似電源線VAと高電位電源線V2との電位差を小さくするように疑似電源線VA及び低電位電源線V1に接続されたダイオードDI1、及び疑似電源線VA及び高電位電源線V2に接続されたPチャネルMOSトランジスタMS2を備える。

(もっと読む)

出力回路、入力回路及び入出力回路

【課題】自身の電源電位より高い電位のみならず、自身の接地電位GNDより低い電位が印加されても、トランジスタ素子の破壊や、電流の流れ込み、流れ出しを防止することを目的としている。

【解決手段】出力端子から当該出力回路への電流の流れ込みを防止する第一のリーク電流防止回路と、当該出力回路から前記出力端子への電流の流れ出しを防止する第二のリーク電流防止回路と、前記出力端子に当該出力回路の電源電圧よりも高い電圧が印加されたとき、前記第一のリーク電圧防止回路を動作させ、前記出力端子に接地電圧よりも低い電圧が印加されたとき、前記第二のリーク電流防止回路を動作させる選択回路と、を有する。

(もっと読む)

デューティサイクル補正を行う方法

【課題】不均一なデューティサイクルを有する入力信号のデューティサイクル補正を行う方法を提供する。

【解決手段】不均一なデューティサイクルを有する入力信号をコンデンサ・デジェネレイティング差動対回路に入力し、前記回路内の1つ以上のコンデンサの両端に、前記入力信号のデューティサイクルの正の部分と負の部分との継続時間の差を表わす直流電圧を形成し、差動対回路のスイッチング動作を通じてデューティサイクルを有する出力信号を形成し、それによって出力信号のデューティサイクルの正の部分と負の部分の継続時間が、入力信号とスイッチングレベルとの交差点により規定される。必要に応じて、出力信号のデューティサイクルが少なくとも実質的に均一になるまで、信号(およびスイッチングレベル)が調整される。

(もっと読む)

半導体装置

【課題】チップの製造プロセスの微細化にともなって各種リーク電流(サブスレッショルドリーク電流、ゲートトンネルリーク電流、GIDL(Gate-Induced Drain Leakage)電流などの接合リーク電流)が増大している。それらのリーク電流はチップの消費電流を増加する。

【解決手段】第1回路ブロックと、前記第1回路ブロックに接続される第1電源線及び第2電源線と、前記第1電源線と第1電位を供給する第1電位点とを接続するための第1トランジスタと、前記第1トランジスタのゲートに接続される第1駆動回路と、前記第1駆動回路より駆動力の大きい第2駆動回路とを有し、第1の状態から前記第1の状態よりも前記第1電源線と前記第2電源線の間の電位差が大きい第2の状態へ遷移する場合に、第1の期間において前記第1トランジスタを前記第1駆動回路によって駆動し、その後第2の期間において前記第1トランジスタを前記第2駆動回路によって駆動する。

(もっと読む)

1 - 20 / 95

[ Back to top ]