Fターム[5J055EY13]の内容

Fターム[5J055EY13]に分類される特許

1 - 20 / 274

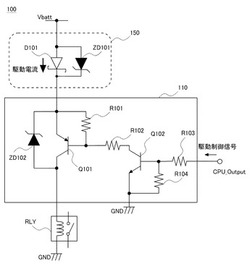

誘導性負荷の駆動回路

リレー装置

【課題】バッテリ逆接続でのリレー動作防止を実現するとともに、リレー回路の駆動電流経路の電圧降下を抑制する技術を提供する。

【解決手段】リレー装置100では、電源電圧VbattからグランドGNDに向けて、逆流防止回路150、リレー駆動回路110及びリレー回路RLYが直列に配置されている。逆流防止回路150は、ショットキーダイオードD101とツェナーダイオードZD101とを備えている。ショットキーダイオードD101とツェナーダイオードZD101とは並列に接続されており、順方向が同じである。

(もっと読む)

スイッチング素子の駆動回路

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

スイッチング電源装置

【課題】大型化することなく、アーム短絡および損失増大の問題を解消したスイッチング電源装置を構成する。

【解決手段】ローサイドスイッチング制御部81は、ローサイドスイッチング素子(Q1)へ駆動電圧信号を出力している期間にトランスの巻線電圧の極性反転を検出したときに、遅延時間(td1)の後にローサイドスイッチング素子(Q1)をターンオフさせるローサイドターンオフ回路を備え、ハイサイドスイッチング制御部61は、トランスの巻線電圧の極性が反転してからハイサイドスイッチング素子(Q2)をターンオンさせるまでの時間(td2)を遅延させる。そして、ローサイドターンオフ遅延回路の遅延時間(td1)はハイサイドターンオン遅延回路の遅延時間(td2)よりも短く設定されている。

(もっと読む)

ゲート駆動回路

【課題】逆導通IGBTに内蔵されたダイオードで発生するリカバリ電流を低減させる。

【解決手段】逆導通IGBTに内蔵されているダイオードに順方向電流が流れている間に、逆導通IGBTのゲート−エミッタ間にゲート閾値電圧よりも低い電圧を印加することで、逆導通IGBTのドリフト領域への正孔の注入を抑制し、リカバリ電流を低減させる。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

負荷制御装置

【課題】高デューティ領域においてデューティ比が不正確になるのを防止することにより、デューティ比の精度を向上させた負荷制御装置を提供する。

【解決手段】三角波生成回路5が、負荷2に供給される電源電圧VIから三角波VC1を生成する。パルス駆動回路6が、三角波生成回路5により生成される三角波VC1と基準電圧Vkとの比較に応じたデューティ比の駆動パルスを負荷2に供給する。基準電圧生成回路7が、電源電圧VIが増加するに従って基準電圧Vkを増加または減少させて駆動パルスのデューティ比を減少させる。周波数調整回路8が、電源電圧VIが所定電圧以下のときに、三角波生成回路5により生成される三角波VC1の周波数を低くして駆動パルスの周波数を低くする。

(もっと読む)

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

ドライブ回路

【課題】トランスの補助巻線を用いることなく、制御回路の電源を確保して安価にできるドライブ回路を提供する。

【解決手段】ノーマリオン型のハイサイドスイッチQ1とノーマリオフ型のローサイドスイッチQ2との直列回路が直流電源に並列に接続され、ハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ回路であって、ハイサイドスイッチとローサイドスイッチとを制御信号によりオンオフさせる制御回路10と、ハイサイドスイッチとローサイドスイッチとの接続点に一端が接続された整流手段D2と、整流手段の他端と直流電源の一端とに接続され且つ制御回路に電源を供給するコンデンサC2と、制御回路からの制御信号とコンデンサからの電圧とに基づいてハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ部A1,AND1,Q3,Q4とを備える。

(もっと読む)

電子機器装置

【課題】電子機器装置において、減電圧状態になった場合及び過電圧状態になった場合に、より確実に回路を保護する。

【解決手段】電子機器装置1は、第1の規定電圧値以下の電圧が電子機器装置1に供給される減電圧状態になった場合に、マイコン8をリセットさせ、第2の規定電圧値以上の電圧が電子機器装置1に供給される過電圧状態になった場合に、ヒューズ10を溶断させる減電圧/過電圧検出回路11を備える。減電圧/過電圧検出回路11は、平滑用のコンデンサ4により平滑化された電圧(1次側電圧出力ラインL1から出力された電圧)を監視し、平滑用のコンデンサ4により平滑化された電圧に基いて、減電圧状態、及び過電圧状態を検出する。そして、減電圧/過電圧検出回路11は、過電圧状態を検出した場合には、マイコン8をリセットさせ、過電圧状態を検出した場合には、ヒューズ10を溶断させる。

(もっと読む)

ブートストラップ回路、半導体装置

【課題】ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を提供する。

【解決手段】ブートストラップ部用電源供給部10は、抵抗R1からなる回路である。抵抗R1の一方の端子は、P母線と接続している。抵抗R1の他方の端子は、コンデンサC1およびツェナーダイオードD1の並列回路の一端と接続している。コンデンサC1は、充電された電圧をスイッチング素子駆動用回路(HVIC4)に印加する。抵抗R1は、メイン電源母線に一方の端子が接続し、他方の端子がコンデンサC1と接続して、メイン電源母線の電圧をコンデンサC1に印加する。抵抗R1によって、メイン電源側からブートストラップ回路のコンデンサC1を充電することができる。

(もっと読む)

ハイサイドスイッチ回路

【課題】所定のスイッチング動作を実行しつつ、破壊耐性を向上することが可能なハイサイドスイッチ回路を提供する。

【解決手段】電源電圧をスイッチングして出力するハイサイドスイッチ回路100は、電源電圧Vccが印加される電源端子1に一端が接続された第1の出力MOSトランジスタM1、第1の出力MOSトランジスタの他端に一端が接続され電圧出力端子2に他端が接続された第2の出力MOSトランジスタM2、第1の出力MOSトランジスタに流れる電流の検出信号を出力する電流検出回路6、第1の出力MOSトランジスタが線形領域で動作するように第1の出力MOSトランジスタのゲートに第1の制御電圧を印加する第1のゲートドライバ4、第2の出力MOSトランジスタが線形領域で動作するように第2の出力MOSトランジスタのゲートに第2の制御電圧を印加する第2のゲートドライバ5を備える。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

半導体装置

【課題】駆動用のスイッチ素子によって出力端子からの出力を制御する半導体装置において、端子に静電気が印加されたときに、スイッチ素子をより確実に保護し得る構成を、装置構成の大型化を抑えて実現する。

【解決手段】半導体装置1は、高電位側電源又は低電位側電源の一方からなる基準部にスイッチ素子の第1端子が接続され、出力端子P1にスイッチ素子の第2端子が接続されている。また、スイッチ素子と並列に第1保護素子が設けられている。また、基準部とは逆側の電源(他方部)と出力端子の間には第2保護素子が接続されている。そして、基準部とは逆側の電源(他方部)側には無効化手段が接続され、出力端子へのサージ電圧の印加によって駆動電圧が発生した場合に、当該駆動電圧の発生後の所定時間、制御入力端子への通電信号の入力を無効化し、所定時間の経過後に無効化を解除するように機能している。

(もっと読む)

アクティブクランプ回路

【課題】アクティブクランプ動作期間を短縮するとともにESD耐量を向上させたアクティブクランプ回路を提供する。

【解決手段】実施形態によれば、第1のスイッチ素子と、第1のダイオードと、第1の抵抗と、第1および第2の制御回路と、を備えたことを特徴とするアクティブクランプ回路が提供される。前記第1のダイオードは、前記第1のスイッチ素子の両端にかかる過電圧によりブレークダウンする。前記第1の抵抗は、前記第1のダイオードの電流を検出する。前記第1の制御回路は、前記第1の抵抗の両端の電圧を増幅して前記第1のスイッチ素子の電流を制御する。前記第2の制御回路は、前記第1の抵抗の両端の電圧に応じて前記第1のスイッチ素子の導通を制御する。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体かなるスイッチング素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続されたコンデンサC1と抵抗R1とからなる並列回路と、並列回路にコンデンサC2とスイッチング素子Q2と抵抗R2からなる直列回路がさらに並列接続され、コンデンサC2とスイッチング素子Q2との接続点にダイオードD1のアノードが接続され、ダイオードD1のカソードとスイッチング素子Q2のゲートはスイッチング素子Q1のソースに接続され、制御信号のオフ信号に対してスイッチング素子Q1ゲートを負電位にバイアスする。

(もっと読む)

1 - 20 / 274

[ Back to top ]