Fターム[5J055EZ20]の内容

Fターム[5J055EZ20]に分類される特許

1 - 20 / 258

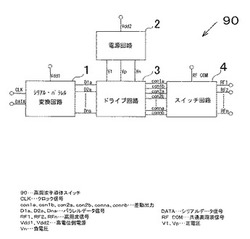

高周波半導体スイッチ、端末装置

【課題】スイッチ回路の誤動作の発生を防止する。

【解決手段】一つの実施形態によれば、シリアル・パラレル変換回路は、第一の高電位側電源が供給され、シリアルデータ信号が入力され、パラレルデータ信号を生成する。電源回路は、第二の高電位側電源が供給され、第二の高電位側電源に基づいて第一の正電圧、第二の正電圧、及び負電圧を生成する。ドライブ回路は、第一の正電圧が電源として供給され、パラレルデータ信号が入力されるインバータと、第二の正電圧及び負電圧が電源として供給され、パラレルデータ信号及びインバータの出力信号が入力される差動型レベルシフタを含むレベルシフト回路が設けられ、第二の正電圧をハイレベルの信号としてスイッチ回路に出力し、負電圧をローレベルの信号としてスイッチ回路に出力する。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

レベルシフト回路及びそれを用いたドライバと表示装置

【課題】低振幅の入力信号を高速に高振幅信号に変換するレベルシフト回路を提供する。

【解決手段】第1及び第2の出力端子の一方を第1電圧レベルに設定する第1のレベルシフト回路10と、第2の電圧端子と、前記第1及び第2の出力端子との間に接続され、前記第1及び第2の出力端子の他方を第2電圧レベルに設定する第2のレベルシフト回路20と、第1の制御信号に基づき、第1及び第2の入力信号が第1及び第2の入力端子に入力される時点で前記第2電圧レベルとされる一つの出力端子について、前記一つの出力端子と第2の給電端子間の電流経路を、前記第1及び第2の入力信号が前記第1及び第2の入力端子に入力される時点を含む所定期間、切断し、前記所定期間の後、前記一つの出力端子と前記第2の給電端子間の電流経路の切断を解除する制御を行う手段を備え、前記第1及び第2の出力端子の出力振幅は、前記第1及び第2の入力信号の振幅よりも大きい。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】スイッチ部と、駆動回路と、電源回路と、を備えた半導体スイッチが供給される。前記スイッチ部は、共通端子と複数の高周波端子との接続を切り替える。前記駆動回路は、端子切替信号に基づいて前記スイッチ部に制御信号を出力する。前記電源回路は、温度に応じて変化する基準電位基づいて、前記制御信号の電位であって温度制御された第1の電位を生成して前記駆動回路に出力する。

(もっと読む)

ゲート駆動回路

【課題】過電流や短絡発生時に絶縁ゲート型トランジスタへの遮断の遅延を抑制し、安全に絶縁ゲート型トランジスタを保護できるゲート駆動を提供する。

【解決手段】対を成すNPNトランジスタ15、PNPトランジスタ17によるトーテムポール回路9に駆動信号が入力され、回路9の出力が絶縁ゲート型トランジスタ3のゲート3Aに接続され、トランジスタ3のゲート3Aの電位を下げて保護動作をする保護回路11が備えられたゲート駆動回路1であって、トーテムポール回路9のトランジスタ15、17ごとに独立して設けられて駆動信号をベース15A、17Aに入力するベースライン29A、29Bと、保護回路11の保護動作の間、トーテムポール回路9の上アーム側のトランジスタ15のベース電位を下げる電位強制低下回路13と、を備える。

(もっと読む)

高周波スイッチ回路、及び複合高周波スイッチ回路

【課題】 ゲート−ボディ間の電圧がMOSFETの耐圧以下とすることが可能な高い信頼性を有する高周波スイッチ回路を実現する。

【解決手段】 MOSFETと、前記MOSFETのゲート及びボディの電位を制御可能な制御回路を備えた高周波スイッチ回路であって、

前記制御回路はタイミング制御回路を備え、

前記タイミング制御回路は、前記高周波信号経路が接続状態から非接続状態に切り替わる時は、前記MOSFETのゲートの電位を切り替えた後にボディの電位を切り替えることが可能であり、かつ、非接続状態から接続状態に切り替わる時は、前記MOSFETのボディの電位を切り替えた後にゲートの電位を切り替えることが可能であることを特徴とする。

(もっと読む)

半導体装置

【課題】ハーフブリッジ回路のメインスイッチング素子が同時オンになることを確実に防止する。

【解決手段】ローサイド側の入力信号を遅延させてローサイド側遅延信号として出力する遅延回路20と、ハイサイド側の入力信号からハイサイド側セット出力信号と予備リセット信号とを生成して出力するパルス発生回路12と、ローサイド側の入力信号がアクティブになってからローサイド側遅延信号がアクティブになるまでの期間、又は予備リセット信号がアクティブである期間にハイサイド側リセット出力信号をアクティブにするリセット信号生成回路30と、を備えるハーフブリッジドライバとする。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

表示装置

【課題】表示装置の走査信号線の駆動回路において、走査信号線の出力波形なまりを改善し、表示品質を高めた表示装置を提供する。

【解決手段】表示装置は、複数の信号線Gnに対して、順に画素トランジスタを導通させる電位であるアクティブ電位を印加する駆動回路210を備え、前記駆動回路210は、前記複数の信号線のうちの一の信号線である出力信号線の一端に、より上位の前記出力信号線において出力されるアクティブ電位が入力されることに起因して、クロック信号を印加してアクティブ電位を出力させる主駆動回路240と、前記出力信号線の他端、及び前記クロック信号の信号線が、ソース/ドレインを介して接続されたトランジスタである補助トランジスタを含む補助駆動回路250と、を有する。

(もっと読む)

高周波スイッチモジュール

【課題】スイッチポート切替時間が短く、かつ低消費電力、低面積を同時に満たす高周波スイッチモジュールを提供する。

【解決手段】デコーダ3は、前記スイッチポートを切替える制御信号CNTに応答し、スイッチ7を制御するためのスイッチ制御信号SWCNTを生成して、スイッチ切替タイミング検出器は、スイッチ制御信号SWCNTに応答し、スイッチ切替え検出信号t_swを生成し、周波数制御信号生成器は、スイッチ切替え検出信号t_swに応答し、周波数制御信号ICONT、CCONTを生成し、負電圧発生回路は、周波数制御信号ICONT、CCONTに応答し、前記負電圧発生回路内で生成したクロック信号の周波数を2つ以上のそれぞれ異なる周波数に切替つつ、負電圧出力信号NVG_OUTを生成し、スイッチ7は、スイッチ制御信号SWCNTと前記負電圧出力信号NVG_OUTに応答し、複数の高周波信号ポート間の経路を切替える。

(もっと読む)

デジタル入力回路およびシステム監視回路

【課題】消費電力を低減させることを目的とする。

【解決手段】デジタル入力回路の分圧回路11において、システム4からの入力信号が伝搬する信号ラインL1から分岐される分岐ラインL2にスイッチング素子23を設け、このスイッチング素子23をマイクロコントローラ3の動作タイミングに応じてオンオフ制御する。これにより、スイッチング素子23がオフとされている期間において、分圧回路11に流れる電流を遮断でき、消費電力を低減させることが可能となる。

(もっと読む)

パルス生成回路、パルス生成方法、走査回路、表示装置、及び、電子機器

【課題】自身の回路動作によって所望の遷移速度のパルス信号を生成可能なパルス生成回路、その生成方法、パルス生成回路を用いる走査回路、当該走査回路を用いる表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】2つの電源の間に直列に接続され、入力パルスの論理に応じて相補的にオン/オフ動作を行う2つのスイッチ素子を有し、パルス消滅時に所望の遷移速度のパルス信号を生成するパルス生成回路において、2つの電源のうち、入力パルスと同じ極性側の一方の電源を固定の電源電圧とし、他方の電源を複数の電源電圧間で切り換え可能とする。

(もっと読む)

パワーオンリセット回路

【課題】パワーオン時における回路電源電圧の変化の緩急に拘らず、非動作電圧から動作電圧へ変化時にリセット信号を確実に出力するパワーオンリセット回路を提供する。

【解決手段】本発明に係るパワーオンリセット回路は、回路電源電圧を受けて充電を行う充電回路と、回路電源電圧を受けて出力電圧を出力する動作電圧設定回路と、前記充電回路の出力する充電電圧、及び、前記動作電圧設定回路の出力する出力電圧を判定して、パワーオンリセット信号を出力する電圧判定回路とを備える。

(もっと読む)

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

1 - 20 / 258

[ Back to top ]