Fターム[5J055AX58]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | 課題の発生する時、注目している時 (638) | 電源の不安定時、瞬断時、遮断時 (54)

Fターム[5J055AX58]に分類される特許

1 - 20 / 54

電圧検出回路

自動回復回路付き制御IC、制御ICの自動回復回路、パワ変換システム及び制御ICの自動回復方法

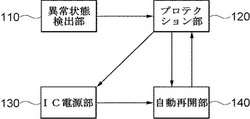

【課題】予備電源を備えなくても、制御ICが保護モードにて出力以外に自動復元の動作を行って、一定時間後自動に正常動作する。

【解決手段】システムまたは制御ICの異常状態を検出する異常状態検出部110と、異常状態の検出に応じて、保護モードに変更し、該保護モードにて自動回復信号を入力されて動作モードに変更するプロテクション部120と、入力電源からの電力の供給後、IC電源が予め決められた高電圧に到達すると、電力供給遮断信号に応じて入力電源からの電力の供給を遮断し、入力電源からの電力の供給及び遮断を繰り返すIC電源部130と、保護モードの開始に応じて、IC電源部130の電力供給信号及び電力供給遮断信号が交互に繰り返されるクロックをカウントし、該カウント数が予め決められた値に到達すると、プロテクション部120に自動回復信号を供給する自動再開部140とを含む。

(もっと読む)

低電圧検出回路

【課題】 電源電圧が所定の電位以上になって所定時間後に出力が解除状態になった後は定電流源の電流を流さないようにして消費電流を抑える遅延付き低電圧検出回路を実現する。

【解決手段】 電圧比較回路(13)により検出対象の電圧が所定の電圧値以下になったことを検出した場合には出力状態を直ちに変化させ、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には電流回路(14)により決まる遅延時間後に出力状態を変化させる低電圧検出回路において、電流回路は、電圧比較回路により検出対象の電圧が所定の電圧値以下になったことを検出した場合には、定電流源の電流を遮断する状態とし、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には、定電流源の電流を流す状態として電流回路によるコンデンサの充電を開始させ所定遅延時間後に定電流源に流れる電流を遮断するように構成した。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

電源電圧検出回路

【課題】低電圧状態を検出し、システムへの通知やシステムの停止等を行う電源電圧検出回路において低電源電圧時の誤動作を回避する電源電圧検出回路を提供する。

【解決手段】基準電圧Vrefを生成する回路200の出力にプルアップ回路250を設け、基準電圧Vrefを生成する回路200を電源電圧VE(100)までプルアップする。さらに、R1(341),R2(342)から成る検出抵抗に直列にスイッチS1(347)を設け、基準電圧Vrefを生成する回路200によって、上記スイッチS1(347)をオン/オフする。そうしておいて低電源電圧時に上記プルアップ回路250により基準電圧Vref(225)を上記電源電圧VE(100)までプルアップさせると共に、上記スイッチS1(347)をオフし分圧値VI(345)を強制的に低下させることで、Vref>VIの状態を保持し、比較器330からの誤信号出力を回避する。

(もっと読む)

リセット回路

【課題】減電検出を利用して確実にリセットを掛ける。

【解決手段】整流電圧V+をレギュレータ24にてレギュレートした定電圧3.3Vを駆動電圧とされるマイコン30のリセット端子に接続される端子2と抵抗R1を介して定電圧3.3Vを入力される端子4とを備え、端子4の入力電圧が第1閾値を下回るとマイコン30にリセット信号を出力するリセットIC12と、抵抗R2を介して端子4にコレクタを接続され、エミッタをグランドに接続され、スイッチングトランス21の出力が所定レベルを下回るとオンするように構成されたトランジスタQ1と、を備え、トランジスタQ1がオンすると端子4に第1閾値を下回る電圧を入力する。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

電力制御器システム

【課題】落雷などの故障過渡電流が流れる間はスイッチング装置を開いて過電流が流れるのを防止する一方、その間、負荷電流が中断されない電力制御器システムを提供する。

【解決手段】電力制御器システム10は、電気経路31内に設けられた、負荷20に電流を供給するスイッチング装置30を備える。スイッチング装置30の両端間の電圧または電流が所定のレベルを超えたとき、制御器50がスイッチング装置10を開くように構成する。スイッチング装置30が開いているときも、並列電気経路60を負荷に接続する回路11内の誘導素子32に蓄積された誘導エネルギーの放散により、負荷電流61が並列電気経路60および負荷20に流れ続ける。

(もっと読む)

減電圧リセット回路及びこれを用いた電源装置

【課題】より確実に安定した減電圧監視を行うことが可能な減電圧リセット回路及び電源装置を提供する。

【解決手段】減電圧リセット回路15は、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第1トランジスタ153と、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第2トランジスタ154と、監視対象電圧V1の供給を受けて動作し、監視対象電圧V1が第1閾値電圧を下回っているときに第1トランジスタ153をオンさせる第1監視部151と、監視対象電圧V1とは異なる駆動電圧V0の供給を受けて動作し、監視対象電圧V1が第1閾値電圧よりも低く第1監視部151の下限動作電圧よりも高い第2閾値電圧を下回っているときに第2トランジスタ154をオンさせる第2監視部152と、を有する。

(もっと読む)

活線挿抜制御回路

【課題】解除電圧のばらつきを低減した活線挿抜制御回路を提供する。

【解決手段】実施形態によれば、出力回路と、電圧発生回路と、検出回路と、補正回路とを備えた活線挿抜制御回路が提供される。前記出力回路は、活線挿抜基板に設けられた半導体装置の出力信号を電源電圧が解除電圧以下のときディスエーブルに切替え、前記電源電圧が前記解除電圧よりも高いときイネーブルに切替えることのできるイネーブル信号を生成する。前記電圧発生回路は、前記電源電圧が供給されるMOSFETを含み、前記電源電圧に応じて変化し前記解除電圧を検出する基準となる第1の電圧を発生する。前記検出回路は、前記第1の電圧を検出する。前記補正回路は、前記検出回路の出力に応じて前記第1の電圧を一定値に補正する。

(もっと読む)

電圧検出回路、及び電源装置

【課題】瞬停の度に電力を遮断せずともリセット用コンデンサを確実に放電可能とする。

【解決手段】スイッチング制御回路5への入力電圧の降下を検出し、当該スイッチング制御回路5に設けられたリセット用コンデンサC2を放電する放電回路55を作動させる電圧検出回路53であって、前記入力電圧の降下検出後の復電時から所定時間Ta後に電圧が復電判定値Vrに至る比較用信号を前記入力電圧から生成し、前記入力電圧の降下検出時から前記比較用信号の電圧が前記復電判定値Vrを超えるまで前記放電回路55の作動を継続して前記リセット用コンデンサC2を放電するようにした。

(もっと読む)

半導体集積回路

【課題】回路部が停止状態から動作状態に移行するときに、チップ内電源に対する電圧降下を低減すること。

【解決手段】動作期間T10で、回路部210内の寄生容量221の電位とデカップリング容量220の電位は、チップ内電源201の電位に維持され、停止期間T11で、寄生容量221の電位は徐々に降下してゼロになり、デカップリング容量220の電位はチップ内電源201の電位に維持される。移行期間T12〜T14で、デカップリング容量220の電位が第2スイッチSW2を介して寄生容量221に充電され、デカップリング容量220の電位は徐々に降下し、寄生容量221の電位は徐々に上昇していく。移行期間T12〜T14で、回路部210の電位がゼロの状態であるときに、回路部210が第1スイッチSW1を介してチップ内電源201と接続しないようにすることで、チップ内電源201に対する電圧降下を低減することができる。

(もっと読む)

半導体集積回路

【課題】常時電源オン回路領域の電源が先に遮断されても電源オフ回路領域に悪影響を及ぼすことを防止する半導体集積回路を提供する。

【解決手段】第1電源から電力供給される回路領域である電源オンドメインと、第2電源から電力供給される回路領域である電源オフドメインとを同一チップ上に備え、電源オンドメインは、第1電源がオンかつ第2電源がオフであるときに電源オフドメインと電源オンドメインとの間で入出力される信号を遮断する第1信号遮断部と、第2信号遮断部の遮断を有効または無効にする旨を示す第1制御信号を出力する遮断制御部とを備え、電源オフドメインは、遮断制御部からの遮断を有効にする旨を示す第1制御信号に基づき、電源オンドメインと電源オフドメインとの間で入力される信号を遮断する第2信号遮断部を備え、前記遮断制御部は、第1電源からの電源供給の停止を検出したとき、遮断を有効にする旨を示す第1制御信号を出力する。

(もっと読む)

半導体装置およびシステム

【課題】 電源電圧が低下するときに、半導体装置の内部ノードを確実に初期化する。

【解決手段】 第1トランジスタは、電源電圧が供給される第1電源線に一端とゲートとが接続され、他端が第1ノードに接続される。第2トランジスタは、第2ノードにゲートが接続され、一端が第1ノードに接続され、他端が第3ノードに接続される。第3トランジスタは、第2電源線に一端が接続され、ゲートが第4ノードに接続され、他端が第3ノードに接続される。第1バイアス電圧生成回路は、第2ノードに第1バイアス電圧を供給する。第2バイアス電圧生成回路は、第4ノードに第2バイアス電圧を供給する。これにより、第3ノードが、あるレベルから別のレベルに変化するときの電源電圧を高く設定でき、電源電圧が低下するときに、第3ノードの電圧の変化に応じて半導体装置の内部ノードを確実に初期化できる。

(もっと読む)

半導体メモリの内部電源のスタートアップ回路

【課題】電源の遮断時に残留電位を速やかに放電することができる半導体メモリの内部電源のスタートアップ回路を提供する。

【解決手段】放電回路40が、放電用のNMOSトランジスタN4〜N6、電位補償用のNMOSトランジスタN7、及びカップリング容量により配線Gの電位を引き下げるDMOSトランジスタD2を含んで構成されている。電源電圧VCCの遮断時に、DMOSトランジスタD2及びNMOSトランジスタN7により配線Gの電位がマイナス電位に引き下げられ、NMOSトランジスタN4〜N6が動作して、配線D、E、Fの残留電荷を引き下げ、放電する。

(もっと読む)

半導体装置

【課題】消費電力が少なく、かつ電源電圧の変動に対する応答性に優れたパワーオンリセット回路を備えた半導体装置を提供する。

【解決手段】レベルシフタLS40は、第1の電源電圧VDD1が供給される電源端子に接続された電圧降下回路(抵抗素子R40)と、電圧降下回路と接地電圧端子の間に接続されたPチャネル型MOSトランジスタM41及びNチャネル型MOSトランジスタM40により、構成される。また、レベルシフタLS40の入力端子は、電源電圧VDD2に対応したパワーオンリセット回路POR11の出力端子であるノードN40へ接続される。電圧降下回路とPチャネル型MOSトランジスタM41の共通ノードの電圧値は、ノードN40の電圧値よりもPチャネル型MOSトランジスタM41の閾値電圧の絶対値分だけ常時高いことを特徴とする。

(もっと読む)

トレラントバッファ回路及びインターフェース

【課題】出力端子が出力回路の電源電圧より高電位である場合や、出力回路の電源電圧が0Vになっても出力端子から電源電圧へ電流の逆流入は発生しないトレラントバッファ回路及びインターフェースを提供すること。

【解決手段】トレラントバッファ回路100は、電源端子VDD1と出力端子102の間にソースを共有して直列接続されたPチャンネルMOSトランジスタQ111,Q112と、出力端子102と接地端子の間に接続されたNチャンネルMOSトランジスタQ113と、PチャンネルMOSトランジスタQ111のゲートに出力接続されたインバータ121と、PチャンネルMOSトランジスタQ112のゲートに出力接続されたインバータ122と、各MOSトランジスタQ111、Q112、Q113にそれぞれ第1、第2及び第3の制御信号を出力してこれらのMOSトランジスタのオン・オフを制御する制御回路130とを備える。

(もっと読む)

半導体回路

【課題】できるだけ小規模の回路で、電源電圧の投入時または一時的な低下時に信号の出力を確実かつ十分な時間遮断することができる半導体回路を提供する。

【解決手段】半導体回路10Aは、パワーオンリセット回路30と、遅延回路16と、第1、第2の遮断回路18,19とを備える。パワーオンリセット回路30は、電源電圧VCCの投入時または一時的な低下時に活性状態であり、電源電圧VCCが所定の電圧を超えた後に非活性状態になるリセット信号POROUTを生成する。第1の遮断回路18は、遅延回路16に入力される制御信号CTL1の経路上に設けられ、リセット信号POROUTが活性状態の間、制御信号CTL1を遮断する。第2の遮断回路19は、遅延回路16から出力される制御信号CTL1の経路上に設けられ、リセット信号POROUTが活性状態の間、制御信号CTL1を遮断する。

(もっと読む)

負荷電圧を供給するためのドライバ回路

負荷(104)に給電を行うための負荷電圧を供給するドライバ回路(100)であって、前記負荷(104)はとりわけ車両の負荷であり、当該ドライバ回路(100)は、給電電圧を供給するための給電電圧源(UB)と、電気エネルギーを一時蓄積するために一時蓄積ユニット(101)とを有し、前記一時蓄積ユニット(101)は、前記電気エネルギーを供給するための給電電圧源に接続されており、当該ドライバ回路(100)はさらに、前記給電電圧が電圧降下した場合に前記負荷(104)に前記負荷電圧が供給されるように、前記一時蓄積ユニット(101)によって必要に応じて前記電気エネルギーが供給されるドライバユニット(105)を有することを特徴とする、ドライバ回路(100)。  (もっと読む)

(もっと読む)

1 - 20 / 54

[ Back to top ]