Fターム[5J055DX17]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442) | 閾値 (83) | バックゲートを利用 (23)

Fターム[5J055DX17]の下位に属するFターム

能動素子を接続

Fターム[5J055DX17]に分類される特許

1 - 20 / 23

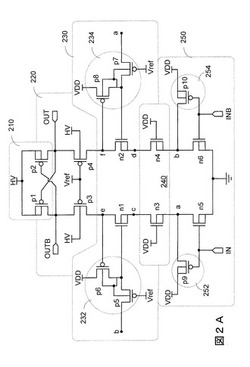

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

ESD保護回路

【課題】ESDパルスをもれなく検出し、かつ通常の電源投入時やスパイクノイズ印加時の誤検出を抑制する。

【解決手段】第1検出回路7はESDパルスの印加開始時から第1所定時間だけ第1検出信号を出力する。第2検出回路9は、第1検出信号を受け、かつESDパルスの印加が第2所定時間だけ持続したときに第3所定時間だけ第2検出信号を出力する。第1所定時間は電源の立ち上がり時間よりも短い。第2所定時間は第1所定時間よりも短く、かつスパイクノイズの印加時間よりも長い。第3所定時間はESDパルスの印加時間よりも長い。クランプ回路11は、第1検出信号及び第2検出信号の少なくとも一方が出力されているときはゲート端子47をGND端子3とは絶縁する。プルアップ回路13は、ゲート端子47を、第2検出信号が出力されているときは電源端子1に接続し、第2検出信号を出力されていないときは電源端子1とは絶縁する。

(もっと読む)

高周波スイッチ

【課題】高周波スイッチの歪特性の劣化を抑止することができる高周波スイッチを提供する。

【解決手段】アンテナ110へ送信信号が出力される共通ポートCXと、送信信号が入力される送信ポートTX1、TX2と、複数の送信ポートと共通ポートとの間にそれぞれ接続され、各送信ポートから共通ポートへの送信信号を導通または遮断する複数のスイッチ部100A、100Bと、を有し、スイッチ部はシリコン基板に形成された一以上のMOSFETTSWを有し、MOSFETのうち共通ポートに接続されたもののボディ端子と共通ポートに接続された端子との間にキャパシタが接続される。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

半導体集積回路

【課題】 ゲート酸化膜の信頼性を維持しながら、待機時のリーク電流を抑制でき、回路面積の増加を最小限にでき、欠陥を確実に検出することができる半導体集積回路を実現する。

【解決手段】 論理回路10と電源電圧Vddの供給端子との間にスイッチング回路20を設ける。動作時に、スイッチング回路20のトランジスタMP0のゲートに0Vの電圧を印加し、チャネル領域に電源電圧Vddと同じかまたは僅かに低いバイアス電圧VBを印加することで、トランジスタMP0のしきい値電圧を低くし、その電流駆動能力を大きくする。待機時にトランジスタMP0のゲートに電源電圧Vddと同じ電圧を印加し、ソースに電源電圧より低い電圧を印可し、チャネル領域に電源電圧Vddと同じかまたはそれより高いバルクバイアス電圧VBを印加し、トランジスタMP0のドレイン電流を最少化することにより、論理回路10の電流経路を遮断し、リーク電流の発生を抑制する。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

負荷駆動装置

【課題】従来の負荷駆動装置は、電源が正常に接続された場合の待機時において消費電流が増大するという問題があった。

【解決手段】本発明にかかる負荷駆動装置は、電源端子PWRと出力端子OUTとの間に接続された出力トランジスタT1と、出力端子OUTと接地端子GNDとの間に接続された負荷11と、出力トランジスタT1のゲートと接地端子GNDとの間に設けられ、電源11の極性が逆になった場合に出力トランジスタT1を導通状態にする保護トランジスタMN3と、電源10の極性が正常の場合に接地端子GNDと保護トランジスタMN3のバックゲートとを導通状態に制御するバックゲート制御回路17と、を備える。

(もっと読む)

半導体装置及びその耐圧制御方法

【課題】従来の半導体装置では、チップ面積を小さくすることができない問題があった。

【解決手段】本発明の半導体装置は、第1の電圧VHと、第1の電圧VHよりも低い第2の電圧VLと、第1の電圧VHと第2の電圧VLとの間の第3の電圧VMとに基づき動作する半導体装置であって、第2の電圧VLから第1の電圧VHに至る振幅を有する信号がゲートに入力されるトランジスタを少なくとも1つ含む出力回路20と、出力回路20に含まれるトランジスタのゲートの電圧を制御する第1の制御信号と、トランジスタのバックゲート領域の電圧を制御する第2の制御信号と、ディープウェル領域の電圧を制御する第3の制御信号と、を生成する制御回路10と、を有し、制御回路10は、第1の制御信号と第2の制御信号との電圧差を第1の電圧VHと第3の電圧VMとの電圧差及び第2の電圧VLと第3の電圧VMとの電圧差のうち大きな電圧差以下とする。

(もっと読む)

カップリング回路、このカップリング回路を含むドライバ回路、およびこのカップリング回路の制御方法

【解決手段】p−チャネル電界効果トランジスタタイプの第1および第2のトランジスタ(P1,P2)を備えるカップリング回路において、第1のトランジスタ(P1)のドレイン端子は信号入力端子(1)に接続し、第1および第2のトランジスタ(P1,P2)のソース端子はともに信号出力端子(2)に接続し、第1および第2のトランジスタ(P1,P2)のバルク端子はともに第2のトランジスタ(P2)のドレイン端子に接続し、第1のトランジスタ(P1)のゲート端子は第2のトランジスタ(P2)のゲート端子に接続する。このカップリング回路には、さらに 負電圧を生成する電荷ポンプ回路(110)を含むゲート制御回路(10)も設ける。このゲート制御回路(10)は、負電圧に基づいて、第1および第2のトランジスタ(P1,P2)のゲート端子におけるゲート電圧を制御する。 (もっと読む)

チャージポンプ回路

【課題】チャージポンプ回路の出力電圧と所望の電圧との差を小さくすることにより、回路の電力効率を向上させる。

【解決手段】このチャージポンプ回路は、入力端子と出力端子の間に直列接続された複数のスイッチング素子と、前記入力端子に入力電圧を供給する電圧源と、前記複数のスイッチング素子の接続点に一端が接続されたコンデンサと、前記コンデンサの他端にクロックパルスを供給するクロックドライバーと、を具備し、前記出力端子から正の昇圧電圧を出力するチャージポンプ回路であって、前記クロックドライバーの中でクロックドライバーCDV1が前記入力電圧を供給する電圧源と、当該入力電圧より低い電圧からなる電圧源の間に接続されており、他のクロックドライバーが前記入力電圧を供給する電圧源と接地電位との間に接続されている事を特徴とする。

(もっと読む)

二重絶縁ゲート型電界効果トランジスタを用いたゲート回路、SRAMセル回路、多入力CMOSゲート回路、CMOS−SRAMセル回路、集積回路

【課題】高速動作と消費電力の減少を両立させた二重絶縁ゲート型電界効果トランジスタを用いた回路を提供する。

【解決手段】第一の四端子二重絶縁ゲート電界効果トランジスタは、一方のゲートを入力端子、ソースを第一の電源に接続し、ドレインを出力端子、該ドレインを負荷素子を介して第四の電源に接続し、他方のゲートに第一の三端子絶縁ゲート電界効果トランジスタのドレインを接続し、前記第一の三端子絶縁ゲート電界効果トランジスタは、ソースを第二の電源に接続し、ゲートを第三の電源に接続し、前記三端子絶縁ゲート電界効果トランジスタのドレインとソースの間の抵抗と前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートと他方のゲートの間のゲート絶縁膜容量と前記両ゲートに挟まれた半導体の容量で微分回路を構成したゲート回路で、前記第一の四端子二重絶縁ゲート電界効果トランジスタの一方のゲートと他方のゲート間を容量で接続する。

(もっと読む)

スイッチ装置

【課題】 双方向スイッチの低コスト化及び高耐圧化が要求されている。

【解決手段】 双方向スイッチ機能を有するスイッチ装置10は、第1及び第2の主端子11,12と、HEMT構成のノーマリオン型主半導体スイッチング素子13と、第1の主端子11と主半導体スイッチング素子13の第1の主電極20との間に接合された低耐圧ノーマリオフ型の第1のMOSFET14と、第2の主端子12と主半導体スイッチング素子13との間に接続された低耐圧ノーマリオフ型の第2のMOSFET15と、第1及び第2のMOSFET14,15に逆方向並列に接続された第1及び第2のダイオード16,17と、主半導体スイッチング素子13のゲート電極22と第1及び第2の主端子11,12との間に接続された第3及び第4のダイオード18,19とを有する。このスイッチ装置10はノーマリオフ特性を有する。

(もっと読む)

ディスチャージ回路

【課題】ディスチャージトランジスタのゲート電圧が、電源電圧、温度、及びプロセスの変動の影響を受け難く、常に所定の値を保つことができる設計容易なディスチャージ回路を提供する。

【解決手段】一端がディスチャージノードAに接続され、他端がグランドに接続され、ゲートがバイアス電圧Vgに接続されたNMOSトランジスタ11を有するディスチャージ部10と、ゲートにバイアス電圧Vgを供給するバイアス電圧発生部20と、一端とゲートとがディスチャージ部10のNMOSトランジスタのゲートに接続され、他端がディスチャージノードAに接続されたMOSトランジスタ31を有するクランプ部30とを有し、クランプ部30は、ディスチャージ部10のNMOSトランジスタ11のゲートに印加されるバイアス電圧を所定の値にクランプする。

(もっと読む)

アナログスイッチ

【課題】 低容量なアナログスイッチを実現すること。

【解決手段】 アナログスイッチの入出力端であるTERM1の電位とTERM2の電位とNMOSスイッチ素子のウェル電位とゲート電位をレベルシフトバッファ2及び3を介して同期して動作させることによりそれぞれの間にある寄生容量をキャンセルする。

(もっと読む)

高周波スイッチ回路

【課題】寄生容量による信号漏れを抑制する。

【解決手段】高周波スイッチ回路30には、Nch MOSトランジスタMT1乃至4、抵抗R1乃至9、共通RF端子PRFCOM、RF端子PRF1、RF端子PRF2、制御端子PVCON1、及び制御端子PVCON2が設けられる。Nch MOSトランジスタMT1のバックゲート側に設けられる抵抗R2は、他端が共通RF端子PRFCOM側に接続される。Nch MOSトランジスタMT2のバックゲート側に設けられる抵抗R4は、他端が共通RF端子PRFCOM側に接続される。Nch MOSトランジスタMT3のバックゲート側に設けられる抵抗R6は、他端がRF端子PRF1側に接続される。Nch MOSトランジスタMT4のバックゲート側に設けられる抵抗R8は、他端がRF端子PRF2側に接続される。高周波スイッチ回路30では、信号線と接地線が交差する部分がない。

(もっと読む)

スイッチ回路、可変コンデンサ回路およびそのIC

【課題】 単一の低い電圧で動作が可能なスイッチ回路を提供する。

【解決手段】 第1の端子T1が、コンデンサC11を通じて、バックゲートが分離されたMOS−FET(Q11)のドレイン(あるいはソース)に接続される。MOS−FET(Q11)のソース(あるいはドレイン)が第2の端子T2に接続される。バックゲートがソース(あるいはドレイン)に接続される。MOS−FET(Q11)のゲートに制御電圧VGが供給されるとともに、この制御電圧VGの極性を反転した電圧が抵抗素子R12を通じてドレインに供給される。

(もっと読む)

3値論理インバータ回路

【課題】少数のMOSで構成することができ、基板電流を回避することができる、3値論理インバータ回路を提供すること。

【解決手段】第1から第4のMOSを備え、第1から第4のMOSのゲート端子に、共通の入力信号を入力可能とし、第1のMOS及び前記第3のMOSにおける、サブストレート端子を第1の基板電圧に接続すると共に、ソース端子を第1の信号電圧に接続し、第2のMOS及び前記第4のMOSにおける、サブストレート端子を第2の基板電圧に接続すると共に、ソース端子を第2の信号電圧に接続し、第3のMOSのドレイン及び第4のMOSのドレインを相互に接続すると共にこの接続点を第2のMOSのソース端子に接続し、あるいは、第1のMOSのドレイン及び第2のMOSのドレインを相互に接続すると共にこの接続点を第3のMOSのソース端子に接続した。

(もっと読む)

半導体回路

【課題】 簡単なバルク電位制御の回路構成で回路面積の増大を防ぐことができ、MOSトランジスタのしきい値電圧の絶対値を調整することができると共にしきい値電圧のばらつき幅を低減させることができ、安定した低電圧動作を行うこと。

【解決手段】 しきい値電圧を制御したいトランジスタT2のバルク端子bを、同しきい値電圧を有し、ゲート端子gとドレイン端子dを短絡したダイオード接続型のトランジスタT1のゲート端子gと接続することで、しきい値電圧に応じたバルク電位を発生させ、しきい値の絶対値及びばらつき幅を抑制することを可能とする。

(もっと読む)

半導体集積回路

【課題】ウェルおよび深層ウェルの電位を半導体集積回路の電位と分離して、他の回路が発生するノイズ伝播を抑制する。

【解決手段】P型MOSトランジスタのバルクにはインバータ回路のVDDパッド15と分離したバルク専用パッド17、また、N型MOSトランジスタのバルクにもインバータ回路のVSSパッド16と分離したバルク専用パッド18を設ける。VDDパッド15,VSSパッド16は他の回路とも共通で、他の回路にノイズ発生源がある場合、VDDパッド15,VSSパッド16を経由する。バルク専用パッド17,バルク専用パッド18は、VDDパッド15,VSSパッド16と分離され、また、それぞれのパッドまでの配線に配線抵抗19が存在しており、各MOSトランジスタのバルクに他の回路が発生するノイズが伝播することを抑制できる。

(もっと読む)

トレラント入力回路

【課題】 入力回路のしきい値を調整することなく、製造ばらつきに関わらず安定して動作するトレラント入力回路を提供する。

【解決手段】 入力パッド1と入力回路2との間にNチャネルMOSトランジスタにてなる降圧素子Tr3を介在させ、降圧素子Tr3のゲートに入力回路の電源VDDを供給して、入力パッド1に入力される高電圧信号を、電源VDD電圧以下に降圧して入力回路2に供給するトレラント入力回路であって、入力パッド1に高電圧信号が入力されたとき、降圧素子Tr3のバックゲート電圧を上昇させるバックゲート電圧制御回路を備えた。

(もっと読む)

1 - 20 / 23

[ Back to top ]