Fターム[5J055DX28]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 光入力を有する素子 (22)

Fターム[5J055DX28]の下位に属するFターム

フォトトランジスタ、フォトカプラ (14)

フォトサイリスタ、LIT

Fターム[5J055DX28]に分類される特許

1 - 8 / 8

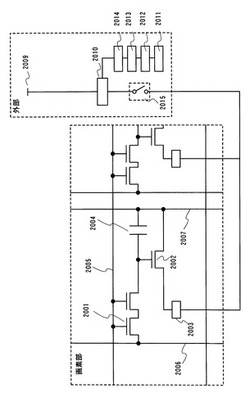

半導体装置

【課題】発光装置に含まれる発光素子の発光輝度を周囲の情報に応じて調節する表示シス

テムを提供する。

【解決手段】本発明において、センサー2011が周囲の情報を電気信号として検出し、

これをCPU2013は、あらかじめ設定しておいた比較データに基づきEL素子の発光

輝度を補正するための補正信号に変換する。この補正信号が電圧可変器2010に入力さ

れることにより、電圧可変器2010が所定の補正電位をEL素子に印加する。以上の表

示システムによりEL素子2003の発光輝度を制御することができる。

(もっと読む)

電力変換装置のゲート制御回路

【課題】直列接続されたスイッチング素子の直流短絡事故などを防止するとともに、ゲートパルス信号用のライトガイドの本数を削減する。

【解決手段】直列接続されたスイッチング素子を駆動するゲート駆動回路と、このゲート駆動回路に与える基準信号を発生し、インターロック手段を備えたゲート信号発生手段と、このゲート信号発生手段から光伝送された信号を受光してゲート駆動回路に分配する光分配回路と、この光分配回路の出力をゲート駆動回路に夫々供給する手段と、ゲート駆動回路の出力を監視し、光分配回路にフィードバックするゲート信号監視手段と、ゲート信号監視手段のフィードバック信号が全てオフ状態であればオフ、1つでもオンであればオンとみなす論理演算手段と、論理演算手段の出力を光変換してゲート信号発生手段に供給する伝送手段とで構成する。この伝送手段の出力を、インターロック手段のインターロック条件に反映させる。

(もっと読む)

光電センサユニット

【課題】複数の機能を備える光電センサユニットにおいてユーザの用途やワークに応じた設定を容易に設定可能とすることで、光電センサユニットが有する能力を適切に引き出すことができる光電センサユニットを提供すること。

【解決手段】検出機能及び表示機能を定める複数の設定パラメータの設定内容を初期化する通常の初期化処理を実行する通常初期化モードと、ユーザの用途に応じて一部の設定パラメータを推奨される設定内容に変更した上で、残りの設定パラメータを初期化する特別初期化モードのいずれかを選択する設定画面を表示し、特別初期化処理が実行されると、複数の設定パラメータの組み合わせが推奨される設定内容に自動的に設定される。

(もっと読む)

半導体集積回路

【課題】電源起動時のリーク電流によるトランジスタの誤作動を防止することが可能な半導体集積回路を提供すること。

【解決手段】発明にかかる半導体集積回路は、第1の制御信号を駆動回路120を介して出力する論理回路209と、コレクタが高電位側の電源電圧VCCに接続され、エミッタが出力端子VOUTに接続され、ベースに入力される第1の制御信号に応じてオンオフが制御されるNPN型バイポーラトランジスタ201をそなえる。また、一方の端子がベースと駆動回路210との間のノードに接続され、他方の端子が電源電圧及び接地電圧のいずれか一方に接続されたトランジスタスイッチ203と、第1のトランジスタスイッチに並列に接続された抵抗素子205とを備える。このような回路構成により、電源起動時のリーク電流によるトランジスタの誤作動を防止することができる。

(もっと読む)

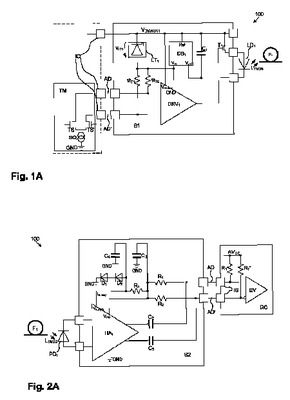

TMDS符号化信号を伝送する回路装置及び方法

少なくとも部分的に、特に少なくともタイムスロット方式でTMDS符号化され、且つ特に少なくとも1つのDVIデータ接続、及び/又は、少なくとも1つのHDMIデータ接続に割り当てられた信号を、少なくとも1つのデータソースから少なくとも1つのデータシンクへ安価に伝送する回路装置(100;100’)及び方法を提供するために、

駆動回路(S1;S1’)は、上流に接続され且つ前記データソースに割り当てられた少なくとも1つの接続インターフェース(IQ)によって、約5ボルトの供給電圧を含み、特に約55ミリアンペア以下でチャージすることができる、供給電圧(VDVI/HDMI)を供給されること、

前記駆動回路(S1;S1’)の下流に接続された少なくとも1つの発光素子(LD1)、特に少なくとも1つの光ダイオード、少なくとも1つの発光ダイオード、少なくとも1つのレーザダイオード、あるいは少なくとも1つの半導体レーザを含む少なくとも1つのレーザによって、電気的なTMDS符号化信号を電気−光変換して、前記TMDS符号化信号を与えられた光(LTMDS)として、少なくとも1つの光ファイバー(F1)、特に少なくとも1つのガラス繊維又は少なくとも1つのプラスチックファイバーを含む少なくとも1つのプラスチック材料繊維に、連結すること、

少なくとも1つのTMDSトランスミッタ(TM)からデータソースに割り当てられた前記接続インターフェース(IQ)へ供給される直流電流部分は、前記駆動回路(S1;S1’)によって前記発光素子(LD1)を制御する変調信号電流に変換されること、

前記TMDS符号化信号を与えられた前記光(LTMDS)は、少なくとも1つの光吸収素子(PD1)、特に少なくとも1つのフォトダイオードによって、前記光ファイバー(F1)から取り出されて、光−電気変換され、前記光吸収素子(PD1)の下流且つ前記データシンクに割り当てられた少なくとも1つの接続インターフェース(IS)の上流に接続された少なくとも1つのトランスインピーダンス変換回路(S2;S2’)に供給され、前記トランスインピーダンス変換回路(S2;S2’)は、少なくとも1つの差動ペア配線(AD、AD’)によって印加される直流電圧部分によって提供されることが提案される。  (もっと読む)

(もっと読む)

負荷を駆動する駆動方法および駆動装置、並びに電子機器

【課題】容量性リアクタンス負荷を低速トランジェントパルスで駆動する際、ばらつきや環境変動の影響を受けずに、適正な位相遅延量や傾き特性での駆動ができるようにする。

【解決手段】位相遅延制御部672で、負荷電圧の入力パルスPinに対する遅延量を監視し、遅延量が仕様に合致するように、遅延量制御信号P72を遅延クロック数レジスタ614に供給してパルス遅延部612での遅延量を制御する。スルーレート制御部674で、負荷電圧のスルーレートを監視し、スルーレートが仕様に合致するように、スルーレート制御信号P74をDACデータレジスタ638に供給してDA変換器634から出力される前段駆動信号P30を制御する。実動状態の負荷電圧を監視して、遷移特性が仕様に合致するようにフィードバック制御を実施するので、ばらつきや環境変動があっても、常に一定の遷移特性が得られる。

(もっと読む)

通信制御装置及びその機能ユニット

【目的】 装置の設置環境によらず常に安定な稼働が得られることを課題とする。

【構成】 通信制御機能を実現する複数の機能ユニット301〜30nと、該複数の機能ユニットにDC電源を給電する一次電源10と、各機能ユニットの立ち上げ状態を管理する管理ユニット40とを備える通信制御装置であって、機能ユニット30は、一次電源により給電されて所定のDC電圧を発生する二次電源33と、該二次電源により給電されて所定の機能を実現する論理回路部34と、一次電源により給電されて論理回路部の立ち上げ状態を検出・保持する実装検出保持部20であって、論理回路部34が二次電源の瞬断によりリセットされたことに伴いリセット(RS)され、かつ論理回路部が立ち上がったことにより再セット(RDY)されるもの、とを備える。

(もっと読む)

MOSFET駆動回路、プログラマブル電源及び半導体試験装置

半導体試験装置に使用されるプログラマブル電源において、電流レンジや出力リレーにおける大電流の高速切り換えを可能とする。

半導体試験装置1のプログラマブル電源10に設けられたスイッチ部20のMOSFET駆動回路22において、光絶縁素子22−1の受光部22−12からの電流によりコンデンサ部22−12に電荷が蓄積される。アナログスイッチ部22−3の切り換えによりSWAがON(SWBがOFF)となると、コンデンサ部22−12に蓄積されていた電荷によりMOSFET部21の各MOSFETのゲートがチャージされON状態となる。一方、アナログスイッチ部22−3のSWBがON(SWAがOFF)となると、MOSFETのゲートがディスチャージされる。

(もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]