Fターム[5J055DX53]の内容

Fターム[5J055DX53]に分類される特許

1 - 20 / 63

過電流検出回路および負荷駆動装置

【課題】回路用電源電圧としてむやみに高い電圧を用いることなく、シャント抵抗の低電位側端子の電圧がグランド電位付近となる異常が原因で生じる過電流を検出する。

【解決手段】検出電流出力部11は、シャント抵抗Rsの各端子電圧を入力し、その入力した電圧から負荷2に流れる電流に応じた検出電流を出力する。過電流判定部12は、検出電流に基づいて負荷2に過電流が流れているか否かを判定する。検出電流出力部11において、通常時に駆動用電源電圧Vdに近い電圧が印加される部分と、回路用電源電圧Vcに近い電圧が印加される部分との間の経路に第1ダイオードD1および第2ダイオードD2を逆方向に介在させることにより、第1トランジスタT1および第2トランジスタT2がブレークダウンして電流が流れることを阻止する。

(もっと読む)

半導体装置

【課題】スイッチング素子のターンオン直後における、過電流保護回路の誤動作防止と過電流検出遅れ防止とを両立させる。

【解決手段】半導体装置は、スイッチング素子1のセンス端子に流れるセンス電流を電圧(センス電圧)に変換するセンス抵抗4と、センス電圧が閾値を越えたときにスイッチング素子1の保護動作を行う過電流保護回路3とを備える。過電流保護回路3は、上記閾値を、第1基準電圧VREF1またはそれよりも低い第2基準電圧VREF2に切り替えることができる。過電流保護回路3は、スイッチング素子1が定常状態のときは、上記閾値を第2基準電圧VREF2とし、スイッチング素子1のターンオン直後のミラー期間のときは、上記閾値を第1基準電圧VREF1に設定する。

(もっと読む)

スイッチ素子駆動回路

【課題】グランド端子からグランド電位の供給を受けることなく、スイッチ素子をオン状態に維持することを可能とするスイッチ素子駆動回路を提供する。

【解決手段】本発明によるスイッチ素子駆動回路(100)は、電源と負荷との間に接続されたスイッチ素子を駆動するためのスイッチ素子駆動回路であって、前記電源と前記負荷との間に設けられた電圧降下素子(10)と、前記電圧降下素子の端子間に発生する電圧を動作電源として該電圧を昇圧し、該昇圧により得られた電圧から前記スイッチ素子を制御するための制御信号を生成する信号生成部(20)とを備える。

(もっと読む)

スイッチング素子の制御装置

【課題】実際に発生しているフライバックエネルギーを定量的に評価した上で保護動作を行うことができるスイッチング素子の制御装置を提供する。

【解決手段】NチャネルMOSFET2を介してコイル1に供給される電流をセンスMOSFET6及び検出用抵抗素子21により検出し、NチャネルMOSFET2をターンオフさせた際に発生し、ドレインに印加される逆起電圧をクランプ回路3によってクランプする。電流検出回路24は、クランプ回路3に発生するクランプ電圧によりNチャネルMOSFETがターンオンした際に、検出用抵抗素子21に流れる電流を複数の閾値と比較し、保護動作部26は、電流検出回路24の比較結果により、前記電流がNチャネルMOSFET2をターンオフさせた時点からの時間経過に対応する特定の閾値を超えていると判定されると、逆起電圧に基づくエネルギーを減少させるようにNチャネルMOSFET2の制御状態を変更する。

(もっと読む)

負荷駆動回路

【課題】簡単な構成で負荷オープン状態を検出することができる負荷駆動回路を提供する。

【解決手段】電源端子T1に入力される入力電圧Vinよりも低い基準電圧V1と出力端子T2の電圧Voutとを比較する第1のコンパレータ8と、スイッチング素子2がオフ状態で、且つ負荷オープン状態である場合に、出力端子T2の電圧Voutを基準電圧V1よりも高く、且つ入力電圧Vinよりも低いclamp電圧にクランプするクランプ回路7とを備えることにより、第1のコンパレータの出力によって、負荷オープン状態を検出する。また、入力電圧Vinよりも低く且つclamp電圧よりも高い基準電圧V2と出力端子T2の電圧Voutとを比較する第2のコンパレータ9を備えることにより、第1のコンパレータ及び第2のコンパレータ9の出力によって、負荷オープン状態と出力天絡状態とを検出する。

(もっと読む)

負荷駆動回路

【課題】オン指令期間とオフ指令期間の両期間における電流を高精度に検出する。

【解決手段】制御装置13は、PWM駆動信号のオン指令期間において、電流検出回路14による検出電流と電源電圧検出回路15による検出電源電圧を電圧方程式に適用してオン期間電流経路の抵抗値とインダクタンス値を算出する。これらの値から還流経路12以外の経路の抵抗値とインダクタンス値を減算してオフ期間電流経路の抵抗値とインダクタンス値を求める。オフ指令期間において、オフ期間電流経路の抵抗値Rとインダクタンス値L、ダイオード7の順電圧Vfおよび前回の計算で求めた前回電流値を電圧方程式に適用し、リニアソレノイド2に流れる負荷電流を順次算出する。

(もっと読む)

過電流保護電源装置

【課題】直流電源17からスイッチ用のFET18を経て負荷16へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】比較基準電圧生成回路40を電流供給部41と比較基準電圧発生抵抗部46とで構成し、比較基準電圧VX を生成する。過電流検出電圧生成回路50を電流供給部51と過電流検出抵抗部54とで構成し、FET18の電圧VDSが増大すると減少する電流検出電圧VY を生成する。電圧VDSの増大を検出してFET18をオフすれば、過電流保護も過熱保護も可能となる。

(もっと読む)

過電流保護電源装置

【課題】直流電源11からスイッチ用のFET12を経て負荷14へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】FETのドレイン・ソース間電圧に比例した電流Iを生成する電流変換回路4と、容量素子を含む一次遅れ回路として構成された過電流検出用電圧発生回路6とを直列接続し、その接続点Sの電圧を過電流検出用電圧VS とする。過電流検出回路5から制御回路3へ過電流検出信号が入力されて来たとき、制御回路3はFET12をオフする。過電流検出用電圧発生回路6の回路定数の設定を工夫することにより、VS を速やかに大になるようにすることが出来、1種類の保護回路で大過電流時にも保護が出来る。

(もっと読む)

ドライバ回路

【課題】 出力オフ時のスイッチング時間を短くすることのできるドライバ回路を提供する。

【解決手段】 実施形態のドライバ回路は、を駆動する出力用MOSトランジスタMV1が、電源端子VDDと誘導性負荷RLが接続される出力端子OUTとの間に接続され、抵抗R1が、出力用MOSトランジスタMV1のゲート端子とゲート電圧印加端子VGとの間に接続され、ゲート電圧印加端子VGに一端が接続された抵抗R2と、一端が抵抗R2の他端に接続され、他端が接地端子GNDに接続され、出力用MOSトランジスタMV1を制御する制御信号VSWにより導通が制御されるNMOSトランジスタMD1とを備える。さらに、このドライバ回路は、一端が抵抗R1の他端に接続され、他端が出力端子OUTに接続され、NMOSトランジスタMD1の一端から出力される信号により導通が制御されるPNPトランジスタQ1を備える。

(もっと読む)

電力用半導体素子の駆動保護回路

【課題】電力用半導体素子の制御電極の短絡動作時の電圧を通常動作時の電圧と同じ値に制限し、安全で確実な遮断を行うことが可能な電力用半導体素子の駆動保護回路の提供を目的とする。

【解決手段】本発明の電力用半導体素子の駆動保護回路は、電力用半導体素子F1と、その制御電極を駆動する駆動回路と、電力用半導体素子F1の制御電極の電圧Vgeが一定値を超えないよう制限する電圧保護回路とを備える。電圧保護回路は、電力用半導体素子F1の制御電極にエミッタが接続されたゲート放電用トランジスタTr1と、ゲート放電用トランジスタTr1にベース電位を与える電圧発生回路B1とを備え、電圧発生回路B1は、電力用半導体素子F1の駆動正電源電圧VDDから、前記駆動回路における電圧降下ΔV1を超える電圧が電力用半導体素子F1の制御電極に印加されたときに、ゲート放電用トランジスタTr1がオンできる電圧を出力する。

(もっと読む)

負荷駆動回路の保護装置

【課題】FET(T1)のドレイン電流IDが急激に増加し、電圧Vdsが増加する過渡期間であっても、FET(T1)の温度上昇量を忠実に示す信号を生成することが可能な負荷回路の保護装置を提供する。

【解決手段】FET(T1)の両端に生じる電圧Vdsに比例する電流Iaを流す電流変換回路21と、この電流Iaを通電するインピーダンス回路22を備える。そして、FET(T1)の過渡熱抵抗の時間に対する変化を示す関数を過渡熱関数Rth(t)としたとき、FET(T1)に、ゼロから階段状に増加する電流を通電した際に、インピーダンス回路22の点P2に生じる電圧V5が、過渡熱関数Rth(t)の平方根に比例した電圧となるように、前記インピーダンス回路のインピーダンスを設定する。そして、電圧V5が判定電圧V6を上回った場合に、FET(T1)を遮断して負荷駆動回路を過熱から保護する。

(もっと読む)

半導体スイッチング素子の駆動装置及び半導体スイッチング素子の駆動方法

【課題】PWM信号の傾きを制御する場合でも、本来意図したデューティと同じ期間だけ、半導体スイッチング素子をオンできる駆動装置を提供する。

【解決手段】ゲート駆動回路4が、入力されるPWM信号の立ち上がり及び立ち下がりにそれぞれ傾きを付与したゲート信号をNチャネルMOSFET1のゲートに出力する場合、デューティ調整部3は、NチャネルMOSFET1を介してランプ2に出力される電圧信号を検出し、入力信号の立ち上がりから電圧信号が立ち上がるまでの時間aと、PWM信号の立ち下がりから電圧信号が立ち下がるまでの時間bとを求め、デューティz=(x+a−b)に設定した駆動信号をゲート駆動回路4に出力する。

(もっと読む)

負荷制御装置

【課題】ノイズ対策用のコンデンサC1を設置した場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】プラス端子P11とマイナス端子P12より電力が供給されて駆動する制御回路10により、FET(T1)のオン、オフを切り替えて、負荷RLの駆動、停止を制御する場合に、マイナス端子P12とグランドとを接続するアース線に、抵抗R5とダイオードD1の並列接続回路を設ける。従って、入力スイッチSW1の投入時にプラス端子11とマイナス端子12の間に配置されたコンデンサC1の放電電流I2が流れる場合であっても、抵抗R5の電圧降下VR5によりマイナス端子P12の電圧をグランドレベルよりも相対的に低くすることができ、コンデンサC1の両端電圧VC1を拡大させて、放電電流I2を抑制し、電圧V1の低下を抑えることができる。

(もっと読む)

負荷制御装置

【課題】ノイズ対策用のコンデンサC1を設置した場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】FET(T1)のゲートとドレインとの間に第2のコンデンサC2を設けることにより、点P1の電圧V1が減少した場合に、FET(T1)のゲート電流がコンデンサC2側にバイパスしてFET(T1)に流れ、FET(T1)のゲートに供給される電荷量が低減する。このため、FET(T1)のドレイン電流の増加を抑制でき、電圧V1の急激な変動を防止できる。その結果、比較器CMP1が作動不能となる程度まで電圧V1が低下することを防止でき、比較器CMP1が誤動作することを防止できる。

(もっと読む)

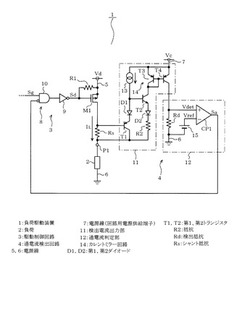

負荷制御装置

【課題】FET(T1)のドレイン電圧の低下量が大きくなった場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】FET(T1)のゲートとドレインとの間にコンデンサC1を設けることにより、点P1の電圧V1が減少した場合に、FET(T1)のゲート電流がコンデンサC1側にバイパスしてFET(T1)に流れ、FET(T1)のゲートに供給される電荷量が低減する。このため、FET(T1)のドレイン電流の増加を抑制でき、電圧V1の急激な変動を防止できる。その結果、比較器CMP1が作動不能となる程度まで電圧V1が低下することを防止でき、比較器CMP1が誤動作することを防止できる。

(もっと読む)

電源供給装置

【課題】GNDレベルの入力信号を入力する入力回路を備える場合であっても接地端子がオープン状態にあるときにスイッチング用トランジスタ素子をオフ状態に保持すること。

【解決手段】電源供給装置1は、電源2と負荷3との間に接続されたスイッチング用トランジスタ素子Fと、スイッチング用トランジスタ素子Fをオン/オフすることによって電源2から負荷3への電力供給を制御する駆動回路4と、電源2からの電力を利用して駆動される周辺回路6と、スイッチング用トランジスタ素子Fのゲート端子とソース端子との間に接続された電流駆動型の補償トランジスタユニット5と、接地電圧を供給する接地ユニット8とを備える。補償トランジスタユニット5は、周辺回路6と接地ユニット8を介して電源2から所定値以上の電流が供給された場合、スイッチング用トランジスタ素子Fのゲート端子とソース端子との間をショートする。

(もっと読む)

半導体素子の保護装置

【課題】電圧を印加した際に、所定のデューティ比で通電して作動する負荷を制御するための半導体素子を過電流から保護する半導体素子の保護装置を提供する。

【解決手段】負荷の駆動、停止を制御するための半導体素子として、150℃におけるオン抵抗が(7)式を満足するパワーMOSFET(Q1)を用いる。また、モニタ電圧生成回路13により、負荷電流ILに比例したモニタ電圧VMOを発生し、このモニタ電圧VMOと、第1基準電圧Vref1〜第4基準電圧Vref4とを比較することにより、カウンタの累積カウント値を変更するためのポイント数を設定する。従って、過電流の度合いが大きいほど累積カウント値が早く上限カウント値255に到達させることができ、半導体素子を遮断して負荷回路を保護することができる。

(もっと読む)

出力回路

【課題】出力回路の出力バッファに備えるMOSトランジスタの閾値電圧がばらついても、このMOSトランジスタのoff動作時における出力信号のスルーレートのばらつきを抑制する。

【解決手段】出力回路は、出力バッファ8のNMOSトランジスタ15と、このトランジスタ15をon動作させるためのトランジスタon動作駆動回路51と、このトランジスタ15をoff動作させるためのSW機能付電流源52と、前記トランジスタon動作駆動回路51と前記SW機能付電流源52との各々を制御する駆動制御回路50とにより構成される。前記SW機能付電流源52の電流は、前記出力バッファ8のNMOSトランジスタ15のゲート電圧が閾値電圧Vthのばらつき範囲内でばらついても、一定の電流値でゲート端子の電荷を引き抜く。

(もっと読む)

電源電圧検出回路

【課題】従来の電源電圧検出回路は、電源電圧起動時等において安定した電源電圧を供給することができないという問題があった。

【解決手段】本発明にかかる電源電圧検出回路は、電源電圧VDDに基づいて基準信号を生成する基準電圧源100と、基準信号に基づいて両端子間を流れる電流が制御されるスイッチ101と、電源電圧とスイッチ101の一方の端子との間に直列に接続され、電源電圧に応じた制御電圧を生成し、出力する電圧生成回路102と、制御電圧に基づいて、電源電圧を出力するか否かを制御するスイッチ107と、を備える。このような回路構成により、安定した電源電圧を供給することができる。

(もっと読む)

半導体装置

【課題】保護回路において、所望の遅延時間を実現する。また、遅延回路の小型化を図り、消費電力を低減させる。

【解決手段】遅延回路100は、第1のインバータ101〜第3のインバータ103、第4のpチャネルMOSFET7、第4のnチャネルMOSFET8、遅延抵抗121およびキャパシタ122で構成されている。遅延抵抗121は、第1のインバータ101の出力端子と第2のインバータ102の入力端子の間に接続されている。第4のnチャネルMOSFET8のゲート端子は、遅延抵抗121と第2のインバータ102の入力端子の間のノード113に接続されている。第4のnチャネルMOSFET8のゲート端子とドレイン端子の間には、キャパシタ122が接続されている。第4のnチャネルMOSFET8の帰還容量を用いることで、キャパシタ122の容量を、キャパシタ122の物理的な静電容量よりも擬似的に大きくする。

(もっと読む)

1 - 20 / 63

[ Back to top ]