Fターム[5J055EZ43]の内容

Fターム[5J055EZ43]の下位に属するFターム

ノンロック式スイッチ (1)

連動式スイッチ(2回路以上) (1)

キーボード (3)

Fターム[5J055EZ43]に分類される特許

61 - 72 / 72

電子制動スイッチを備えた電動機用制御回路

【課題】検出器を適用することにより、制御回路は制御回路が伝導性である時を“知り”、バイパススイッチが閉じないようにする。

【解決手段】本発明はDC電圧電源を制御するための制御回路に関し、この制御回路は電動機に直列接続されたスイッチング素子と、半導体で形成され、かつバイパスによって電動機を制動するために電動機に並列接続されたバイパススイッチとを有するものであり、また、バイパススイッチを制御するための制御回路と、スイッチング素子の状態を検出するために制御回路に接続された検出器とを有するものである。半導体は、振動や汚れの影響を受けにくい。また、半導体は、制御回路の他の構成要素と同一のキャリアに容易に設けられる程小さい。この制御回路は、一度スイッチング素子が開くと、バイパススイッチの伝導率を徐々に増大させるように構成されていることが好ましい。半導体スイッチの部分的な伝導により、工具のスイッチを切った際の機械的な衝撃が妨げられる。

(もっと読む)

電力供給制御装置

【課題】 チャタリングを抑制しつつ過熱保護が可能な電力供給制御装置を提供する。

【解決手段】 パワーMOSFET15に対して、過熱状態となっても少なくとも10ms間隔でしか強制オンオフ動作はされないため、例えば放熱性の高い周期環境であっても、高周期でのチャタリング現象を防止できる。また、過熱状態が継続して上記10ms周期の強制オンオフ動作が実行された場合、Mbitカウンタ回路71がオーバフローしたときにもパワーMOSFET15等に2次遮断動作をさせる構成であり、過熱状態に基づく外部回路の焼損も防止できる。

(もっと読む)

アナログスイッチ回路

【課題】 低コスト、かつ、低消費電力であり、開閉率が高く、入力電圧の出力側への漏れが少なく、さらにセレクタとして用いることも可能なアナログスイッチ回路を提供する。

【解決手段】 MOSFET101は、ドレインが入力端子111に接続され、ソースが中間ノード110に接続されており、MOSFET102は、ドレインが出力端子112に接続され、ソースが中間ノード110に接続され、ゲートがMOSFET101のゲートに接続されている。スイッチSW、抵抗R1およびダイオードD3、抵抗R2からなる回路は、MOSFET101および102の両方をオンさせる第1のゲート電圧または両方をオフさせる第2のゲート電圧を出力し、第2のゲート電圧を出力するときには、中間ノード110に対し、第2のゲート電圧近傍の直流電圧を与える。

(もっと読む)

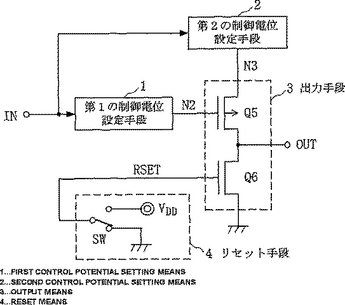

波形整形回路

第1の制御電位設定手段(1)は入力信号(IN)が論理閾値の近傍に達したときに第2の制御電位(N3)との大小関係が逆転する第1の制御電位(N2)を生成する。第2の制御電位設定手段(2)は、入力信号(IN)の変化に応じて入力信号(IN)と同方向に変化する第2の制御電位(N3)を生成する。出力手段(3)は、トランジスタ(Q5,Q6)からなり、第1の制御電位(N2)と第2の制御電位(N3)とリセット信号(RSET)とに基づいて所定の電位の出力信号(OUT)を生成する。リセット手段(4)は、波形整形回路の動作時にトランジスタ(Q6)をオフにする。  (もっと読む)

(もっと読む)

信号入力装置

【課題】スイッチ手段の開閉状態により信号ラインの電圧が変化するような信号入力装置において、経時的に生成される酸化皮膜を除去できるとともに消費電力の低減を実現する。

【解決手段】スイッチ手段SW*(*は0〜7)を介して電源電圧VDに接続される8つの信号ラインL*の電圧をマイコン3に入力させる回路5は、各信号ライン毎の通電量増減回路ZK*と、一端が接地電位(=0V)に接続された抵抗25とを備えている。そして、各通電量増減回路ZK*では、抵抗25よりも抵抗値が大きい抵抗R*で信号ラインL*を常時プルダウンするが、スイッチ手段SW*がオンされてからある時間までは、スイッチCT*がオンとなって信号ラインL*を小抵抗値の抵抗25でもプルダウンする。ある時間だけスイッチ手段SW*に生じた酸化皮膜を除去する大きな電流が流れることになる。

(もっと読む)

出力回路

【課題】 オンラインダウンロード機能を備える出力部の2つの入力端子の電圧が互いに相関がない電圧で決定されるので、起動時の突入電流が大きい。この突入電流を小さくするために定常状態での出力部の電圧を0Vにしていたが、過渡的にマイナス電位になるために寄生トランジスタをオンしてしまうという課題を解決する。

【解決手段】 ダウンロード切替デジタル信号でスイッチをオン・オフして一端が基準電位に接続された時定数回路内のコンデンサを充放電する時定数回路の出力を出力部の一方の入力端子に入力して、出力部の他方の入力端子に前記基準電位を印加するようにした。出力部の入力誤差が小さくなるので、これによる過大な突入電流が流れることはない。そのため、定常状態における出力部の電圧を自由に選ぶことができるので、寄生トランジスタをオンさせることもなくなる。

(もっと読む)

入力回路およびそれを備える電子制御装置

【課題】 マイクロコンピュータなどのマイクロコンピュータの入力ポートを、スイッチなどの接地との間の複数の接点入力端で共用するために介在される入力回路において、前記接点入力端の接地電位からの浮きに対しても、正確に接点状態を判定できるようにする。

【解決手段】 各接点入力端IN1〜IN8に対して、ベースが接続されるトランジスタQ1〜Q8を設け、たとえば奇数番目と偶数番目とのように、複数のトランジスタをマイコン12のI/OポートP01,P02からの選択出力で纏めて選択/非選択し、かつ同時に選択されない複数のトランジスタQ1とQ2.Q3とQ4,Q5とQ6、Q7とQ8のコレクタ電流を共通の抵抗R1〜R4を用いて電圧変換し、I/OポートP1〜P4に与える。したがって、スイッチSW1〜SW8のオン抵抗などで、接地電位時に接点入力に浮きが生じても、正確に接点状態を判定することができる。

(もっと読む)

多用途電子機器システム

【課題】 故障箇所を特定するための信号線の配線を簡易にして回路規模を小さくし、モジュールの再構築を容易にして、稼働率を向上させることができる多用途電子機器システムを提供する。

【解決手段】 モジュール2内の機能実行部を信号線で連結すると共に、モジュール2間の機能実行部を横断的に連結して全ての機能実行部をマトリクス状に信号線で接続し、当該マトリクス状の信号線をホスト1が監視することで、信号線の配置を複雑にすることなく、故障部位を検出し、更に代替可能な機能実行部を表示することでモジュール構成の再構築を容易に実現できるとする多用途電子機器システムである。

(もっと読む)

タイマー回路

【課題】小さい回路構成で長い時間の信号を発生することが可能なタイマー回路を提供する。

【解決手段】半導体集積回路に用いられるタイマー回路1において、入力端Aおよび出力端Bの間に接続されたコンデンサ21とコンデンサ21および出力端Bにコレクタが接続されたカレントミラー回路4の出力側トランジスタ11とを設けたタイマー部2と、カレントミラー回路の入力側トランジスタ12と入力側トランジスタ12のコレクタに接続された時間調整用の定電流源であるバイアス回路用カレントミラー回路5とを設けた時間調整部3とを備えたことを特徴とする。

(もっと読む)

半導体回路

【課題】 LSIのパワーオルエリアの電源投入・遮断時に貫通電流や誤動作を発生させることなく、確実に電源遮断状態に移行させる。

【解決手段】 パワーオフエリアにマスクレジスタ19を設け、電源遮断の前にこのマスクレジスタ19に“L”のマスク信号をセットする。バックアップエリア側では、パワーオフエリアから与えられるマスク信号を保持すると共に、このマスク信号が無電圧状態となったときには“L”を保持するラッチ回路33Aを設け、このラッチ回路33Aで保持したマスク信号を用いて、パワーオフエリア側との間の入出力信号をマスクする。

(もっと読む)

情報処理装置及びその設定方法

【課題】

ユーザの使い勝手を格段と向上し得る情報処理装置及びその設定方法を提案する。

【解決手段】

外部入力による各種の操作内容に応じた処理を実行する情報処理装置及びその設定方法において、それぞれ所定の操作内容が割り当てられた複数の操作子のうち指定された各操作子を操作禁止対象として設定して記憶しておき、続いて各操作子からの入力を無効にするための設定スイッチがオン状態で、かつ複数の操作子のうち任意の操作子からの入力があったとき、記憶された設定内容に基づいて、当該操作子が操作禁止対象であるか否かを判断した後、当該判断結果に基づいて、操作された操作子が操作禁止対象である場合には当該操作子からの入力を無効にする一方、操作された操作子が操作禁止対象でない場合には当該操作子からの入力を有効にするようにした。

(もっと読む)

半導体スイッチの制御装置

【課題】複数の負荷回路を備えた回路で短絡接地が発生した場合に、短絡接地の発生した負荷回路のみを即時に遮断し、その他の負荷回路を継続して動作させることのできる半導体スイッチの制御装置を提供する。

【解決手段】半導体スイッチとしてのMOSFETを備えた複数の負荷回路と、各負荷回路と直流電源VBとを連結する電源配線21とを備え、短絡接地が発生した際にMOSFETを遮断する機能を具備した半導体スイッチの制御装置において、電源配線21に発生する逆起電力を検出する逆起電力検出回路12を有し、各負荷回路は、MOSFETの両端電圧VDSを検出するVDS検出回路13と、VDS検出回路にて、電圧VDSが所定のレベル以上となったことが検出され、且つ、逆起電力検出回路により、電源配線に所定の閾値以上の逆起電力E1が発生していると判断された際に、MOSFETを遮断する制御を行う制御手段17とを備えたことを特徴とする。

(もっと読む)

61 - 72 / 72

[ Back to top ]