Fターム[5J055FX07]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 帰還に用いられる素子、センサ等 (193)

Fターム[5J055FX07]の下位に属するFターム

抵抗 (103)

モニター用トランジスタ (47)

トランス (28)

Fターム[5J055FX07]に分類される特許

1 - 15 / 15

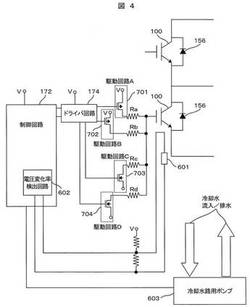

電力変換装置

【課題】本発明の課題は、電力変換装置における温度検出素子の時間変化率を検出し、温度上昇の事前予測によりフェールセーフをかけることで、発熱半導体素子の発熱抑制とモジュールケースの冷却構造最適化を実現することである。

【解決手段】上記課題を解決するために、前記半導体素子のモジュールケースまたは素子自体の温度の時間変化率を検出する検出手段と、素子のゲート抵抗値を可変にする抵抗可変回路とを設け、前記検出温度の時間変化率が所定の設定値以上になったと判断されたときは、ゲート抵抗値を前記抵抗可変回路により低減することを特徴とする電力変換装置を提供する。

(もっと読む)

発光素子のドライバ回路

【課題】発光素子のドライバ回路における消費電力を抑制する。

【解決手段】発光素子202と、発光素子202と直接に接続された電流制限用インダクタ24との直列接続部と、直列接続部に並列に接続され、電流制限用インダクタ24に蓄えられたエネルギーを回生する回生用ダイオード28と、発光素子202及び電流制限用インダクタ24に流れる電流を制御するトランジスタ26と、トランジスタ26の動作を制御する制御部22と、電流制限用インダクタ24と電磁気的に結合し、制御部22に電源電力の少なくとも一部を供給する電源用インダクタ30と、を備える。

(もっと読む)

電圧駆動型半導体素子のゲート駆動装置

【課題】FWDが小電流で逆回復する時のサージ電圧や電圧振動を抑制するために、対向アームのオンゲート抵抗値を大きくする方式では、通常電流時の損失が大きくなり、装置の損失が大きく、装置が大型となる。

【解決手段】ターンオフ時にIGBT3に接続されている内部インダクタンス5に発生する電圧を検出する電圧検出回路12と、オフゲート信号が入力されてから電圧検出回路12が電圧検出するまでの検出時間と予め定められた設定時間とを比較する比較回路13と、を備え、比較結果に応じてターンオン用のゲート駆動抵抗8又は11をスイッチ素子6、10で切替える。

(もっと読む)

電力用素子の故障検出装置

【課題】パワーモジュールに用いられる電力用素子の故障を簡単な構成で検出可能な故障検出装置を提供する。

【解決手段】故障検出装置1Bは、電力用素子としてのIGBTQ1の主電極間の電圧を、ダイオードD7を介して検出する。そして、故障検出装置1Bは、ダイオードD7のアノード電圧が予め定める基準電圧V3より低電圧であるとき、IGBTQ1は短絡故障であると判定する。好ましくは、ダイオードD7のアノード電圧が予め定める基準電圧V4より高電圧であることを併せて判定すれば、フライホイールダイオードD1がオン状態である正常動作の場合を除外できる。

(もっと読む)

スキュー調整回路

【課題】リセット動作時に大きな雑音を発生する可変遅延回路を用いたスキュー調整回路において、他の可変遅延回路のリセット動作時の雑音干渉による遅延時間の変動を防ぎ、高集積、低消費電力、高分解能、高精度なスキュー調整回路を実現すること。

【解決手段】リセット動作時に大きな雑音を発生する可変遅延回路を用いたスキュー調整回路において、全ての可変遅延回路の遅延発生動作が終了してから全ての可変遅延回路のリセット動作を行うことを特徴とするもの。

(もっと読む)

半導体装置

【課題】スイッチング素子のスイッチング動作時における寄生インダクタンスを低減し、小型化、低コスト化が可能な半導体装置を提供する。

【解決手段】正極電極1と負極電極2との間に、FWD12を並列接続したIGBT11と、FWD14を並列接続したIGBT13とを直列に接続し、2個のIGBT11,13の接続点から電力を出力電極3へ出力する半導体装置として、正極電極1と出力電極3とを隣接させ、負極電極2を出力電極3の上側に配置し、正極電極1、負極電極2それぞれの外部接続部を出力電極3の外部接続部と対向する位置に平行に隣接させ、IGBT11、FWD12を正極電極1上に配置し、IGBT13、FWD14を、IGBT11、FWD12と負極電極2を挟んだ位置にある出力電極3上に配置する。

(もっと読む)

タイマ回路及び警報装置

【課題】 電源電圧に応じて発振周波数が変動する発振部を用いながらも正確な計時が可能なタイマ回路及び該タイマ回路を用いた警報装置を提供する。

【解決手段】 制御部14は、発振回路14aがパルスを単位カウント数だけ出力する毎に単位時間の経過を判定する。また、制御部14は、電源である一次電池BTの出力電圧を検出する電圧検出部15の出力に基づいて電圧補正係数を得るとともに、温度検出部16の出力に基づいて温度補正係数を得、得られた各係数をそれぞれ所定の基準状態での単位カウント数である基準カウント数に乗じることにより、新たな単位カウント数を得る。この単位カウント数の変更は、一次電池BTの出力電圧の変動や温度の変動による発振周波数の変動による単位時間への影響を相殺するものであって、新たな単位カウント数を用いて得られた単位時間は、発振周波数の変動に関わらず略一定となる。

(もっと読む)

フリーホイールダイオードとを有する回路装置

【課題】既存の変換回路におけるノイズを低減しつつ、回路の導通損失を低減する。

【解決手段】 本願発明の代表的な形態は、一つ以上のスイッチング素子と、これに並列に接続されたフリーホイールダイオードとを有し、フリーホイールダイオードが、シリコンより大きいバンドギャップを有する半導体材料を母材とするショットキーバリアダイオードとシリコンPiNダイオードとが並列に接続して構成され、且つこれらのショットキーバリアダイオードとシリコンPiNダイオードとが別体のチップなる回路装置である。

(もっと読む)

周辺光感知回路及びこれを有する平板表示装置

【課題】周囲明るさを正確に感知し、これを利用して周囲の明るさによって自動に画面の明るさを調節することができる周辺光感知回路及びこれを有する平板表示装置を提供することを目的とする。

【解決手段】トランジスタと、トランジスタのしきい値電圧を補償する第1容量性素子と、第1容量性素子に電気的に接続された第2容量性素子と、周辺光が入射されば、第1容量性素子及び第2容量性素子のカップリング電圧を変化させる受光素子と、第1電源の電圧を出力負荷に供給して充電させる第1スイッチと、トランジスタと出力負荷との間に電気的に連結され、第1容量性素子及び第2容量性素子のカップリング電圧に対応してトランジスタを介して出力負荷の電圧が放電されるようにする第2スイッチからなる。

(もっと読む)

パワー半導体スイッチング素子の駆動回路

【課題】電圧駆動型パワー半導体スイッチング素子を、高速で駆動するゲート駆動回路を提供する。

【解決手段】本発明の電圧駆動型のパワー半導体スイッチング素子のゲート駆動回路は、電圧駆動型のパワー半導体スイッチング素子と、該スイッチング素子のゲート電極に駆動信号を与える駆動同路と、該スイッチング素子のエミッタ制御端子或いはソース制御端子と半導体モジュールのエミッタ主端子或いはソース主端子の間にインダクタンスを有するパワー半導体スイッチング素子のゲート駆動回路を備え、インダクタンスの両端に発生する電圧を検出し、その検出値に基づいて、ゲート駆動電圧或いはゲート駆動抵抗を可変させる。

(もっと読む)

過電流保護回路及びこれを備えるインバータ

【課題】過電流保護回路において、負荷のインダクタンス及び寄生容量による発振を抑制する。

【解決手段】MOSFET50のドレイン端子に負荷54が接続され、ゲート端子に駆動信号が供給される。MOSFET50のソース端子とゲート端子間にトランジスタ62を含むフォードバック回路を接続してドレイン電流を制限する。MOSFET50のドレイン端子とゲート端子間に、互いに直列接続された抵抗R72及びキャパシタC74を接続し、出力電圧の発振を抑制する。

(もっと読む)

カレントミラー回路及びこれを利用した駆動回路と駆動方法

【課題】カレントミラー回路を構成するトランジスタのしきい値電圧に関係なく所望の電流を供給するようにしたカレントミラー回路を提供する。

【解決手段】カレントミラー回路は、第1端子が電圧源VDDに接続され、ゲート端子及び第2端子が互いに電気的に接続される第1トランジスタM1と、第1端子が前記電圧源VDDに接続され、ゲート端子が前記第1トランジスタのゲート端子に接続される第2トランジスタM2と、前記第1トランジスタ及び第2トランジスタのしきい値電圧を補償することができる補償部をなす第3トランジスタM3、第4トランジスタM4、第1キャパスタC1及び第2キャパシタC2と、を具備する。

(もっと読む)

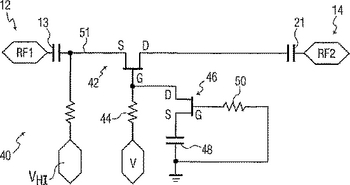

スイッチおよびスイッチ制御方法

【課題】

互いに逆の論理状態を必要とするシリーズFETおよびシャントFETを含み、1つの制御信号で駆動可能であるスイッチおよびその制御方法を提供する。

【解決手段】

少なくとも1つのシリーズFET42のチャネルを含む1つの信号経路51によって相互に結合される、少なくとも2つの信号ポート12,14と、シャントFET46のチャネルを含み、グラウンドに結合される1つのシャント経路とを備えるスイッチにおいて、前記シリーズFET42のゲートおよびシャントFET46のドレイン−ソース間に、1つの制御電圧Vを印加する。  (もっと読む)

(もっと読む)

出力回路

【課題】2つの問題(電源ノイズ及び放射ノイズ)を低減する機能と、且つ、そこで得られる効果を選定できる機能を有する出力回路を提供すること。

【解決手段】ソースが第1の電源に接続され、ドレインが出力端子に接続される第1の伝導タイプの第1のMOSFETと、ソースが第2の電源に接続され、ドレインが出力端子に接続される第2の伝導タイプの第2のMOSFETから成る出力回路において、

前記第1のMOSFETのゲートを制御する第1の制御回路と、前記第2のMOSFETのゲートを制御する第2の制御回路を持ち、出力端子から第1の制御回路と、第2の制御回路のそれぞれに出力端子の変動の高周波成分を帰還し、第1若しくは第2のMOSFETのうち、導通状態から非導通状態に変化するMOSFETについては高周波成分を帰還する手段によらず高速に非導通状態になるように制御する。

(もっと読む)

MOSFET駆動回路、プログラマブル電源及び半導体試験装置

半導体試験装置に使用されるプログラマブル電源において、電流レンジや出力リレーにおける大電流の高速切り換えを可能とする。

半導体試験装置1のプログラマブル電源10に設けられたスイッチ部20のMOSFET駆動回路22において、光絶縁素子22−1の受光部22−12からの電流によりコンデンサ部22−12に電荷が蓄積される。アナログスイッチ部22−3の切り換えによりSWAがON(SWBがOFF)となると、コンデンサ部22−12に蓄積されていた電荷によりMOSFET部21の各MOSFETのゲートがチャージされON状態となる。一方、アナログスイッチ部22−3のSWBがON(SWAがOFF)となると、MOSFETのゲートがディスチャージされる。

(もっと読む)

(もっと読む)

1 - 15 / 15

[ Back to top ]