Fターム[5J055FX37]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 最初に動作する検出回路の素子、回路 (2,393) | FET、BiTrの閾値を利用 (731)

Fターム[5J055FX37]に分類される特許

721 - 731 / 731

高速変化耐性微分レベルシフトデバイス

【課題】高周波で作動でき、電力散逸量が少なく、共通モードの変化に対して耐性を有するレベルシフトデバイスを提供する。

【解決手段】第1電圧レベル(13)で作動する入力側(14)と、第2電圧レベル(53)で作動する出力側(54)と、入力側と出力側とを接続するレベルシフト回路(48)とを備え、入力回路は、第1電圧レベルを基準とする入力信号(14)を受信し、入力信号の変化に対応する出力信号を発生する。レベルシフト回路は、MOSFET(28)を備え、MOSFETのゲートは、入力回路の各出力に接続され、ソース−ドレインパスは、第2電圧と第1電圧の基準との間に結合されている。出力側は、微分回路トポロジー(50)を有し、入力信号の変化を対応する信号をサンプリングし、その変化の間のサンプルをホールドする第1回路(56)と、微分された形態でホールドされたサンプル信号を受信して、シングルエンド形態に変換する出力回路(54)を有している。

(もっと読む)

リーク電流低減方法

データ保持モードのために回路をパワー・ダウンする方法は、電源電圧ノードを能動状態の電源電圧レベルから非能動状態の電源レベルに変更する工程と、Pチャネル・デバイスのソースを電源電圧ノードに接続する工程と、Pチャネル・デバイスのバック・ゲートに保持用電源電圧レベルを供給する工程と、Pチャネル・デバイスのドレイン電圧を保持用電源電圧レベルとは異なる基準電圧レベルに変更する工程と、Pチャネル・デバイスのゲート電圧を基準電圧レベルに変更する工程とを含む。  (もっと読む)

(もっと読む)

移相回路、高周波スイッチ並びに移相器

小型でかつ広帯域な特性を持つ移相回路を提供するもので、スルーとキャパシタンスの容量とを切り替える第1のスイッチング素子と、スルーとグランドに対するキャパシタンス

の容量とを切り替える第2のスイッチング素子と、インダクタンスをもつ第1および第2のインダクタとを備え、第1と第2のスイッチング素子の一端同士を第1のインダクタで接続し、第1と第2のスイッチング素子の他端同士を第2のインダクタで接続し、第1のスイッチング素子の一端を高周波信号入力端子に接続し、第1のスイッチング素子の他端を高周波信号出力端子に接続して、定の条件をを満たす移相器を構成する。

(もっと読む)

信号伝送回路、固体撮像装置、カメラおよび表示装置

【課題】回路電源を高速化または低電圧化しても安定な動作が可能で、高速化または低消費電力化に適した信号伝送回路を提供する。

【解決手段】複数の単位回路で構成され、駆動パルスに従って単位回路からパルス電圧が順次出力される。単位回路は、駆動パルスをドレインに入力して、パルス電圧としてソースから出力する第1の出力トランジスタ(T12)と、第1の出力トランジスタのゲートとソースとの間に接続された第1のブートストラップ容量(C11)と、第1のブートストラップ容量を充電するために、ソースが第1の出力トランジスタのゲートに接続され、ドレインが電源線または接地線あるいは充電パルス線に接続された充電トランジスタ(T11)と、一端が充電トランジスタのゲートに接続された第2のブートストラップ容量(C22)とを備える。

(もっと読む)

アクチュエータを制御するための電子装置

本発明は複数の誘導負荷を制御する装置に関する。この装置は、

複数の制御段から成る少なくとも1つの第1のグループと、

前記グループの制御段に共通した再導通化回路とを有しており、

前記制御段の各々は、

− 誘導負荷のためのボンディングパッドと、

− 導通化信号のための受信入力側と、

− 前記受信入力側に接続された制御電極と前記ボンディングパッドに接続された出力電極とを有するスイッチと、

− 前記ボンディングパッドに印加された電圧を測定し、該電圧がイネーブルレベルに達した場合にイネーブル信号を発生させるイネーブル回路を有しており、

前記再導通化回路は、前記グループの制御段のボンディングパッドにおける電圧を前記グループの各制御段のイネーブルレベルよりも高い共通のレベルに制限し、前記制御段のうちの1つのイネーブル回路がイネーブル信号を発生した場合に、導通化信号を該制御段のスイッチの制御電極に印加する。

本発明は、特に、ボンディングパッドに接続された負荷に対して同じ給電持続時間を保証するために使用することができる。  (もっと読む)

(もっと読む)

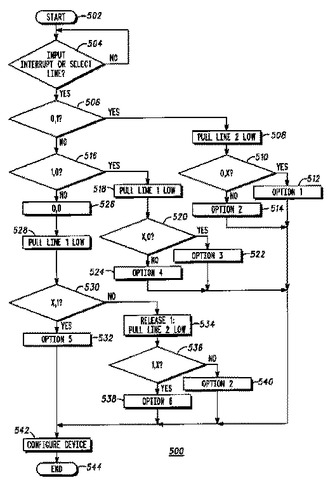

携帯機器のための割り込み駆動の拡張型オプション選択インタフェース

携帯電子機器(102)には周辺コンポーネント(104)が取り付けられ、この周辺コンポーネント(104)はオプション選択回路を使用して周辺コンポーネントのオプションクラスを示す。オプション選択回路は、携帯電子機器に割り込みを生成し、次いで種々のオプション論理ラインの論理レベルの変更により、オプションクラスを決定する。オプション選択ラインのうちの一つの論理状態の反転が検知されると、携帯電子機器はオプション選択回路のプレゼンスを知り、従って周辺コンポーネントのオプションクラスを決定する。  (もっと読む)

(もっと読む)

ダイナミックバックゲートバイアスを伴うブートストラップダイオードエミュレータ

【解決手段】ハーフブリッジスイッチング回路で使用するためのブートストラップダイオードエミュレータ回路が提供される。スイッチング回路は、負荷ノードにおいてトーテムポール構造の形で互いに繋がれているトランジスタと、これらのトランジスタを駆動するための駆動回路と、高圧側駆動回路に電力を供給するためのブートストラップコンデンサとを含む。ブートストラップダイオードエミュレータ回路は、ゲート、バックゲート、ソース、およびドレインを有し、そのドレインを高圧側供給ノードに結合され、そのソースを低圧側供給ノードに結合されているLDMOSトランジスタと、LDMOSトランジスタのゲートに電気的に結合されているゲート制御回路と、LDMOSトランジスタのバックゲートに電気的に結合されているダイナミックバックゲートバイアス回路とを備える。ダイナミックバックゲートバイアス回路は、LDMOSがオンにされたときに、LDMOSトランジスタのドレインの電圧に近いけれども同電圧よりも僅かに低い電圧をLDMOSトランジスタのバックゲートに印加することによって、LDMOSトランジスタのバックゲートを動的にバイアスするように動作可能である。 (もっと読む)

信号増幅用回路、及びアクティブマトリクス装置における同回路の使用

増幅回路はキャパシタ構造(42)と切替装置とを備える。キャパシタ構造は、電圧依存性静電容量を有する第一のキャパシタ(C2)と第二のキャパシタ(C1)(これもまた電圧依存性としてよい)とを有する。同回路は2つのモードで、すなわち少なくとも第一のキャパシタの一端子に入力電圧が提供される第一のモードと、切替装置によって第一及び第二のキャパシタ同士の間で電荷の再配分が起こることにより、第一のキャパシタにかかる電圧が変化し第一のキャパシタの静電容量が減少し、出力電圧が第一のキャパシタにかかる電圧に依存する第二のモードとで、動作可能である。本発明は電圧制御静電容量をキャパシタ間の電荷共有と併せて使用するものであり、これにより、結果的に電圧増幅特性が提供される。よってこの機構は、アナログ電圧の増幅に、または固定レベル(すなわちデジタル電圧)の昇圧に利用できる。よって本発明の回路は、レベルシフトまたは増幅のために、例えばアクティブマトリクスアレイ装置のピクセルでの用途に使用できる。  (もっと読む)

(もっと読む)

半導体スイッチの高周波制御

共振ゲートドライバ回路は、例えば、MOSFETの効率的なスイッチングを提供する。しかし、共振ゲートドライバ回路は、高いスイッチング周波数が必要とされる用途を可能にさせないことがしばしばある。本発明によれば、共振ゲートドライバ回路のインダクタのプリチャージングが実行される。これは、MOSFETの極めてエネルギー効率が良い高速な動作を可能にさせる。  (もっと読む)

(もっと読む)

無線周波数用双極単投スイッチ

【解決手段】本発明の双極単投(DPST)スイッチは、第1入力ポートに対応する第1回路部と、第2入力ポートに対応する第2回路部と、及び出力ポートを有するスイッチ回路とを具備する。ここで、第1及び第2の回路部の各々は、分離チャンネルの一部を提供する少なくとも1個の第1トランジスタと、送信チャンネルの一部を提供する少なくとも1個の第2トランジスタと、送信チャンネル又は分離チャンネルのいずれかを選択する制御バイアスを提供する少なくとも1個の第3トランジスタとを有する。 (もっと読む)

電流検出式の双方向スイッチおよびプラズマディスプレイ用の駆動回路

【解決手段】開示される双方向スイッチ(20)は、第1および第2の半導体スイッチング素子(22)と、これらのスイッチング素子に直列に接続されることによって直列回路を形成する電流センサ(RS)と、これら第1および第2のスイッチング素子がほぼ同時にオン・オフされるようにこれら第1および第2のスイッチング素子のオン・オフ操作を制御する駆動回路(30)であって、制御入力に応じてこれら第1および第2のスイッチング素子をオンにしたり電流センサの電流がほぼゼロ電流近くまで低下する際にこれら第1および第2のスイッチング素子をオフにしたりする駆動回路と、を備える。また、このような双方向スイッチ(20)を用いたプラズマディスプレイパネル(PDP)用の放電サステイン駆動回路も開示される。 (もっと読む)

721 - 731 / 731

[ Back to top ]