Fターム[5J056BB46]の内容

Fターム[5J056BB46]の下位に属するFターム

静電気に対する保護 (18)

Fターム[5J056BB46]に分類される特許

1 - 20 / 60

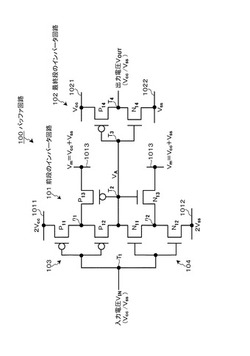

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

半導体チップ及びこれをパッケージングした半導体装置

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

出力回路

【課題】高電圧信号を出力する回路を低耐圧トランジスタで構成しても、信頼性を向上させることのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力部1が、高電圧電源端子VCCHと出力端子とZの間に接続されPMOSトランジスタP11、P12と、接地電位端子GNDと出力端子Zとの間に接続されたNMOSトランジスタN11、N12とを有し、低電圧入力信号INが入力されるプリバッファ部2が、PMOSトランジスタP11、NMOSトランジスタN11へ、VCCHよりも小さい振幅のゲート電圧PG、NGを出力する。PMOSトランジスタP12およびNMOSトランジスタN12のゲート端子へVCCHよりも低い定電圧VGが印加され、PMOSトランジスタP12の基板へVCCHよりも低い基板バイアス電圧VBPが印加され、NMOSトランジスタN12の基板へ接地電位よりも高い基板バイアス電圧VBNが印加される。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

駆動回路、駆動信号出力回路及びインクジェットヘッド

【課題】出力する駆動信号の遅延を小さくし且つ小型化した安価な駆動回路、駆動信号出力回路及びインクジェットヘッドを実現することである。

【解決手段】駆動回路30は、負荷を駆動するプッシュ側のMOSFET32及びプル側のMOSFET33と、アノード、カソードがMOSFET32のゲート、ソースに接続されたツェナーダイオード38と、アノード、カソードがMOSFET33のソース、ゲートに接続されたツェナーダイオード39と、昇圧回路31の出力端とMOSFET32のゲートとに接続された抵抗36と、昇圧回路31の出力端とMOSFET33のゲートとに接続された抵抗37と、抵抗36、抵抗37に並列に接続されたスピードアップコンデンサ42,43と、を備える。MOSFET32,33のソースが高圧側、グランドに接続され、MOSFET32,33のドレインが互いに接続される。

(もっと読む)

信号入力回路

【課題】信号入力端子のプルアップ機能を有したまま、信号入力端子に入力する信号電圧が高電位電源端子の電圧を超えるときがあっても、上記したような問題が生じないようにした信号入力回路を提供する。

【解決手段】エンハンスメント型NMOSトランジスタMN1のバックゲートを低電位電源端子2に接続し、ドレインとゲートを高電位電源端子1に接続し、ソースを信号入力端子3に接続する。エンハンスメント型NMOSトランジスタMN1のオン抵抗を、信号入力端子3に接続される前段回路のドライバの“L”レベル電圧出力時の出力インピーダンスよりも高い値に設定する。

(もっと読む)

半導体集積回路装置

【課題】高い耐圧を有する入出力バッファ回路を備えた半導体集積回路装置を、中耐圧の素子のみで構成すること。

【解決手段】入出力バッファ回路を備えた半導体集積回路装置であって、入出力バッファ回路は、低スルーレートを実現するための帰還容量素子として、直列に接続された第1の容量素子及び第2の容量素子を有するとともに、第1の容量素子と第2の容量素子との間のノードの電位を入出力モードに応じて調整する電位調整回路を有する。

(もっと読む)

レベルシフト回路

【課題】バッテリの電源投入時等の電源電圧の急激なオーバーシュートに対する耐性を向上させるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、バッテリからの高電圧レベルの入力信号VINを入力するレベルシフト部10と、レベルシフト部10の中間信号Vmを一定以下に制限するクランプ部20と、中間信号をより低電圧のCMOSレベルで出力する出力バッファ部30とを備える。出力バッファ部30の初段においてpMOSトランジスタ31の負荷を抵抗32とすることにより、電源電圧のオーバーシュートに対する耐性を向上させる。

(もっと読む)

負荷駆動装置

【課題】従来の負荷駆動装置は、電源が正常に接続された場合の待機時において消費電流が増大するという問題があった。

【解決手段】本発明にかかる負荷駆動装置は、電源端子PWRと出力端子OUTとの間に接続された出力トランジスタT1と、出力端子OUTと接地端子GNDとの間に接続された負荷11と、出力トランジスタT1のゲートと接地端子GNDとの間に設けられ、電源11の極性が逆になった場合に出力トランジスタT1を導通状態にする保護トランジスタMN3と、電源10の極性が正常の場合に接地端子GNDと保護トランジスタMN3のバックゲートとを導通状態に制御するバックゲート制御回路17と、を備える。

(もっと読む)

集積回路装置、電子機器及び集積回路装置の端子保護方法

【課題】低コストで、端子を保護できる集積回路装置、電子機器及び集積回路装置の端子保護方法等を提供する。

【解決手段】集積回路装置は、I/O回路と、I/O回路の入力又は出力と電気的に接続される端子と、前記端子と所与のクランプ電圧が供給される電源線との間に電流を流して端子の電圧を変化させるクランプ回路と、端子の電圧を検出する電圧検出部と、電圧検出部による検出結果に基づいて、クランプ回路に流れる電流を制御するクランプ制御部とを含み、クランプ制御部が、保護制御信号が第1のレベルのとき、端子の電圧が所与の閾値電圧以上であることを条件に、端子と前記電源線との間に電流が流れるように前記クランプ回路を制御すると共に、保護制御信号が第2のレベルのとき、端子と電源線との間に電流が流れないようにクランプ回路を制御する。

(もっと読む)

ドライバ回路

【課題】ドライバ回路、特にメインドライバに過電圧がかからないようにして、回路を過電圧による破壊から保護する。

【解決手段】第1電源VDDIから動作電源を得て動作するプリドライバB1と、第2電源VDDEから動作電源を得るとともにプリドライバB1からの出力信号を増幅して出力するメインドライバB2と、を備える。第1電源VDDIとプリドライバB1との間に第1スイッチB4を備える。第2電源VDDEとメインドライバB2との間に第2スイッチB5を備える。過電圧保護シーケンス回路B3は、第1スイッチB4および第2スイッチB5のオンオフ制御をして、プリドライバB1とメインドライバB2のオンオフ順序を制御し、ドライバ回路、特にメインドライバB2に過電圧がかかるのを防ぐ。

(もっと読む)

単位回路および電子回路

【課題】出力回路における各トランジスタのゲート・ソース間に印加される電圧を制限するための構成や単位回路へ入力される制御信号の振幅を小さくするための構成を簡素化する。

【解決手段】単位回路Jは、電源線101と接地線103との間に直列に接続された第1のPチャネルトランジスタ、第2のPチャネルトランジスタ、第1のNチャネルトランジスタ、および第2のNチャネルトランジスタとを備える。そして、第1のPチャネルトランジスタがオン状態のときにその電位がVDDとなり、第1のPチャネルトランジスタがオフ状態のときにその電位がVREF+Vtp2となる第1出力信号V1を第1出力端子から出力し、第2のNチャネルトランジスタがオン状態のときにその電位がGNDとなり、第2のNチャネルトランジスタがオフ状態のときにその電位がVREF−Vtn1となる第2出力信号V2を第2出力端子から出力する。

(もっと読む)

レベルシフト回路およびそれを備えた半導体装置

【課題】高い信頼性や、高速性を備えたレベルシフト回路を実現する。

【解決手段】例えば、高電圧レベル(電源電圧VCCHのレベル)の入力信号INを低電圧レベル(電源電圧VCCLのレベル)の出力信号OUTに変換するレベルシフト回路LS1において、カップリングノイズを抑制するためのNMOSトランジスタMN4を設ける。INが‘H’レベルから‘L’レベルに遷移した際には、NMOSトランジスタMNH1の寄生容量(CGD)を介して、そのドレインとなるノードNDE1にアンダーシュートが生じ得るが、それをMN4からの電流I1によって抑制する。これにより、PMOSトランジスタMPL1,MPL2を薄膜仕様としてもその耐圧を満たすことができ、薄膜仕様に伴い高速動作が実現できる。

(もっと読む)

高信号レベル対応入出力回路

(213)は、特定レベルを検出するためのマルチ信号レベルの信号を受け付けるように適合された入力回路(M6,M6,M7)を持つ。これらの信号レベルは、第1信号レベルおよび、より大きな第2信号レベルを含む。入力回路の電子構成要素は、第2信号レベルよりも低い信頼性レベルを持っている。ラッチ回路(710)は、受け付けられた信号の検出レベルに合致する信号をラッチするために、入力回路(M6,M6,M7)に結合される。  (もっと読む)

(もっと読む)

高信号レベル対応入出力回路

インターフェース回路用の信号ドライバ(211)は、第1信号レベルにおいて出力信号および入力信号を受け付ける第1ステージレベルシフタ(311)を持つ。この信号ドライバ(211)はまた、第1ステージレベルシフタ(311)に結合され、第2信号レベルにおいて信号を出力する第2ステージレベルシフタ(312)を持つ。第1(311)および第2(312)ステージレベルシフタの電子構成要素は、第2信号レベルよりも低い信頼性の限界を持っている。第1ステージレベルシフタ(311)および第2ステージレベルシフタ(312)の第1および第2ステージ構成は、第2信号レベルにおいて信号を出力する処理の際に、電子構成要素が、信頼性の限界より高い端子〜端子信号レベルにさらされるのを、防止する。  (もっと読む)

(もっと読む)

周波数出力装置、流量計、及び流量計測装置

【課題】周波数出力端子の保護と、信号波形の帯域を十分に確保することができる周波数出力装置を提供する。

【解決手段】周波数信号を出力する周波数出力装置2の出力端子にバリスタ素子Zs1を設ける。これにより、例えばバリスタ電圧を超える電圧が出力端子に印加された場合に、そのバリスタ電圧を超える電圧分を接地側に流して、周波数出力装置2に高電圧のサージ電圧が入力されるのを防ぎ、周波数出力装置2を保護する。また、放電時における放電量を少なくして電圧の変化を滑らかにし、電圧の立ち下がり時におけるピーク電流を下げて、ラジオノイズ等の電磁誘導ノイズの影響を低減し、必要な周波数信号の帯域を確保する。

(もっと読む)

半導体集積回路装置

【課題】 レベルシフト回路のオン耐圧について配慮し、オン耐圧を高めて破壊を防止する回路を提供することにある。

【解決手段】 高圧出力DOUTがHiの状態では、N型トランジスタHVN1、P型トランジスタHVP2はOFF状態、N型トランジスタHVN2、P型トランジスタHVP1はON状態であり、HVN1のドレイン−ソース間には高電圧VHが印加されている。高圧出力DOUTをLoに遷移させる過程において、N型トランジスタHVN1のゲート電位を一旦、VDDとGNDの中間状態に置き、N型トランジスタHVN1のドレイン−ソース電圧を下げた後、ゲート電圧をVDDに上昇させる。これにより、N型トランジスタHVN1のドレイン−ソース間電圧が高く、且つ、ドレイン電流が大きい状態を回避し、レベルシフト回路のオン耐圧を高めて破壊を防止する。

(もっと読む)

電圧ストレスを低減したゲート制御回路のための回路および方法

【課題】素子にかかる電圧ストレスを低減したゲート制御回路を提供する。

【解決手段】供給電圧より高電圧レベルの出力を供給してトランスファゲートP2を制御するMOSトランジスタ回路において、2つのクランプ回路CLAMP1,CLAMP2が設けられる。第1クランプ回路CLAMP1は、ポンプ電圧を供給するPMOSトランジスタP1のドレイン/ソースが所定電圧を超えないように、トランジスタP1のゲートとソース/ドレインとの間の電圧を確保する。第2クランプ回路CLAMP2は、NMOSトランジスタN1のゲートと同トランジスタN1のドレイン/ソースに接続される出力との間の電圧が所定量を超えないように保証する。2つのクランプ回路は、ゲートとソース/ドレインとの間の電圧を確保することによりドレイン/ソース端子が所定電圧を超えないようにし、それによりトランジスタP2にかかるゲートストレスを低減する。

(もっと読む)

1 - 20 / 60

[ Back to top ]