Fターム[5J056BB48]の内容

Fターム[5J056BB48]に分類される特許

1 - 17 / 17

クロック負昇圧回路

【課題】回路構成が簡易、小型でウェル・バイアス電圧の立ち上がり時間が短く、安定した負昇圧クロックを供給することが可能なクロック負昇圧回路を提供する。

【解決手段】クロック負昇圧回路部301、クロック負昇圧回路部302、クロック負昇圧回路部301、クロック負昇圧回路部302のウェル層上に設けられたNMOSトランジスタ107に電圧を供給するキャパシタ403、NMOSトランジスタ104を備え、クロック負昇圧回路部301が備えるNMOSトランジスタ104とキャパシタ403とを接続する電圧ライン303、クロック負昇圧回路部302が備える2つのNMOSトランジスタ104の出力を接続する電圧ライン303によってクロック負昇圧回路を提供する。

(もっと読む)

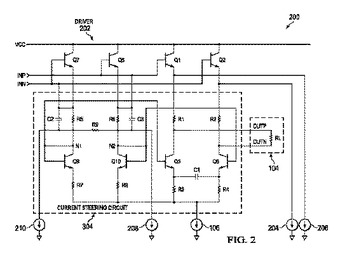

正確な電流ステアリングを備えた低電力高速差動ドライバ

BiCMOSプロセストランジスタを用いる混合又はハイブリッドモードドライバが、ドライバのプルアップ部の電圧に調和するプルダウン電流を生成するため電流ステアリング回路(電圧駆動差動対の代わりに)を有する。ドライバは、速度を速め、生成する出力同相電圧ゆらぎが一層小さい。回路200が、出力端子(OUTP、OUTN)を介して電流を供給して負荷104を駆動するドライバ202(これは、電圧モードと電流モードの組み合わせを用いる)を有する。ドライバ202は、NPNトランジスタ(Q1、Q2、Q7、Q8)、電流源(106、204、206)、及び電流ステアリング回路304を有する。電流ステアリング回路304は、フィードフォワード・レジスタ・キャパシタ(RC)ネットワーク(R5、R6、C2、C3)、入力NPNトランジスタ(Q9、Q10)、出力NPNトランジスタ(Q5、Q6)、電流源(208、210)、レジスタ(Rl〜R4及びR7〜R8)、及びバイパスキャパシタC1を有する。NPNトランジスタはPNPトランジスタで置き換えてもよい。  (もっと読む)

(もっと読む)

入出力インターフェース回路、集積回路装置および電子機器

【課題】 入出力インターフェース回路におけるラッチアップの発生を確実に防止すること。

【解決手段】 本発明の入出力インターフェース回路は、入出力端子T1と、入力バッファー102と、フローティングウエル領域N4に形成される第1導電型の第1MOSトランジスタMP1(FNWL)を有し、入出力端子を経由して外部に信号を出力するための出力バッファーINV1と、静電保護回路390と、フローティングウエル電位調整回路108と、を含み、前記静電保護回路は、第1抵抗R1と、第1抵抗R1の他端と高レベル電源電位VDDとの間に接続されるダイオードD1と、を有し、フローティングウエル電位調整回路108は、入出力端子T1に一端が接続される第2抵抗R2と、第2抵抗R2の他端に一端が接続され、他端がフローティングウエル領域N4に接続され、ゲートに高レベル電源電位VDDが接続される、第1導電型の第2MOSトランジスタMP2(FNWL)と、を有する。

(もっと読む)

半導体集積装置

【課題】基盤電位をモニターして、確実にラッチアップをリセットできる機能を有する半導体集積装置を提供する。

【解決手段】第1導電型の半導体基板11の第2導電型のウェル層12に形成された第1チャネルMOSトランジスタP1と、半導体基板11に形成され、基準電位GNDに接続された第2導電型の半導体層14と、半導体基板11の基盤電位VEEと基準電位GNDとの電位差をモニターし、不純物拡散層13aと、ウェル層12と、半導体基板11と、半導体層14とにより付随的に形成される寄生サイリスタが導通することにより生じるラッチアップを検出するための検出手段15と、基準電位GNDと基盤電位VEEとの間に接続され、検出手段15の出力信号Voutに応じて基準電位GNDと基盤電位VEEとを同電位にし、寄生サイリスタの導通を阻止してラッチアップを解消するためのスイッチ手段16と、を具備する。

(もっと読む)

半導体装置

【課題】基板バイアス制御手法を備えた半導体装置について、パワーオンリセット機能によるリセット期間終了時において基板バイアス対象回路の基板電位が変動し、ラッチアップ発生により半導体集積回路装置が誤動作を起こすのを防ぐことを目的とする。

【解決手段】本発明の一実施形態に係る半導体装置は、所定の基板電位を生成する基板電位ジェネレータ回路2、リセット期間において基板バイアス対象回路1の基板を電源に接続するとともに、リセット期間後において基板を基板電位ジェネレータ回路2にノードVBGP,VBGNを介して接続するパワーオンリセット手段、所定の電圧を生成する電圧生成回路6を備えて構成される。パワーオンリセット手段はリセット期間においてノードVBGP,VBGNに電圧生成回路6を接続する。

(もっと読む)

レベルシフト回路

【課題】VDD2>VSS2>VSS1、且つVDD1>VSS1の関係にある入力電圧VDD1,VSS1を入力してVDD2,VSS2にレベルシフトする際に、VSS1>VSS2になったときであってもラッチアップ現象の発生を回避する。

【解決手段】信号出力端子OUTとなるノードN1とノードN2の間に逆並列接続された2個のインバータからなり且つ電圧VDD2とVSS2で動作するラッチ回路3と、信号入力端子INとノードN3の間に接続され且つ電圧VDD1とVSS1で動作する第1のインバータ1と、ノードN3とノードN4の間に接続され且つ電圧VDD1とVSS1で動作する第2のインバータ2と、ノードN1,N2,N3に接続された第1の反転駆動回路4と、ノードN1,N2,N4に接続された第2の反転駆動回路5と、電圧VSS1の端子側をアノード、電圧VSS2の端子側をカソードとするダイオードD1とを設ける。

(もっと読む)

過熱保護回路を備える定電圧回路を内蔵した半導体装置

【課題】出力端子Voutに高圧のサージ電圧が印加されても、ラッチアップを防止し、半導体チップ上に形成した配線の溶断を防止できるようにする。

【解決手段】出力トランジスタM1を制御して、入力電圧を所定の出力電圧に変換する定電圧回路と、半導体チップの温度を検出して、定電圧回路の出力電流を制限する過熱保護回路10を内蔵した半導体装置1において、過熱保護回路10に温度検出用のダイオードD1を設け、ダイオードD1に直列に抵抗R3を接続する。ダイオードD1を前記出力トランジスタM1の近傍に配置することにより、出力端子Voutに高圧のサージ電圧が印加された場合でも、ラッチアップを防止でき、しかもサージ電圧印加中の貫通電流も少なくすることができる。

(もっと読む)

半導体集積回路装置

【課題】電源制御後に電源に対する所望の基板電圧へ制御しようとする際、所望の基板電圧に移行するまでの移行時間が長くなるという課題があった。また電源制御、基板制御を各々の電圧に関係なく実施しようとすると、ラッチアップや耐圧劣化が発生する。

【解決手段】トランジスタ5,6で構成される被制御回路4に対し供給する電源電圧を制御する電源制御回路2と、トランジスタ5,6の基板を制御する基板制御回路1と、電源遷移中の基板を別系統から制御する特殊基板制御回路3とを設け、電源遷移中に特殊基板制御回路3により積極的に基板制御を実施し、早めに所望の基板電圧へ制御することにより、所望の基板電圧に移行するまでの時間を短縮する。また、電源電圧と基板電圧との間の電位差条件によって発生するラッチアップ、耐圧劣化の課題に対しては、電位差条件に対応した特殊基板制御回路3による電圧供給、電流供給を実施する。

(もっと読む)

バス駆動回路、データ伝送制御デバイスおよびバス駆動方法

【課題】いわゆるラッチアップ防止のため一方のバス側の外部駆動デバイスの検出と、他方のバス側の十分低いプルダウンを両立して、バス駆動回路を安定動作させる。

【解決手段】それぞれが駆動部(駆動トランジスタM1mまたはM1s)を含み、バスMまたはバスSの電位の電圧閾値に対する大小関係と、内部の駆動部を流れる駆動電流ImまたはIsの電流閾値に対する大小関係とを検出する第1および第2駆動検出回路(バスインターフェース1,3)と、制御回路2とを有する。制御回路2は、バスインターフェース1のバス電位検出と駆動電流検出の結果に基づいてバスS駆動トランジスタM1sを制御し、バスインターフェース3のバス電位検出と駆動電流検出の結果に基づいてバスM駆動トランジスタM1mを制御する。

(もっと読む)

ボディバイアスされたトランジスタを有する集積回路に対するラッチアップ防止回路網

【課題】金属酸化物半導体トランジスタ内のラッチアップの防止を行う能動ラッチアップ防止回路網を備える集積回路を提供すること。

【解決手段】ボディ端子をそれぞれが有する金属酸化物半導体トランジスタと、電力供給信号を集積回路に供給する入出力ピンと、ボディバイアス信号を該金属酸化物半導体トランジスタの該ボディ端子に分配するボディバイアス経路と、該電力供給信号をモニタして、該金属酸化物半導体トランジスタに対する潜在的なラッチアップ条件を検出することと、該ボディバイアス経路を安全な電圧に維持して、該潜在的なラッチアップ条件が存在する間、該金属酸化物半導体トランジスタ内のラッチアップを防止することとを行う能動ラッチアップ防止回路網とを備える、集積回路。

(もっと読む)

ラッチアップ防止を有する調整可能なボディバイアス生成回路網

【課題】調整可能なpチャネル金属酸化物半導体トランジスタボディバイアス生成回路網を備える集積回路を提供すること。

【解決手段】ボディバイアス経路を介してボディバイアス信号を受けるボディ端子を有する、pチャネル金属酸化物半導体トランジスタと、該ボディバイアス信号を該ボディバイアス経路に供給する調整可能なpチャネル金属酸化物半導体ボディバイアス生成回路網であって、該調整可能なpチャネル金属酸化物半導体トランジスタボディバイアス生成回路網は、高電力供給端子と該ボディバイアス経路との間に結合されたpチャネル制御トランジスタと、該pチャネル金属酸化物半導体トランジスタがラッチアップするのを防止するために、該ボディバイアス経路に接続された能動ラッチアップ防止回路とを含む、調整可能なpチャネル金属酸化物半導体トランジスタボディバイアス生成回路網とを備える、集積回路。

(もっと読む)

スイッチ回路、ダイオード

【課題】 従来の双方向導通可能なスイッチ回路において、スイッチ機能を担うトランジスタに含まれる寄生サイリスタで、ラッチアップが生じるという問題がある。そこで、本発明は、寄生サイリスタによるラッチアップの発生を抑制し、双方向に導通可能なスイッチ回路を提供することを目的とする。

【解決手段】本発明は、スイッチ機能を担うMOSトランジスタと、MOSトランジスタのソース及びドレインに存在する寄生ダイオード、それぞれと並列に接続されたダイオードを含むスイッチ回路である。

(もっと読む)

内部電圧発生回路

【課題】異なる目標電位を有する2種類以上の内部電位の生成の際にチャージポンプの動作時期を調節し、これらの電位の間に発生され得るラッチアップ現象を防止できるようにすること。

【解決手段】本発明の内部電圧発生回路は、ポンプ電圧を生成するポンプ電圧発生手段と、前記ポンプ電圧と周辺電圧とのレベルを比較し、イネーブル信号を出力するレベル比較器と、前記イネーブル信号に応じてポンプイネーブル信号を出力し、前記イネーブル信号に応じて前記周辺電圧を生成する周辺電圧発生手段とを備える。

(もっと読む)

半導体集積回路装置及びそのスタンバイモード設定方法

【課題】スタンバイモード時における外部機器、外部メモリ等の破損や、半導体集積回路内におけるラッチアップ等による大電流の発生を防止する。

【解決手段】スタンバイモード設定時において、入出力回路50に印加する第2電源切替信号STBを“L”レベルから“H”レベルに遷移させて、その入出力回路50により、半導体集積回路40ら出力される出力イネーブル信号OE及び出力データ信号ODに代えて、“H”又は“L”レベルの固定信号をI/Oパッド95へ出力する。更に、I/Oパッド95から入力されるデータ信号に代えて、“L”レベルの固定信号を半導体集積回路40の入力部43へ与える。その後、第1電源切替信号STを“L”レベルから“H”レベルへ遷移させて、半導体集積回路40に印加するコア電源V1をオフ状態にし、その半導体集積回路40をスタンバイモードにする。

(もっと読む)

半導体メモリ素子の内部電圧生成装置

【課題】 ラッチアップ現象を防止できる半導体メモリ素子の内部電圧生成装置を提供すること。

【解決手段】 レベル感知部20、周期信号生成部22及びチャージポンピング部24から構成され、内部電圧VBB及び基準電圧VBB_REFの大小を比較した結果に応じて、電源電圧VSSをチャージポンピングして内部電圧VBBを生成する内部電圧生成部と、初期レベル感知部500及び初期ドライバー40’から構成され、内部電圧VBB及び電源電圧VSSの大小を比較した結果に応じて、電源電圧VSSを内部電圧VBBとして出力する初期内部電圧生成部とを備える。

(もっと読む)

CMOSメモリセル内のラッチアップを防ぐための回路

回路の電源バス(42)又は接地バス(44)に沿って配置された電流制限器(46、48)を含むCMOS回路(40)が提供される。電流制限器(46、48)は、CMOS回路(40)のラッチアップを阻止するように構成される。より具体的には、電流制限器(46、48)は、寄生pnpnダイオード構造体の接合を逆バイアスに維持するように構成される。回路の電源バスに沿って配置された電流制限器を含まない第1のCMOS回路内に配置されたpnpnダイオードの電流−電圧プロットを生成する段階を含む方法も提供される。更に、本方法は、第2のCMOS回路を通る電流が保持電流レベルを超えないように、電流−電圧プロットから保持電流レベルを求めて、第1のCMOS回路と同様の設計仕様を有する第2のCMOS回路の電源バスに沿って配置するように電流制限器の大きさを定める段階とを含む。 (もっと読む)

バルクバイアスを備える負極性チャージポンプ

チャージポンプ構造のCMOS環境につきものである寄生バイポーラトランジスタのターンオンを回避するような方法でnチャネルMOSトランジスタのバルクがバイアスをかけられる、nチャネルMOSトランジスタの負極性電圧チャージポンプが開示される、  (もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]