Fターム[5J056CC28]の内容

Fターム[5J056CC28]に分類される特許

1 - 13 / 13

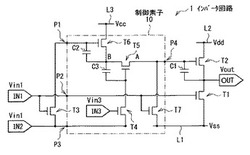

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】7Tr3Cで構成されるインバータ回路1において、入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3と、制御素子10とを介して、入力電圧Vin2がトランジスタT2のゲートに入力される。入力電圧Vin1,Vin2がともにハイレベルの電圧Vddとなっている期間においては、入力電圧Vin3がハイレベルの電圧Vddとなっているときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

半導体装置及び電子機器

【課題】一導電型のTFTのみを用いて回路を構成することにより工程削減が可能であり、かつ出力信号の電圧振幅が正常に得られる表示装置の駆動回路を提供する。

【解決手段】出力ノードに接続されているTFT203のゲート−ソース間に容量205を設け、TFT201、202からなる回路は、ノードαを浮遊状態とする機能を有する。ノードαが浮遊状態のとき、容量205によるTFT203のゲート−ソース間の容量結合を利用してノードαの電位をVDDよりも高い電位とし、これによって、TFTのしきい値に起因する振幅減衰が生ずることなく、正常にVDD−GND間の振幅を持った出力信号を得ることが出来る。

(もっと読む)

レベルシフタ回路および表示ドライバ回路

【課題】回路面積を大きくすることなく入力信号に対する応答速度が速いレベルシフタ回路および表示ドライバ回路を提供することである。

【解決手段】本発明にかかるレベルシフタ回路1は、第1の電圧変換回路11、第2の電圧変換回路12を備える。第1の電圧変換回路11は、電源電位GNDと電源電位VDDLとの間の振幅を有する入力信号INが入力されると共に、電源電位VDDLよりも高い電源電位VDDHが供給される。また、電源電位VDDHの電源線41から供給される電流を制限する電流制限回路34を備え、入力信号INよりも大きな振幅を有する電圧信号を入力信号INに応じて出力する。第2の電圧変換回路12は、電源電位VDDHが供給されると共に、第1の電圧変換回路11から出力された電圧信号に応じて電源電位GNDと電源電位VDDHとの間の振幅を有する出力信号を出力する。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】3Tr2Cで構成されるインバータ回路において、トランジスタTr2のゲートと低電圧線L1との間、さらにトランジスタTr2のソースと低電圧線L1との間に、入力電圧Vinと低電圧線L1の電圧との電位差に応じてオンオフ動作するトランジスタTr1,Tr2が設けられている。トランジスタTr2のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr2のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

液晶表示装置及び電子機器

【課題】 一導電型のTFTのみを用いて回路を構成することにより工程削減が

可能であり、かつ出力信号の電圧振幅が正常に得られる表示装置の駆動回路を提

供する。

【解決手段】 出力ノードに接続されているTFT203のゲート−ソース間に

容量205を設け、TFT201、202からなる回路は、ノードαを浮遊状態

とする機能を有する。ノードαが浮遊状態のとき、容量205によるTFT20

3のゲート−ソース間の容量結合を利用してノードαの電位をVDDよりも高い

電位とし、これによって、TFTのしきい値に起因する振幅減衰が生ずることな

く、正常にVDD−GND間の振幅を持った出力信号を得ることが出来る。

(もっと読む)

半導体表示装置

【課題】良好な動作をおこなう半導体表示装置を提供する。

【解決手段】p型トランジスタ、第1の容量素子、第1のスイッチ、n型トランジスタ、第2の容量素子、第2のスイッチを有する半導体表示装置であって、第1の容量素子の第1の電極は、第1の配線に電気的に接続されており、第1の容量素子の第2の電極は、p型トランジスタのゲートに電気的に接続されており、第1のスイッチの第1の端子は、p型トランジスタのゲートに電気的に接続されており、第1のスイッチの第2の端子は、p型トランジスタの第1の端子及び第2の端子の一方に電気的に接続され、第2の容量素子の第1の電極は、第1の配線に電気的に接続されており、第2の容量素子の第2の電極は、n型トランジスタのゲートに電気的に接続されており、第2のスイッチの第1の端子は、n型トランジスタのゲートに電気的に接続されており、第2のスイッチの第2の端子は、n型トランジスタの第1の端子及び第2の端子の一方に電気的に接続されている。

(もっと読む)

表示装置

【課題】ポリ・シリコン・薄膜トランジスタで構成されるレベルシフト回路を備える表示装置において、レベルシフト動作スピードの高速化を図る。

【解決手段】レベルシフト回路を備える表示装置であって、前記レベルシフト回路は、半導体層がポリシリコン層で構成される薄膜トランジスタと、前記薄膜トランジスタの第2電極と基準電源との間に接続される負荷抵抗素子と、前記薄膜トランジスタの第2電極に接続される波形整形回路と、前記薄膜トランジスタの第1電極にアノード領域が接続され、前記薄膜トランジスタの第2電極にカソード領域が接続されるダイオード素子とを有する。

(もっと読む)

電気回路、電気回路の駆動方法、表示装置および電子機器。

【課題】簡易な構成でインバータ回路の動作を高速化する。

【解決手段】インバータ回路Qは、電源線L1と電源線L2との間に直列に接続されたPチャネル型のトランジスタTR1とNチャネル型のトランジスタTR2とを含む。トランジスタTR1およびトランジスタTR2の各々のバックゲートBには共通の閾値制御信号SAが供給される。閾値制御信号SAは、インバータ回路Qに対する入力信号SINがハイレベルから立下がり始める時点からインバータ回路Qの出力信号SOUTがハイレベルに到達する時点までの期間TAを含んでローレベルを維持し、入力信号SINがローレベルから立上がり始める時点から出力信号SOUTがローレベルに到達する時点までの期間TBを含んでハイレベルを維持する。

(もっと読む)

半導体集積回路

【課題】 複数のトランジスタをカスケード接続した回路において、トランジスタの特性を保持できる半導体集積回路を提供する。

【解決手段】 インバータ回路1は、直列に接続されたP型MOSトランジスタ10,11と2個のN型MOSトランジスタ12,13とを有する。P型MOSトランジスタ10が高電位電源VHに接続され、N型MOSトランジスタ13が低電位電源VLに接続されている。各MOSトランジスタ10〜13のゲートは入力信号線19に接続されている。また、インバータ回路1は、P型MOSトランジスタ10,11の接続点14と入力信号線19とを接続するP型MOSトランジスタ17と、N型トランジスタ12,13の接続点15と入力信号線19とを接続するN型MOSトランジスタ18とを有している。P型MOSトランジスタ17およびN型MOSトランジスタ18のゲートは、インバータ回路1の出力信号線20に接続されている。

(もっと読む)

データ出力回路

【課題】マイコンへ入力されるデータの信号線の数を減少させることが可能であるとともに、マイコンに出力されるシリアルデータの出力開始タイミングを変更することなく、シリアルデータを増やすことが可能なデータ出力回路を提供する。

【解決手段】出力データを生成するデータ生成回路と、データ生成回路に対するアドレスを受け付け、アドレスを受け付けている期間に入力されるパラレルデータを保持し、データの出力を指示する出力指示信号に応じて、データ生成回路によって生成される出力データと、保持されたパラレルデータとを、シリアルで出力するシリアル出力回路と、

を備えるデータ出力回路を構成する。

(もっと読む)

信号レベル変換回路、平面表示装置

【課題】 低振幅の入力信号に対しても正常に信号レベル変換が可能であり、動作信頼性が高く、かつ構成が簡素な信号レベル変換回路を提供する。

【解決手段】 互いに同じ極性チャネルのトランジスタであって、低振幅の入力信号INを高振幅の出力信号に変換するための第1及び第2の入力トランジスタ1,2と、第1及び第2の入力トランジスタと同じ極性チャネルのトランジスタであって、電流を供給する第1の電流源15に接続され、入力信号に第1のオフセット電圧を加えて第1の入力トランジスタのゲートに印加する第1のオフセットトランジスタ17と、第1及び第2の入力トランジスタと同じ極性チャネルのトランジスタであって、電流を供給する第2の電流源16に接続され、入力信号に重畳する第1のバイアス電圧VREF’に第2のオフセット電圧を加えて第2の入力トランジスタのゲートに印加する第2のオフセットトランジスタ18とを備える信号レベル変換回路である。

(もっと読む)

回路装置

【課題】製造工程数の削減に寄与する回路装置を提供する。

【解決手段】第1の経路52を通じて電源電圧V10をノードN0に供給し、第2の経路62を通じて電源電圧V−5をノードN0に供給する回路部12であって、回路部12は、第1の経路52上に配されたTFT50と、第1の経路52上に配され、TFT50に接続されたTFT51と、第2の経路62上に配されたTFT60と、第2の経路62上に配され、TFT60に接続されたTFT61と、電源電圧V10とV−5との間の電源電圧V5を、TFT50と51との間に供給するための第3の経路54と、電源電圧V10とV−5との間の電源電圧V0を、TFT60と61との間に供給するための第4の経路64と、を有する。

(もっと読む)

1 - 13 / 13

[ Back to top ]