Fターム[5J056CC30]の内容

Fターム[5J056CC30]に分類される特許

1 - 20 / 36

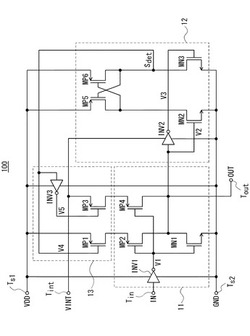

論理回路、半導体集積回路

【課題】供給される電源電圧の変動を抑制することができる論理回路及び当該論理回路が搭載される半導体集積回路を提供すること。

【解決手段】本発明の一態様であるバッファ回路100は、バッファ部11、電圧検出部12及びスイッチ部13を有する。バッファ部11は、電源端子Ts1又は電圧レギュレータ1と電源端子Ts2との間に接続されることにより電源供給され、入力信号INと同論理の信号を出力端子Toutへ出力する。電圧検出部12は、出力端子Toutの電圧を検出し、検出結果に基づく検出信号Sdetを出力する。スイッチ部13は、検出信号Sdetに応じて、バッファ部11を電源端子Ts1又は電圧レギュレータ1と接続する。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

半導体スイッチ

【課題】端子切替時の挿入損失の増加を抑制した半導体スイッチを提供する。

【解決手段】実施形態によれば、電源回路部と制御回路部とスイッチ部とを備えた半導体スイッチが提供される。前記電源回路部は、内部電位生成回路と第1のトランジスタとを有する。前記内部電位生成回路部は、電源線に接続され、入力電位よりも高い第1の電位を生成する。前記第1のトランジスタは、前記内部電位生成回路の入力と出力との間に接続され、前記第1の電位が前記入力電位よりも低下したときオンして前記第1の電位を前記入力電位以上に保持するようにしきい値電圧が設定されたことを特徴とする。前記制御回路部は、前記第1の電位を供給され、ハイレベルまたはローレベルの制御信号を出力する。前記スイッチ部は、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

半導体スイッチ及び無線機器

【課題】オフ歪みを低減した半導体スイッチを提供する。

【解決手段】負の第1の電位を生成する電圧生成回路と、外部から入力される端子切替信号に応じて前記第1の電位を変化させる電圧制御回路と、電源電圧または電源電圧よりも高い正の第2の電位と前記第1の電位とが供給され、前記端子切替信号を入力し前記端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する駆動回路と、SOI基板に設けられ、前記駆動回路の出力により端子間の接続を切り替えるスイッチ部と、を備えたことを特徴とする半導体スイッチが提供される。

(もっと読む)

半導体装置

【課題】省電力化および信頼性の向上、または小面積化を実現可能な半導体装置を提供する。

【解決手段】電源遮断が行われない内部電源Vint0と電源遮断が行われる内部電源Vint1との間を接続する電源スイッチSWと、電源遮断が行われる内部電源Vint1の電圧を判定する内部電圧判定回路VINTDETを設ける。電源遮断が行われる内部電源Vint1は、外部電源Vextからレギュレータ回路VREGを用いて生成する。Vint1の電源遮断時は、SWをオフにし、VREGのオフおよびVREG出力の接地電位GNDへのショートを行い、Vint1の電源復帰時は、VREGのオンおよびショートの解除を行い、上昇したVint1の電圧をVINTDETで判定した上で回路ブロックBLK1の動作開始およびSWのオンを行う。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

半導体装置

【課題】半導体装置に設けられる従来のチャージポンプ回路は電流駆動能力が低下する問題があった。

【解決手段】本発明の半導体装置は、第1の駆動トランジスタP11を介して蓄積された第1のポンピングキャパシタC1の電荷に基づき第1の制御信号を生成する第1チャージポンプ回路11と、第2の駆動トランジスタP21を介して蓄積された第2のポンピングキャパシタC2の電荷に基づき第2の制御信号を生成する第2チャージポンプ回路12と、第3の駆動トランジスタP32を介して端子OUT−端子VSS間の電荷の受け渡しを行う第3のチャージポンプ回路13と、第4の駆動トランジスタP42を介して端子OUT−端子VSS間の電荷の受け渡しを行う第4のチャージポンプ回路14と、を有し、第1、第3の駆動トランジスタは第2の制御信号に基づき導通状態が制御され、第2、第4の駆動トランジスタは第1の制御信号に基づき導通状態が制御される。

(もっと読む)

カップリング回路、このカップリング回路を含むドライバ回路、およびこのカップリング回路の制御方法

【解決手段】p−チャネル電界効果トランジスタタイプの第1および第2のトランジスタ(P1,P2)を備えるカップリング回路において、第1のトランジスタ(P1)のドレイン端子は信号入力端子(1)に接続し、第1および第2のトランジスタ(P1,P2)のソース端子はともに信号出力端子(2)に接続し、第1および第2のトランジスタ(P1,P2)のバルク端子はともに第2のトランジスタ(P2)のドレイン端子に接続し、第1のトランジスタ(P1)のゲート端子は第2のトランジスタ(P2)のゲート端子に接続する。このカップリング回路には、さらに 負電圧を生成する電荷ポンプ回路(110)を含むゲート制御回路(10)も設ける。このゲート制御回路(10)は、負電圧に基づいて、第1および第2のトランジスタ(P1,P2)のゲート端子におけるゲート電圧を制御する。 (もっと読む)

レベルシフタ、集積回路、システム、およびレベルシフタの動作方法

【課題】 レベルシフタ、集積回路、システムおよびレベルシフタの動作方法を提供する。

【解決手段】 第1電圧状態から第2電圧状態への第1状態遷移を含む入力電圧信号を受けるように構成された入力端、第3電圧状態から入力電圧信号の第1状態遷移に対応した第2電圧状態への第2状態遷移を有する出力電圧信号を出力するように構成された出力端、及び入力端と出力端の間に結合され、第1トランジスタと第2トランジスタを含み、第1電圧状態と第2電圧状態の電圧レベルの約平均値に対応した時間からほぼ直ちに、第2電圧状態がトランジスタのゲートに実質的に印加されることがなくなり、第1トランジスタを実質的にオフにするドライバ段を含むレベルシフタ。

(もっと読む)

電力調整装置およびLEDドライバ

【課題】制御信号を用いて電力を多段階制御する電子機器、および2段階制御する電子機器の何れにも適用可能でありながら、極力簡易な制御信号が与えられるだけで適切に電力を調整し得る電力調整装置を提供する。

【解決手段】第1状態または第2状態をとる制御信号を受付け、制御信号に基づいて、所定装置に供給される電力を調整するものであって、制御信号が第1状態から第2状態に遷移した場合、遷移時点から所定の判定時間が経過するまでに、制御信号が第1状態に戻ったかを判定する機能と、戻った場合には、第1方式によって電力を現状と異なる値に調整し、戻らなかった場合には、第2方式によって電力を現状と異なる値に調整する機能を備え、第1方式は、制御信号に基づき、電力を2段階以上に設定された各値の何れかに調整する方式であり、第2方式は、電力を所定値に調整する方式である電力調整装置とする。

(もっと読む)

高周波半導体スイッチ装置

【課題】各FETの端子間にかかる電圧を抑えつつ、高周波特性の優れた高周波半導体スイッチ装置を提供する。

【解決手段】高周波スイッチ部1に制御信号を供給する駆動回路は、第1のレベルシフト回路11と第2のレベルシフト回路12とを有し、これらはSOI構造の半導体装置に設けられ、第1のレベルシフト回路11のクロスカップルPMOSP11、P12に、ゲートに第1のバイアス電位Vb1(>0)が与えられるカスコード接続PMOSP13、P14を接続し、これらの接続ノードを第2のレベルシフト回路12の入力とし、第2のレベルシフト回路12にPMOSP23、P24およびNMOSN21、N22のカスコード接続段を設け、PMOSP23、P24のゲートには第1のバイアス電位Vb1が、NMOSN21、N22のゲートには第2のバイアス電位Vb2(>Vb1)が与えられる。

(もっと読む)

電圧ストレスを低減したゲート制御回路のための回路および方法

【課題】素子にかかる電圧ストレスを低減したゲート制御回路を提供する。

【解決手段】供給電圧より高電圧レベルの出力を供給してトランスファゲートP2を制御するMOSトランジスタ回路において、2つのクランプ回路CLAMP1,CLAMP2が設けられる。第1クランプ回路CLAMP1は、ポンプ電圧を供給するPMOSトランジスタP1のドレイン/ソースが所定電圧を超えないように、トランジスタP1のゲートとソース/ドレインとの間の電圧を確保する。第2クランプ回路CLAMP2は、NMOSトランジスタN1のゲートと同トランジスタN1のドレイン/ソースに接続される出力との間の電圧が所定量を超えないように保証する。2つのクランプ回路は、ゲートとソース/ドレインとの間の電圧を確保することによりドレイン/ソース端子が所定電圧を超えないようにし、それによりトランジスタP2にかかるゲートストレスを低減する。

(もっと読む)

半導体集積回路

【課題】ループフィルタのオンチップ化を可能とし高速応答を実現しロック後に十分な雑音抑圧効果を得るPLL回路を内蔵する半導体集積回路を提供する。

【解決手段】位相周波数比較器1、第1と第2のチャージポンプ2、3、ループフィルタ4、電圧制御発振器5、分周器6を含むPLL回路を内蔵する。PLL回路の動作モードは、ロック動作が停止されたスタンバイ状態と、ロック動作を開始するロック応答動作と、ロック応答動作によって開始されたロック動作を継続する定常ロック動作とを含む。定常ロック動作では、第1のチャージポンプ2の充放電電流よりも、第2のチャージポンプ3の充放電電流が小さく設定され、第1と第2のチャージポンプ2、3は、位相周波数比較器1の出力に応答してループフィルタ4の互いに逆相の充放電動作を実行する。ロック動作を開始するロック応答動作では、逆位相の前記第2のチャージポンプ3による充放電動作が停止される。

(もっと読む)

負電圧検知回路及び負電圧検知回路を備えた半導体集積回路

【課題】本発明は、基準電流からミラー電流を生成するカレントミラー回路における温度、電源電圧の変動に伴うトランジスタの動作のずれを修正して最適な動作点を維持する。

【解決手段】温度検知回路31を有し、カレントミラー回路を構成する第1、第2のMOSトランジスタ回路32、33のトランジスタのディメンジョンサイズを温度検知回路31で発生される制御信号に応じて変更する。

(もっと読む)

負電圧検知回路及びこの負電圧検知回路を用いた半導体集積回路装置

【課題】温度変動や製造プロセスのバラツキの影響を受け難く、より精度の高い負電圧検知を実現できる負電圧検知回路を提供する。

【解決手段】負電圧検知回路は、基準電流Irefを生成する基準電流生成回路37と、一端に検知すべき負電圧が印加され、他端に上記基準電流のミラー電流が供給される抵抗分割回路38と、上記基準電流に対応する第1の電圧Vrefと抵抗分割回路にミラー電流を流したときの他端の第2の電圧とを比較する第1のコンパレータ32を備える。基準電流生成回路は、カレントミラー回路から供給される電流に基づいて負及び正の温度係数を持った第3,第4の電圧をそれぞれ生成する第1,第2の回路部と、第1の電圧を生成する第3の回路部、及び第3の電圧と第4の電圧の電圧差が一致するように、カレントミラー回路を制御する第2のコンパレータ31とを備える。

(もっと読む)

半導体装置

【課題】使用される外部電源電圧のレベルに応じて効率的に内部電圧を生成することのできる半導体装置を提供する。

【解決手段】容量素子(180、184、191)のチャージポンプ動作により内部電圧(Vpp)を生成する回路において、出力トランジスタ(192)に結合される内部電荷供給ノード(ND53)および内部電荷供給ノードに電荷を容量素子(191)を介して供給するドライバ(185、186)の電源ノードのいずれかに制御信号に応答するチャージポンプ容量素子(187)を選択的に結合する。

(もっと読む)

半導体集積回路装置

【課題】 低電力で動作する半導体集積回路装置を提供する。

【解決手段】 半導体集積回路装置は、論理ブロックと、論理ブロックに供給される電力を制御する電力制御回路と、を含み、電力制御回路は、データ保持モード時に論理ブロックに格納されたデータを保持するのに必要な最小の動作電圧を供給するように構成される。

(もっと読む)

半導体回路装置

【課題】待機モード時の論理が不定の論理回路のリーク電流を低減する。

【解決手段】待機モード時の出力論理レベルが互いに同じになるインバータ30をバッファ電源線24とバッファ接地線28との間に接続し、待機モード時の出力論理レベルが上記と異なるが互いに同じになるインバータ32をバッファ電源線22とバッファ接地線26の間に接続し、ラッチ回路44の出力信号に応じて電源セレクタ34,36でバッファ電源線22,24をメイン電源線10かサブ電源線12に接続し、電源セレクタ38,40でバッファ接地線26,28をメイン接地線16かサブ接地線18に接続する。

(もっと読む)

スイッチング動作速度を増加させるブースト回路を含む高電圧スイッチ回路およびこれを含むフラッシュメモリ装置

【課題】フラッシュメモリ装置において、スイッチング動作速度を向上させるとともに、出力される高電圧のノイズ成分を減少させる。

【解決手段】イネーブル信号に応答して出力ノードを設定された電圧にプリチャージするイネーブル制御回路と、出力ノードがプリチャージされるとき出力ノードで発生するスイッチ制御電圧に応答して入力ノードにフィードバック電圧を供給するフィードバック回路と、クロック信号に応答してフィードバック電圧をブーストしブースト電圧を出力ノードに出力することによりスイッチ制御電圧を増加させるブースト回路と、スイッチ制御電圧に応答してオンまたはオフされオンされるときに高電圧を受信して出力する高電圧スイッチとを備えて、高電圧スイッチ回路を構成する。ブースト回路は、クロスカップルドタイプの増幅回路を含む。

(もっと読む)

半導体装置

【課題】高速動作が可能でスタンバイ電流が低い半導体装置を提供する。

【解決手段】この半導体集積回路装置では、メモリマクロM1〜M6用の電源回路部P1〜P6のそれぞれに負電圧発生回路2を設けたので、負電圧VNEGの変動に対する応答性が速くなる。また、スタンバイモード時には、メモリマクロM1〜M6用の負電圧供給線L1〜L6をスイッチ回路SW2〜SW6によって接続し、6つの電源回路部P1〜P6の負電圧発生回路2のうちの1つの電源回路部P1の負電圧発生回路2のみを活性化させるので、スタンバイ電流の増大を防止できる。

(もっと読む)

1 - 20 / 36

[ Back to top ]