Fターム[5J056HH01]の内容

論理回路 (30,215) | 基板構造、製造時の特徴 (247) | チャネル(ゲート)幅 (58)

Fターム[5J056HH01]に分類される特許

1 - 20 / 58

レベルシフト回路

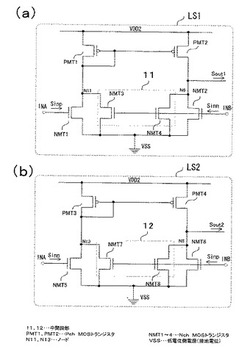

【課題】レベルシフト回路のデータレートの変化時に発生するスキューを抑制する。

【解決手段】一つの実施形態によれば、レベルシフト回路には第1及び第2のレベルシフタが設けられる。第1のレベルシフタは、第1乃至4のトランジスタが設けられ、レベルシフトされた第1の出力信号を出力する。第2のレベルシフタは、第5乃至8のトランジスタが設けられ、レベルシフトされた第1の出力信号とは逆位相の第2の出力信号を出力する。第1の入力信号が入力される第1のトランジスタと差動対をなす第2のトランジスタに、第1の入力信号とは逆位相のハイレベルの第2の入力信号が入力されると第3及び4のトランジスタも同時にオンする。第2の入力信号が入力される第5のトランジスタと差動対をなす第6のトランジスタに、ハイレベルの第1の入力信号が入力されると第7及び8のトランジスタも同時にオンする。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、クロックツリーにおける消費電流を削減しながら、同期回路間の同期動作を行うことが難しかった。

【解決手段】本発明にかかる半導体装置は、動作クロック信号CLKに応じて第1のクロック信号を出力し、第1の応答時間で第1のクロック信号のエッジを変化させる第1のクロックバッファ(VCB11〜VCB14のうちの一つ)と、動作クロック信号CLKに応じて第2のクロック信号を出力し、第2の応答時間で第2のクロック信号のエッジを変化させる第2のクロックバッファ(VCB11〜VCB14のうちの他の一つ)と、第1のクロック信号に同期して動作し、第1の電圧レベルを閾値電圧とする第1の論理回路と、第2のクロック信号に同期して動作し、第2の電圧レベルを閾値電圧とする第2の論理回路と、を有し、第1、第2の論理回路は、動作クロック信号に応じて一のタイミングで動作する。

(もっと読む)

半導体装置

【課題】出力特性の自動調整が可能で、かつ低電力で動作できる高速デジタル出力ドライバを有する半導体装置を提供する。

【解決手段】出力用ドライバ3は、参照電流Iref2の大きさに応じて、出力特性の調整が可能なスケーラブル低電圧信号方式のドライバである。出力用ドライバレプリカ4は、出力用ドライバを複製したものであり、自身の出力と基準電圧との差に基づいて、参照電流Iref2の大きさを調整して出力用ドライバ3へ出力する。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジスタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトランジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

レベルコンバータ回路を備えたMOSトランジスタ回路

【課題】動作上の欠点を除去し、また、用いるトランジスタ数が少ない静的動作のレベルコンバータ回路を備えたMOSトランジスタ回路を提供する。

【解決手段】高電源電圧回路側の第一のCMOSインバータの遷移領域TRHが、低電源電圧回路側の第二のCMOSインバータの出力論理信号の変化範囲に含まれるように前記第一のCMOSインバータと前記第二のCMOSインバータの動作を設定し、第一のCMOSインバータをレベル変換回路とし、第一のCMOSインバータを第二のCMOSインバータの出力で駆動するように構成する。

(もっと読む)

単相差動変換回路

【課題】

正相出力信号と逆相出力信号とが180°の位相差で位相が一致する単相差動変換回路を提供する。

【解決手段】

単相差動変換回路は,単相入力信号が入力される入力端子と,正相出力信号が出力される正相出力端子と,正相出力信号と差動関係にある逆相出力信号が出力される逆相出力端子と,入力端子と正相出力端子との間に設けられ,直列に接続された第1,第2のインバータを少なくとも含む第1のインバータ列と,入力端子と逆相出力端子との間に設けられ,直列に接続された第3,第4,第5のインバータを少なくとも含み第1のインバータ列よりも段数が1段多い第2のインバータ列とを有し,第1のインバータ列は,さらに,第1のインバータの出力端子にドレインが接続され,導通しない電圧にゲートが接続されたトランジスタを有するダミーインバータを有する。好ましくは,第1,第2,ダミー,第3,第4,第5のインバータのゲート幅の比が,m/2:m2:m/2:1:m:m2であり,前記mはインバータの増倍率である。

(もっと読む)

電流消耗を減らす構造を有する半導体装置及びそのターミネーション方法

【課題】電流消耗を減らすオン・ダイ・ターミネーション(ODT)構造を有する半導体装置及びそのターミネーション方法を提供する。

【解決手段】基準電圧と外部抵抗とが連結されたキャリブレーション端子の電圧に応答してキャリブレーションコードを発生させるキャリブレーション回路と、キャリブレーションコードとODT制御信号とに応答して、データ入出力パッドのターミネーション抵抗値を制御するODT装置と、を備え、データ入出力パッドのターミネーション抵抗値は、キャリブレーション端子の抵抗値より大きい半導体装置である。

(もっと読む)

レベルシフト回路及びそれを内蔵した半導体集積回路

【課題】2つの入力信号が共にローレベルとなっても、レベルシフト回路の出力信号を特定のレベルに固定して、次段の回路の誤動作を防止する。

【解決手段】このレベルシフト回路は、第1の電源電位が供給されて動作する回路から入力される互いに逆相の第1の信号及び第2の信号に基づいて、第1の電源電位よりも高い第2の電源電位に対応する振幅を有する第3の信号を出力する電圧変換部と、第1のPチャネルトランジスタ及び第1のNチャネルトランジスタによって構成され、第3の信号を反転して出力端子から出力信号を出力するインバータと、第1のNチャネルトランジスタのソースと接地電位との間に接続され、第1及び第2の信号によってそれぞれ制御される第2及び第3のNチャネルトランジスタと、第2の電源電位とインバータの出力端子との間に接続され、微小電流を流すインピーダンス素子とを具備する。

(もっと読む)

駆動回路

【課題】動作速度が低下する問題があった。

【解決手段】本発明は、外部負荷回路にLVDS信号を出力する駆動回路であって、前記外部負荷回路が接続される第1、第2のノードと、前記第1のノードを共通ノードとし、直列接続された第1及び第2のスイッチング素子を有する第1の直列回路と、前記第2のノードを共通ノードとし、直列接続された第3及び第4のスイッチング素子を有する第2の直列回路と、前記第1、第2の直列回路に所定の電流を出力する第1の電流源と、を有し、前記第1及び第2のスイッチング素子、もしくは、前記第1の電流源の少なくともどれかが備える第1導電型のトランジスタのバックゲートが順バイアスとなっている駆動回路である。

(もっと読む)

レベルシフト回路、表示装置および電子機器

【課題】貫通電流を抑えつつ大振幅のレベル変換を実現可能なインバータ型のレベルシフト回路を提供する。

【解決手段】インバータ型のレベルシフト回路10において、初段のCMOSインバータ回路11のnチャネルトランジスタ112のサイズを、pチャネルトランジスタ111のサイズのa倍(例えば、100倍)以上の極端なサイズ差に設定する。このサイズ比により、貫通電流を抑えつつ、例えば0−3V振幅から0−12V振幅にレベル変換する場合のような大振幅のレベル変換を実現する。

(もっと読む)

半導体装置

【課題】オフリーク電流の温度特性が互いに異なる複数の回路ブロックに対して電源制御を行うことにより、消費電力を低減する。

【解決手段】オフリーク電流が第1の温度特性を有するトランジスタによって構成された第1のXデコーダ12と、オフリーク電流が第2の温度特性を有するトランジスタによって構成されたプリデコーダ13及び周辺回路14と、スタンバイ時において温度が第1のしきい値を超えている場合、Xデコーダ12を非活性化させる電源制御回路16と、スタンバイ時において温度が第2のしきい値を超えている場合、プリデコーダ13及び周辺回路14を非活性化させる電源制御回路17とを備える。本発明によれば、複数の回路ブロックに対する電源制御の有無を、互いに異なる温度を基準として判断していることから、各回路ブロックに対して最適な電源制御を行うことが可能となる。

(もっと読む)

半導体集積回路

【課題】トランジスタの特性ばらつきによる遅延回路の遅延時間の変動を抑制することが可能で、更に、製造工程における加工ばらつきに強く、レイアウト拡張性に優れた半導体集積回路を小面積に提供する。

【解決手段】第1の電源VDDと第2の電源(接地電源)との間に直列に接続されたP型MOSトランジスタMP11と2以上のN型MOSトランジスタMN11、MN12とが備えられる。入力端子INは前記P型MOSトランジスタMP11のゲート端子と前記N型MOSトランジスタMN11、MN12のゲート端子とに接続される。更に、P型MOSトランジスタMP11とN型MOSトランジスタMN11の接点である出力端子OUTに接続した1以上の容量素子C1を有し、P型MOSトランジスタMP11の駆動能力を、2以上に直列接続したN型MOSトランジスタMN11、MN12の総駆動能力よりも大きく構成する。

(もっと読む)

半導体装置

【課題】出力バッファのインピーダンス調整を行う半導体装置を提供する。

【解決手段】制御回路1は、外部からの読み出しまたは書き込みコマンドに応じてDQイネーブル信号を発生する。コマンドラッチ回路2Aは、外部からのコマンド信号(ZQコマンド)に応じて、ZQEnable信号を発生する。ZQ調整回路3は、ZQEnable信号が入力されると、内部に設けられたレプリカ回路のインピーダンス調整を始める。ZQ調整回路3は、DQイネーブル信号が入力される期間中は、インピーダンス調整結果であるドライバコードのDQ回路4への出力を禁止する。

(もっと読む)

半導体装置

【課題】集積回路を構成するMISFETの処理速度の向上とリーク電流の低減を両立させ、かつ、半導体装置の小型化を達成することができる技術を提供する。

【解決手段】単体のMISFETから構成される回路素子に代えて、しきい値電圧の異なる複数のMISFETからなる同一ノードトランジスタから回路素子を構成する。例えば、図2に示すように、nチャネル型MISFET1aとnチャネル型MISFET1bを並列接続しかつ、それぞれのゲート電極Gを電気的に接続する。このとき、例えば、nチャネル型MISFET1aを高VthMISFETから構成し、nチャネル型MISFET1bを低VthMISFETから構成する。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路において、回路面積の増加やプロセスコストの増大を招くことなく、入力信号の電源電圧を低電圧化した場合にも、レベルシフト動作を確実に実行可能にする。

【解決手段】入力信号およびその反転信号を一対の相補信号としてゲートに受ける一対のN型トランジスタについて、単位ゲート幅サイズを小さくすることが可能なレイアウトを採用する。このレイアウト構成は、ドレイン4およびソース5を構成する、分割された複数の長方形の拡散領域1A,1Bと、各拡散領域1A,1Bの短辺の方向をゲート幅方向として、ゲート長方向に並べて配置された、複数のゲート3とを備え、各ゲート3同士、各ドレイン4同士、および各ソース5同士が電気的に接続されている。

(もっと読む)

バッファ回路及び表示装置

【課題】片チャネルで構成されたブートストラップ方式のインバータを多段に接続して構成される回路において、遅延時間を小さくする。

【解決手段】バッファ回路1は、同一導電型FETを用いたブートストラップ方式のインバータUa1〜Uanを備える。初段のインバータから最終段の直前のインバータまでのうち任意のインバータと、当該任意のインバータの直後のインバータとの駆動能力比は、8〜16倍に設定される。これにより、負荷容量CLを充分駆動することができ、且つ、インバータUa1〜Uanの段数を最小にすることができる。

(もっと読む)

半導体集積回路

【課題】近年の高集積化、高速化が要求される半導体集積回路においても、入出力回路における複数の出力バッファ回路が同時に動作することにより発生する同時動作スイッチングノイズに起因する内部回路の誤動作を効果的に防止することが可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、内部回路1と、複数の入出力回路20とを有し、前記内部回路1と入出力回路20との電源は別系統により供給され、前記内部回路1のGNDと前記入出力回路20のGNDとの電位差を検出する差電位検出回路3と、この差電位検出回路3により検出した電位差に基づいて、入出力回路20を構成する入力バッファ回路21で変換された信号が受けたノイズを補正する補正回路4とを有する。

(もっと読む)

信号レベル変換回路、平面表示装置

【課題】 低振幅の入力信号に対しても正常に信号レベル変換が可能であり、動作信頼性が高く、かつ構成が簡素な信号レベル変換回路を提供する。

【解決手段】 互いに同じ極性チャネルのトランジスタであって、低振幅の入力信号INを高振幅の出力信号に変換するための第1及び第2の入力トランジスタ1,2と、第1及び第2の入力トランジスタと同じ極性チャネルのトランジスタであって、電流を供給する第1の電流源15に接続され、入力信号に第1のオフセット電圧を加えて第1の入力トランジスタのゲートに印加する第1のオフセットトランジスタ17と、第1及び第2の入力トランジスタと同じ極性チャネルのトランジスタであって、電流を供給する第2の電流源16に接続され、入力信号に重畳する第1のバイアス電圧VREF’に第2のオフセット電圧を加えて第2の入力トランジスタのゲートに印加する第2のオフセットトランジスタ18とを備える信号レベル変換回路である。

(もっと読む)

インバータ回路

【課題】有機トランジスタのサイズを適切にするとともにトランジスタの伝達特性においてゲインを充分なものにする、という措置を取らなくても、大きなゲインを獲得することのできるインバータ回路を提供する。

【解決手段】本発明に係るインバータ回路は、第1の有機トランジスタおよび第2の有機トランジスタが1つのインバータ段として機能するように構成されるものであり、第5の有機トランジスタおよび第6の有機トランジスタの各々が第3の有機トランジスタおよび第4の有機トランジスタによって制御され、かつ、第1のゲートおよび第2のゲートの各々に給電するものであり、前記第3の有機トランジスタ〜前記第6の有機トランジスタが、前記第1のゲートの入力電圧の上昇時に前記第2のゲートの電圧が降下し、前記第2のゲートの入力電圧の上昇時に前記第1のゲートの電圧が降下するよう、バイアス制御段として機能するように構成されるものである。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

1 - 20 / 58

[ Back to top ]