半導体装置

【課題】従来の半導体装置では、クロックツリーにおける消費電流を削減しながら、同期回路間の同期動作を行うことが難しかった。

【解決手段】本発明にかかる半導体装置は、動作クロック信号CLKに応じて第1のクロック信号を出力し、第1の応答時間で第1のクロック信号のエッジを変化させる第1のクロックバッファ(VCB11〜VCB14のうちの一つ)と、動作クロック信号CLKに応じて第2のクロック信号を出力し、第2の応答時間で第2のクロック信号のエッジを変化させる第2のクロックバッファ(VCB11〜VCB14のうちの他の一つ)と、第1のクロック信号に同期して動作し、第1の電圧レベルを閾値電圧とする第1の論理回路と、第2のクロック信号に同期して動作し、第2の電圧レベルを閾値電圧とする第2の論理回路と、を有し、第1、第2の論理回路は、動作クロック信号に応じて一のタイミングで動作する。

【解決手段】本発明にかかる半導体装置は、動作クロック信号CLKに応じて第1のクロック信号を出力し、第1の応答時間で第1のクロック信号のエッジを変化させる第1のクロックバッファ(VCB11〜VCB14のうちの一つ)と、動作クロック信号CLKに応じて第2のクロック信号を出力し、第2の応答時間で第2のクロック信号のエッジを変化させる第2のクロックバッファ(VCB11〜VCB14のうちの他の一つ)と、第1のクロック信号に同期して動作し、第1の電圧レベルを閾値電圧とする第1の論理回路と、第2のクロック信号に同期して動作し、第2の電圧レベルを閾値電圧とする第2の論理回路と、を有し、第1、第2の論理回路は、動作クロック信号に応じて一のタイミングで動作する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関し、特に装置内の複数の論理回路にクロック信号を分配するクロック分配網を有する半導体装置に関する。

【背景技術】

【0002】

近年の半導体装置では、クロック信号に同期して信号を伝達する同期回路(例えば、フリップフロップ)が多く用いられている。このような半導体装置では、複数のフリップフロップにクロック信号が同時に入力されるように回路を構成する必要がある。しかしながら、クロック信号を複数のフリップフロップに分配する配線網には、寄生抵抗及び寄生容量が形成される。そのため、この寄生抵抗及び寄生容量に起因して、クロック信号がフリップフロップに到達するまでの時間に配線距離に応じた差が生じる。

【0003】

そこで、半導体装置の設計ではクロックツリー合成(Clock Tree Synthesis)処理により、クロックツリーを形成する。このクロックツリーには、クロック信号の伝達経路上に複数のCTSバッファが形成される。また、CTSバッファは、クロック信号を遅延させて次段に形成されるCTSバッファ又は回路に伝達する。つまり、CTSバッファは、フリップフロップ毎のクロックスキューを調節する。そして、クロックツリーを介してクロック信号を複数のフリップフロップに分配することで、複数のフリップフロップにクロック信号が同時に到達する。このようなCTS技術が特許文献1〜7に記載されている。

【0004】

しかし、クロックツリーを用いてクロック信号を複数のフリップフロップに分配した場合、同時に多数のフリップフロップ及びCTSバッファが動作する。そのため、論理回路で扱われる信号の論理レベルの切り替わりに応じて一度に多くの貫通電流が発生する。そして、この貫通電流が電源配線及び接地配線を流れた場合、当該電流がパッケージのインダクタンス及び寄生容量を介して流れ、電源ノイズが生じる。また、電源ノイズが回路の電気的特性に影響を及ぼす。そして、影響が大きくなると回路動作に不具合を生じることがある。

【0005】

そこで、このような回路素子の同時動作に起因して生じる貫通電流を抑制して電源ノイズを低減する技術が特許文献8に開示されている。特許文献8では、1チップでASIC(Application Specific Integrated Circuit)を構成する際に、ASIC内の回路を複数のブロックに分割する。そして、クロック信号の伝搬遅延時間をブロック毎に異なる値に設定する。これにより、特許文献8では、同時動作する回路素子の数を低減して、貫通電流のピーク値を低減する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−234226号公報

【特許文献2】特開2004−241699号公報

【特許文献3】特開2004−013979号公報

【特許文献4】特開2001−175699号公報

【特許文献5】特開2001−022816号公報

【特許文献6】特開2000−353745号公報

【特許文献7】特開2000−294737号公報

【特許文献8】特開2006−165099号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献8に記載の技術では、ブロック毎に回路の動作タイミングが異なるため、ブロック間で動作の整合整を保つことができない問題がある。

【課題を解決するための手段】

【0008】

本発明にかかる半導体装置の一態様は、動作クロック信号に応じて第1のクロック信号を出力し、第1の応答時間で前記第1のクロック信号のエッジを変化させる第1のクロックバッファと、前記動作クロック信号に応じて第2のクロック信号を出力し、前記第1の応答時間とは異なる第2の応答時間で前記第2のクロック信号のエッジを変化させる第2のクロックバッファと、前記第1のクロック信号に同期して動作し、第1の電圧レベルを前記第1のクロック信号の閾値電圧とする第1の論理回路と、前記第2のクロック信号に同期して動作し、前記第1の電圧レベルとは異なる第2の電圧レベルを前記第2のクロック信号の閾値電圧とする第2の論理回路と、を有し、前記第1、第2の論理回路は、前記動作クロック信号に応じて一のタイミングで動作する。

【0009】

本発明にかかる半導体装置の別の態様は、動作クロック信号を伝達し、出力部を構成するPチャネルトランジスタとNチャネルトランジスタの駆動能力の比が異なる複数の可変クロックバッファと、前記複数の可変クロックバッファのそれぞれに対応して設けられ、対応する前記可変バッファを介して前記動作クロック信号が入力されるフリップフロップと、を有し、前記フリップフロップの前記動作クロック信号の入力部は、対応する前記可変クロックバッファの駆動能力の比に応じてPチャネルトランジスタとNチャネルトランジスタとの駆動能力の比が決定される。

【0010】

本発明にかかる半導体装置の別の態様は、第1の応答時間を有する第1のCTSバッファと、前記第1のCTSバッファに結合され、前記第1のCTSバッファの出力信号のエッジに応答して一のタイミングで動作するように閾値電圧が設定された第1のフリップフロップと、前記第1の応答時間とは異なる第2の応答時間を有する第2のCTSバッファと、前記第2のCTSバッファに結合され、前記第2のCTSバッファの出力信号のエッジに応答して前記一のタイミングで動作するように閾値電圧が設定された第2のフリップフロップと、を有する。

【0011】

本発明にかかる半導体装置では、論理回路(又はフリップフロップ)に動作クロック信号を伝達するクロックバッファが、クロックバッファ毎に異なるタイミングで動作クロック信号のエッジを変化させる。これにより、クロックバッファ毎に消費電流のピークが生じるタイミングがずれて、消費電流のピーク値を抑制することができる。さらに、本発明にかかる半導体装置では、論理回路(又はフリップフロップ)における動作クロック信号に対する閾値が論理回路毎に異なる。そして、本発明にかかる半導体装置では、異なるタイミングでエッジが変化する動作クロック信号を受信して、一のタイミングで論理回路が動作する。

【発明の効果】

【0012】

本発明にかかる半導体装置は、消費電流のピーク値を抑制しながら論理回路を一のタイミングで動作させることができる。

【図面の簡単な説明】

【0013】

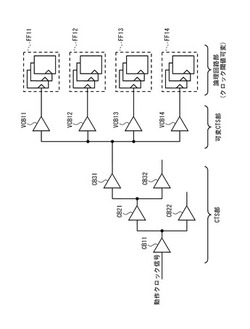

【図1】実施の形態1にかかる半導体装置のクロック分配網のブロック図である。

【図2】実施の形態1にかかる可変クロックバッファのブロック図である。

【図3】実施の形態1にかかる可変クロックバッファの駆動能力の違いを示す表である。

【図4】実施の形態1にかかるフリップフロップの動作クロック信号の入力部の回路図である。

【図5】実施の形態1にかかるフリップフロップの入力部の駆動能力の違いを示す表である。

【図6】実施の形態1にかかる可変クロックバッファとフリップフロップの動作を示すタイミングチャートである。

【図7】実施の形態1にかかる半導体装置の可変クロックバッファの消費電流を示すタイミングチャートである。

【発明を実施するための形態】

【0014】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。本発明は、半導体装置内に設けられるクロック分配網を構成するクロックバッファと、当該クロック分配網から動作クロック信号の供給を受ける論理回路(例えば、フリップフロップ)と、に特徴の一つを有する。そこで、以下では、半導体装置内のクロック分配網、クロックバッファ、及び、クロック分配網から動作クロック信号の供給を受ける論理回路部について特に詳細に説明を行う。つまり、本発明にかかる半導体装置は、以下で説明する動作クロック信号に基づき動作するフリップフロップ等と、以下では説明しない他の回路と、を含む。

【0015】

まず、図1に本発明にかかる半導体装置内に設けられるクロック分配網と当該クロック分配網から動作クロック信号を受ける論理回路部のブロック図を示す。図1に示すように、クロック分配網は、CTS部と、可変CTS部を有する。

【0016】

CTS部は複数のクロックバッファを有する。そして、CTS部では、このクロックバッファを介してツリー状のクロック分配網を構成する。図1に示す例では、クロックバッファCB11、CB21、CB22、CB31、CB32を示した。そして、図1に示す例では、クロックバッファCB11により動作クロック信号をクロックバッファCB21とクロックバッファCB22に分配する。また、クロックバッファCB21は、入力された動作クロック信号をクロックバッファCB31、CB32に分配する。そして、クロックバッファCB31は、可変CTS部に動作クロック信号を分配する。なお、クロックバッファCB22、CB32は、図示しないクロックバッファ又は論理回路に動作クロック信号を分配する。

【0017】

可変CTS部は、複数の可変クロックバッファを有する。図1に示す例では、クロックバッファCB31に対応して設けられる一群の可変クロックバッファのみを示した。図1に示す例では、一群の可変クロックバッファとして可変クロックバッファVCB11〜VCB14を示した。なお、一群の可変クロックバッファは、一の動作クロック信号に基づき、エッジの変化タイミングが異なる一群の動作クロック信号を出力する。

【0018】

論理回路部は、複数の論理回路を有する。この複数の論理回路のうち、クロック信号に同期して動作する論理回路を特に同期回路と称す。この同期回路は、例えば、フリップフロップである。そこで、図1に示す例では、複数のフリップフロップを論理回路部として示した。また、実施の形態1にかかる半導体装置では、複数のフリップフロップを、対応する可変クロックバッファVCB11〜VCB14に対応するフリップフロップ群FF11〜FF14を有する。

【0019】

フリップフロップ群FF11は、可変クロックバッファVCB11を介して動作クロック信号の供給を受ける。フリップフロップ群FF12は、可変クロックバッファVCB12を介して動作クロック信号の供給を受ける。フリップフロップ群FF13は、可変クロックバッファVCB13を介して動作クロック信号の供給を受ける。フリップフロップ群FF14は、可変クロックバッファVCB14を介して動作クロック信号の供給を受ける。

【0020】

ここで、実施の形態1にかかる半導体装置では、可変クロックバッファVCB11〜VCB14のうちの一つを第1の可変クロックバッファ、他の一つを第2の可変クロックバッファとした場合に、第1の可変クロックバッファは第1のクロック信号を出力し、第2の可変クロックバッファは第2のクロック信号を出力する。また、第1の可変クロックバッファは、第1の応答時間で第1のクロック信号のエッジを変化させ、第2の可変クロックバッファは、第2の応答時間で第2のクロック信号のエッジを変化させる。

【0021】

さらに、実施の形態1にかかる半導体装置では、フリップフロップ群FF11〜FF14のうち第1の可変クロックバッファから第1のクロック信号の供給を受けるフリップフロップ群に属するフリップフロップを第1のフリップフロップとし、第1の可変クロックバッファから第1のクロック信号の供給を受けるフリップフロップ群に属するフリップフロップを第1のフリップフロップとする。このとき、実施の形態1にかかる半導体装置では、この第1のフリップフロップは第1のクロック信号に対する閾値を第1の電圧レベルとし、第2のフリップフロップは第2のクロック信号に対する閾値を第2の電圧レベルとする。そして、第1のフリップフロップと第2のフリップフロップは、一のタイミングで動作する。

【0022】

以下では、可変クロックバッファ及びフリップフロップの詳細な構成について説明する。まず、可変クロックバッファの回路図を図2に示す。可変クロックバッファVCB11〜VCB14は、流出電流による駆動能力と流入電流による駆動能力との比が異なるが、基本的な回路構成は同じである。図2に示すように、可変クロックバッファは、前段バッファ10と出力部11とを有する。前段バッファ10は、例えば、インバータ回路であって、高入力インピーダンス・低出力インピーダンスの回路である。また、前段バッファ10は、1段のインバータにより構成しても良く、多段のインバータにより構成しても良い。なお、多段のインバータにより構成する場合は、後段になるほど駆動能力の高いインバータを配置することが好ましい。また、前段バッファ10は、入力閾値電圧として電源電圧の約半分の電圧レベルを有するものとする。さらに、前段バッファ10は、流出電流による駆動能力と流入電流による駆動能力との比が1:1であるものとする。

【0023】

出力部11は、高電位側電源端子(例えば、電源端子VDD)と低電位側電源端子(例えば、接地端子VSS)との間に直列に接続された第1導電型トランジスタ(例えば、PチャネルトランジスタMP1)と第2導電型トランジスタ(例えば、NチャネルトランジスタMN1)とを有する。そして、PチャネルトランジスタMP1とNチャネルトランジスタMN1は、インバータを構成する。そして、出力部11は、前段バッファ10が出力する信号を入力信号とし、当該入力信号の反転信号を出力する。以下の説明では、前段バッファ10に入力されるクロック信号にCIN0の符号を付し、前段バッファ10が出力する(又は出力部11に入力される)クロック信号にCIN1の符号を付し、出力部11が出力するクロック信号にCOUTの符号を付す。

【0024】

また、出力部11は、可変クロックバッファVCB11〜VCB14のそれぞれに設けられるが、可変クロックバッファ毎に流入電流による駆動能力と流出電流による駆動能力とが異なる。PチャネルトランジスタMP1のトランジスタサイズKと、NチャネルトランジスタMN1のトランジスタサイズLを可変クロックバッファ毎に変えることで駆動能力の違いを設定する。そこで、可変クロックバッファVCB11〜VCB14のトランジスタサイズの設定値を示す表を図3に示す。なお、図3に示す値は、各可変クロックバッファの出力部11を構成するPチャネルトランジスタMP1のトランジスタサイズKとNチャネルトランジスタMN1のトランジスタサイズLを示している。このとき、トランジスタサイズK(又はL)の値が1のトランジスタは、基準となる駆動能力を発揮するトランジスタである。そして、図3に示すトランジスタサイズK(又はL)の値は、各トランジスタが基準駆動能力の何倍の駆動能力を有するかを示す。

【0025】

図3に示すように、可変クロックバッファVCB11は、Pチャネルトランジスタの駆動能力が1、Nチャネルトランジスタの駆動能力が4である。可変クロックバッファVCB12は、Pチャネルトランジスタの駆動能力が2、Nチャネルトランジスタの駆動能力が3である。可変クロックバッファVCB13は、Pチャネルトランジスタの駆動能力が3、Nチャネルトランジスタの駆動能力が2である。可変クロックバッファVCB14は、Pチャネルトランジスタの駆動能力が4、Nチャネルトランジスタの駆動能力が1である。

【0026】

なお、基準駆動能力を発揮するトランジスタを設計し、駆動能力の倍数に応じて、トランジスタを並列して並べることでトランジスタの駆動能力を設定することができる。また、基準駆動能力を発揮するトランジスタを設計し、トランジスタのゲート幅を駆動能力の倍数に応じた倍数とすることでもトランジスタの駆動能力を設定することができる。

【0027】

図3に示す例では、出力するクロック信号の立ち上がりエッジの応答時間は、可変クロックバッファVCB11が最も長く、可変クロックバッファVCB14が最も短い。また、出力するクロック信号の立ち下がりエッジの応答時間は、可変クロックバッファVCB11が最も短く、可変クロックバッファVCB14が最も長い。つまり、可変クロックバッファは、PチャネルトランジスタMP1の駆動能力がNチャネルトランジスタMN1の駆動能力よりも大きいほど出力するクロック信号の立ち上がりエッジの応答時間が短くなる。また、可変クロックバッファは、NチャネルトランジスタMN1の駆動能力がPチャネルトランジスタMP1の駆動能力よりも大きいほど出力するクロック信号の立ち下がりエッジの応答時間が短くなる。

【0028】

続いて、フリップフロップの詳細について説明する。実施の形態1にかかる半導体装置のフリップフロップは、当該フリップフロップに動作クロック信号を供給する可変クロックバッファの駆動能力に応じてクロック信号に対する閾値電圧に違いを設けている。また、実施の形態1において説明するフリップフロップは、動作クロック信号に対する閾値電圧以外については一般的なフリップフロップと同じである。そこで、以下の説明では、フリップの動作クロック入力部についてのみ説明する。

【0029】

図4にフリップフロップの動作クロック信号CLKの入力部12の回路図を示す。入力部12は、高電位側電源端子(例えば、電源端子VDD)と低電位側電源端子(例えば、接地端子VSS)との間に直列に接続された第1導電型トランジスタ(例えば、PチャネルトランジスタMP2)と第2導電型トランジスタ(例えば、NチャネルトランジスタMN2)とを有する。そして、PチャネルトランジスタMP2とNチャネルトランジスタMN2は、インバータを構成する。そして入力部12は、入力される動作クロック信号CLKの反転信号CRTCを出力する。この反転信号CRTCは、図示しない、ラッチ回路に入力され、当該ラッチ回路に保持されている値の更新状態を制御する。

【0030】

また、入力部12は、フリップフロップ群FF11〜FF14に属するフリップフロップのそれぞれに設けられるが、フリップフロップ群毎に入力部12の動作クロック信号CLKに対する閾値電圧が異なる。PチャネルトランジスタMP2のトランジスタサイズMと、NチャネルトランジスタMN2のトランジスタサイズNをフリップフロップ群毎に変えることで閾値電圧の違いを設定する。そこで、フリップフロップ群FF11〜FF14の入力部12のトランジスタサイズの設定値を示す表を図5に示す。なお、図5に示す値は、フリップフロップ群FF11〜FF14の出力部11を構成するPチャネルトランジスタMP2のトランジスタサイズMとNチャネルトランジスタMN2のトランジスタサイズNを示している。このとき、トランジスタサイズM(又はN)の値が1のトランジスタは、基準となる駆動能力を発揮するトランジスタである。そして、図5に示すトランジスタサイズM(又はN)の値は、各トランジスタが基準駆動能力の何倍の駆動能力を有するかを示す。

【0031】

図5に示すように、フリップフロップ群FF11に属するフリップフロップの入力部12は、Pチャネルトランジスタの駆動能力が1、Nチャネルトランジスタの駆動能力が4である。フリップフロップ群FF11に属するフリップフロップの入力部12は、Pチャネルトランジスタの駆動能力が2、Nチャネルトランジスタの駆動能力が3である。フリップフロップ群FF11に属するフリップフロップの入力部12は、Pチャネルトランジスタの駆動能力が3、Nチャネルトランジスタの駆動能力が2である。フリップフロップ群FF11に属するフリップフロップの入力部12は、Pチャネルトランジスタの駆動能力が4、Nチャネルトランジスタの駆動能力が1である。

【0032】

なお、基準駆動能力を発揮するトランジスタを設計し、駆動能力の倍数に応じて、トランジスタを並列して並べることでトランジスタの駆動能力を設定することができる。また、基準駆動能力を発揮するトランジスタを設計し、トランジスタのゲート幅を駆動能力の倍数に応じた倍数とすることでもトランジスタの駆動能力を設定することができる。

【0033】

ここで、入力部12を構成するトランジスタのトランジスタサイズと入力部12の閾値電圧との関係について説明する。入力部12は、PチャネルトランジスタMP2とNチャネルトランジスタMN2によりインバータを構成する。そこで、インバータの閾値電圧とインバータを構成するトランジスタのトランジスタサイズとの関係を(1)式に示す。

【数1】

(1)式において、Vthはフリップフロップの動作クロック信号CLKの入力部12の閾値電圧であり、Vtnは入力部12を構成するNチャネルトランジスタMN2の閾値電圧であり、Vtpは入力部12を構成するPチャネルトランジスタMP2の閾値電圧であり、VDDは入力部12に与えられる電源電圧である。また、βNは(2)式、βPは(3)式により表される値である。

【数2】

【数3】

なお、(2)式のμnはNチャネルトランジスタMN2のキャリアの移動度であり、CoxはNチャネルトランジスタMN2のゲート容量であり、WnはNチャネルトランジスタMN2のゲート幅であり、LnはNチャネルトランジスタMN2のゲート長である。また、(3)式のμpはPチャネルトランジスタMP2のキャリアの移動度であり、CoxはPチャネルトランジスタMP2のゲート容量であり、WpはPチャネルトランジスタMP2のゲート幅であり、LpはPチャネルトランジスタMP2のゲート長である。

【0034】

上記(1)〜(3)式より、PチャネルトランジスタMP2及びNチャネルトランジスタMN2のゲート長を固定して、ゲート幅(又は並列トランジスタ数)を調節することでインバータの閾値電圧が変化することがわかる。より具体的には、PチャネルトランジスタMP2のゲート幅をNチャネルトランジスタMN2のゲート幅に比べて大きくすると、閾値電圧は電源電圧VDD側にずれる。一方、NチャネルトランジスタMN2のゲート幅をPチャネルトランジスタMP2のゲート幅に比べて大きくすると、閾値電圧は接地電圧VSS側にずれる。

【0035】

図1に示すように、実施の形態1にかかる半導体装置では、フリップフロップの入力部12のPチャネルトランジスタMP1の駆動能力とNチャネルトランジスタMN1の駆動能力との比をフリップフロップに動作クロックを供給する可変クロックバッファの出力部11の駆動能力の比に応じて決定する。つまり、流出側の駆動能力が高い可変クロックバッファには、流出側の駆動能力が高い入力部12を有するフリップフロップを対応させて設ける。また、流入側の駆動能力が高い可変クロックバッファには、流入側の駆動能力が高い入力部12を有するフリップフロップを対応させて設ける。

【0036】

より具体的には、PチャネルトランジスタMP1のトランジスタサイズKが1、NチャネルトランジスタMN1のトランジスタサイズLが4の可変クロックバッファVCB11には、PチャネルトランジスタMP2のトランジスタサイズMが1、NチャネルトランジスタMN2のトランジスタサイズNが4の入力部12を有するフリップフロップ群FF11に属するフリップフロップが設けられる。

【0037】

実施の形態1にかかる半導体装置では、このような対応関係に基づき可変クロックバッファVCB11〜VCB14とフリップフロップ群FF11〜FF14を設ける。これにより、閾値電圧が高い(電源電圧VDDに近い)フリップフロップには、立ち上がりエッジの応答時間が短い動作クロック信号CLKが入力され、閾値電圧が低い(接地電圧VSSに近い)フリップフロップには、立ち上がりエッジの応答時間が長い動作クロック信号CLKが入力される。

【0038】

ここで、実施の形態1にかかる半導体装置における可変クロックバッファVCB11〜VCB14とフリップフロップ群FF11〜FF14との動作を示すタイミングチャートを図6に示す。図6に示すように、可変クロックバッファに入力される動作クロック信号CIN0は、ほとんど遅延なく動作クロック信号CIN1として出力される。ここで、動作クロック信号CIN0、CIN1は、十分な駆動能力を有するバッファにより出力されるため、立ち上がりエッジと立ち下がりエッジは傾きが急峻になる。

【0039】

そして、動作クロック信号CIN1の立ち下がりエッジに応じて、可変クロックバッファは、動作クロック信号COUTを立ち上げる。この動作クロック信号COUTの立ち上がりエッジは、可変クロックバッファVCB11〜VCB14の電流流出駆動能力により異なる傾きとなる。より具体的には、電流流出駆動能力が高い可変クロックバッファVCB14が出力する動作クロック信号COUTの傾きが最も立ち上がりエッジの応答時間が短くなる。一方。可変クロックバッファVCB11は、電流流出駆動能力が最も低いため、可変クロックバッファVCB11が出力する動作クロック信号COUTの応答時間は最も長くなる。

【0040】

そして、可変クロックバッファVCB14が出力する応答時間が短い(立ち上がりエッジの傾きが急峻な)動作クロック信号COUTは、高い閾値電圧を有するフリップフロップ群FF14に属するフリップフロップに入力される。また、可変クロックバッファVCB11が出力する応答時間が長い(立ち上がりエッジの傾きが緩やかな)動作クロック信号COUTは、低い閾値電圧を有するフリップフロップ群FF11に属するフリップフロップに入力される。そして、動作クロック信号COUTのエッジの応答時間とフリップフロップの閾値電圧が上記のような関係を有することで、フリップフロップ群FF11〜FF14に属するフリップフロップに入力される動作クロック信号COUTの電圧レベルは、いずれも、タイミングT1フリップフロップ群FF11〜FF14の閾値電圧Vthを超える。つまり、フリップフロップ群FF11〜FF14に属するフリップフロップは、一のタイミング(図6に示すタイミングT1)で動作する。そして、すべてのフリップフロップ群に属するフリップフロップも一のタイミングで動作することで、属するフリップフロップ群に関わらず、フリップフロップ間での同期動作が可能になる。

【0041】

続いて、可変クロックバッファVCB11〜VCB14の消費電流について説明する。図7に可変クロックバッファVCB11〜VCB14の消費電流の変動を示すタイミングチャートを示す。図7に示すように、可変クロックバッファVCB11〜VCB14は、出力する動作クロック信号COUTの電圧レベルが傾きをもって遷移している期間において消費電流が増大する。そして、この消費電流は、動作クロック信号COUTの電圧レベルが電源電圧VDDの半分の電圧レベル(VDD/2)付近となるタイミングで最も多くなる。そのため、可変クロックバッファVCB11〜VCB14の消費電流Ivcb11〜Ivcb14のピークが生じるタイミングはずれる。そして、この消費電流Ivcb11〜Ivcb14の合計値であるItotalは、可変クロックバッファを用いない場合よりもピーク値が小さくなる。

【0042】

上記説明より、実施の形態1にかかる半導体装置では、可変クロックバッファと、当該可変クロックバッファの駆動能力に応じた閾値電圧を有するフリップフロップと、を有する。これにより、実施の形態1にかかる半導体装置では、可変クロックバッファの動作に起因する消費電流のピーク値を抑制することができる。さらに、実施の形態1にかかる半導体装置では、入力される動作クロック信号の応答時間に応じてフリップフロップの閾値電圧を設定する。これにより、動作クロック信号の応答時間をずらしながら、入力される動作クロック信号の応答時間によらず複数のフリップフロップを一のタイミングで動作させることができる。また、入力される動作クロック信号によらず複数のフリップフロップを一のタイミングで動作させることで、入力される動作クロック信号によらずフリップフロップ間の同期動作を実現することができる。

【0043】

さらに、実施の形態1にかかる半導体装置における可変クロックバッファは、出力部11を構成する2つのトランジスタの駆動能力の比を変えることで消費電流のピークが発生するタイミングをずらすものである。つまり、実施の形態1にかかる半導体装置では、消費電流のピーク発生タイミングをずらすために別途回路を追加する必要がなく、回路面積の増大を防止することができる。

【0044】

さらに、実施の形態1にかかる半導体装置では、可変クロックバッファの出力部11の駆動能力の比と、フリップフロップの入力部12の駆動能力の比と、を対応する比とすることでフリップフロップ間の動作タイミングを一致させる。つまり、動作クロック信号のずれに応じて、フリップフロップの動作タイミングをずらすために、別途回路を追加する必要がなく、回路面積の増大を防止することができる。

【0045】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0046】

10 前段バッファ

11 出力部

12 入力部

CB11 クロックバッファ

CB21、CB22 クロックバッファ

CB31、CB32 クロックバッファ

FF11〜FF14 フリップフロップ群

MN1、MN2 Nチャネルトランジスタ

MP1、MP2 Pチャネルトランジスタ

VCB11〜VCB14 可変クロックバッファ

【技術分野】

【0001】

本発明は半導体装置に関し、特に装置内の複数の論理回路にクロック信号を分配するクロック分配網を有する半導体装置に関する。

【背景技術】

【0002】

近年の半導体装置では、クロック信号に同期して信号を伝達する同期回路(例えば、フリップフロップ)が多く用いられている。このような半導体装置では、複数のフリップフロップにクロック信号が同時に入力されるように回路を構成する必要がある。しかしながら、クロック信号を複数のフリップフロップに分配する配線網には、寄生抵抗及び寄生容量が形成される。そのため、この寄生抵抗及び寄生容量に起因して、クロック信号がフリップフロップに到達するまでの時間に配線距離に応じた差が生じる。

【0003】

そこで、半導体装置の設計ではクロックツリー合成(Clock Tree Synthesis)処理により、クロックツリーを形成する。このクロックツリーには、クロック信号の伝達経路上に複数のCTSバッファが形成される。また、CTSバッファは、クロック信号を遅延させて次段に形成されるCTSバッファ又は回路に伝達する。つまり、CTSバッファは、フリップフロップ毎のクロックスキューを調節する。そして、クロックツリーを介してクロック信号を複数のフリップフロップに分配することで、複数のフリップフロップにクロック信号が同時に到達する。このようなCTS技術が特許文献1〜7に記載されている。

【0004】

しかし、クロックツリーを用いてクロック信号を複数のフリップフロップに分配した場合、同時に多数のフリップフロップ及びCTSバッファが動作する。そのため、論理回路で扱われる信号の論理レベルの切り替わりに応じて一度に多くの貫通電流が発生する。そして、この貫通電流が電源配線及び接地配線を流れた場合、当該電流がパッケージのインダクタンス及び寄生容量を介して流れ、電源ノイズが生じる。また、電源ノイズが回路の電気的特性に影響を及ぼす。そして、影響が大きくなると回路動作に不具合を生じることがある。

【0005】

そこで、このような回路素子の同時動作に起因して生じる貫通電流を抑制して電源ノイズを低減する技術が特許文献8に開示されている。特許文献8では、1チップでASIC(Application Specific Integrated Circuit)を構成する際に、ASIC内の回路を複数のブロックに分割する。そして、クロック信号の伝搬遅延時間をブロック毎に異なる値に設定する。これにより、特許文献8では、同時動作する回路素子の数を低減して、貫通電流のピーク値を低減する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−234226号公報

【特許文献2】特開2004−241699号公報

【特許文献3】特開2004−013979号公報

【特許文献4】特開2001−175699号公報

【特許文献5】特開2001−022816号公報

【特許文献6】特開2000−353745号公報

【特許文献7】特開2000−294737号公報

【特許文献8】特開2006−165099号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献8に記載の技術では、ブロック毎に回路の動作タイミングが異なるため、ブロック間で動作の整合整を保つことができない問題がある。

【課題を解決するための手段】

【0008】

本発明にかかる半導体装置の一態様は、動作クロック信号に応じて第1のクロック信号を出力し、第1の応答時間で前記第1のクロック信号のエッジを変化させる第1のクロックバッファと、前記動作クロック信号に応じて第2のクロック信号を出力し、前記第1の応答時間とは異なる第2の応答時間で前記第2のクロック信号のエッジを変化させる第2のクロックバッファと、前記第1のクロック信号に同期して動作し、第1の電圧レベルを前記第1のクロック信号の閾値電圧とする第1の論理回路と、前記第2のクロック信号に同期して動作し、前記第1の電圧レベルとは異なる第2の電圧レベルを前記第2のクロック信号の閾値電圧とする第2の論理回路と、を有し、前記第1、第2の論理回路は、前記動作クロック信号に応じて一のタイミングで動作する。

【0009】

本発明にかかる半導体装置の別の態様は、動作クロック信号を伝達し、出力部を構成するPチャネルトランジスタとNチャネルトランジスタの駆動能力の比が異なる複数の可変クロックバッファと、前記複数の可変クロックバッファのそれぞれに対応して設けられ、対応する前記可変バッファを介して前記動作クロック信号が入力されるフリップフロップと、を有し、前記フリップフロップの前記動作クロック信号の入力部は、対応する前記可変クロックバッファの駆動能力の比に応じてPチャネルトランジスタとNチャネルトランジスタとの駆動能力の比が決定される。

【0010】

本発明にかかる半導体装置の別の態様は、第1の応答時間を有する第1のCTSバッファと、前記第1のCTSバッファに結合され、前記第1のCTSバッファの出力信号のエッジに応答して一のタイミングで動作するように閾値電圧が設定された第1のフリップフロップと、前記第1の応答時間とは異なる第2の応答時間を有する第2のCTSバッファと、前記第2のCTSバッファに結合され、前記第2のCTSバッファの出力信号のエッジに応答して前記一のタイミングで動作するように閾値電圧が設定された第2のフリップフロップと、を有する。

【0011】

本発明にかかる半導体装置では、論理回路(又はフリップフロップ)に動作クロック信号を伝達するクロックバッファが、クロックバッファ毎に異なるタイミングで動作クロック信号のエッジを変化させる。これにより、クロックバッファ毎に消費電流のピークが生じるタイミングがずれて、消費電流のピーク値を抑制することができる。さらに、本発明にかかる半導体装置では、論理回路(又はフリップフロップ)における動作クロック信号に対する閾値が論理回路毎に異なる。そして、本発明にかかる半導体装置では、異なるタイミングでエッジが変化する動作クロック信号を受信して、一のタイミングで論理回路が動作する。

【発明の効果】

【0012】

本発明にかかる半導体装置は、消費電流のピーク値を抑制しながら論理回路を一のタイミングで動作させることができる。

【図面の簡単な説明】

【0013】

【図1】実施の形態1にかかる半導体装置のクロック分配網のブロック図である。

【図2】実施の形態1にかかる可変クロックバッファのブロック図である。

【図3】実施の形態1にかかる可変クロックバッファの駆動能力の違いを示す表である。

【図4】実施の形態1にかかるフリップフロップの動作クロック信号の入力部の回路図である。

【図5】実施の形態1にかかるフリップフロップの入力部の駆動能力の違いを示す表である。

【図6】実施の形態1にかかる可変クロックバッファとフリップフロップの動作を示すタイミングチャートである。

【図7】実施の形態1にかかる半導体装置の可変クロックバッファの消費電流を示すタイミングチャートである。

【発明を実施するための形態】

【0014】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。本発明は、半導体装置内に設けられるクロック分配網を構成するクロックバッファと、当該クロック分配網から動作クロック信号の供給を受ける論理回路(例えば、フリップフロップ)と、に特徴の一つを有する。そこで、以下では、半導体装置内のクロック分配網、クロックバッファ、及び、クロック分配網から動作クロック信号の供給を受ける論理回路部について特に詳細に説明を行う。つまり、本発明にかかる半導体装置は、以下で説明する動作クロック信号に基づき動作するフリップフロップ等と、以下では説明しない他の回路と、を含む。

【0015】

まず、図1に本発明にかかる半導体装置内に設けられるクロック分配網と当該クロック分配網から動作クロック信号を受ける論理回路部のブロック図を示す。図1に示すように、クロック分配網は、CTS部と、可変CTS部を有する。

【0016】

CTS部は複数のクロックバッファを有する。そして、CTS部では、このクロックバッファを介してツリー状のクロック分配網を構成する。図1に示す例では、クロックバッファCB11、CB21、CB22、CB31、CB32を示した。そして、図1に示す例では、クロックバッファCB11により動作クロック信号をクロックバッファCB21とクロックバッファCB22に分配する。また、クロックバッファCB21は、入力された動作クロック信号をクロックバッファCB31、CB32に分配する。そして、クロックバッファCB31は、可変CTS部に動作クロック信号を分配する。なお、クロックバッファCB22、CB32は、図示しないクロックバッファ又は論理回路に動作クロック信号を分配する。

【0017】

可変CTS部は、複数の可変クロックバッファを有する。図1に示す例では、クロックバッファCB31に対応して設けられる一群の可変クロックバッファのみを示した。図1に示す例では、一群の可変クロックバッファとして可変クロックバッファVCB11〜VCB14を示した。なお、一群の可変クロックバッファは、一の動作クロック信号に基づき、エッジの変化タイミングが異なる一群の動作クロック信号を出力する。

【0018】

論理回路部は、複数の論理回路を有する。この複数の論理回路のうち、クロック信号に同期して動作する論理回路を特に同期回路と称す。この同期回路は、例えば、フリップフロップである。そこで、図1に示す例では、複数のフリップフロップを論理回路部として示した。また、実施の形態1にかかる半導体装置では、複数のフリップフロップを、対応する可変クロックバッファVCB11〜VCB14に対応するフリップフロップ群FF11〜FF14を有する。

【0019】

フリップフロップ群FF11は、可変クロックバッファVCB11を介して動作クロック信号の供給を受ける。フリップフロップ群FF12は、可変クロックバッファVCB12を介して動作クロック信号の供給を受ける。フリップフロップ群FF13は、可変クロックバッファVCB13を介して動作クロック信号の供給を受ける。フリップフロップ群FF14は、可変クロックバッファVCB14を介して動作クロック信号の供給を受ける。

【0020】

ここで、実施の形態1にかかる半導体装置では、可変クロックバッファVCB11〜VCB14のうちの一つを第1の可変クロックバッファ、他の一つを第2の可変クロックバッファとした場合に、第1の可変クロックバッファは第1のクロック信号を出力し、第2の可変クロックバッファは第2のクロック信号を出力する。また、第1の可変クロックバッファは、第1の応答時間で第1のクロック信号のエッジを変化させ、第2の可変クロックバッファは、第2の応答時間で第2のクロック信号のエッジを変化させる。

【0021】

さらに、実施の形態1にかかる半導体装置では、フリップフロップ群FF11〜FF14のうち第1の可変クロックバッファから第1のクロック信号の供給を受けるフリップフロップ群に属するフリップフロップを第1のフリップフロップとし、第1の可変クロックバッファから第1のクロック信号の供給を受けるフリップフロップ群に属するフリップフロップを第1のフリップフロップとする。このとき、実施の形態1にかかる半導体装置では、この第1のフリップフロップは第1のクロック信号に対する閾値を第1の電圧レベルとし、第2のフリップフロップは第2のクロック信号に対する閾値を第2の電圧レベルとする。そして、第1のフリップフロップと第2のフリップフロップは、一のタイミングで動作する。

【0022】

以下では、可変クロックバッファ及びフリップフロップの詳細な構成について説明する。まず、可変クロックバッファの回路図を図2に示す。可変クロックバッファVCB11〜VCB14は、流出電流による駆動能力と流入電流による駆動能力との比が異なるが、基本的な回路構成は同じである。図2に示すように、可変クロックバッファは、前段バッファ10と出力部11とを有する。前段バッファ10は、例えば、インバータ回路であって、高入力インピーダンス・低出力インピーダンスの回路である。また、前段バッファ10は、1段のインバータにより構成しても良く、多段のインバータにより構成しても良い。なお、多段のインバータにより構成する場合は、後段になるほど駆動能力の高いインバータを配置することが好ましい。また、前段バッファ10は、入力閾値電圧として電源電圧の約半分の電圧レベルを有するものとする。さらに、前段バッファ10は、流出電流による駆動能力と流入電流による駆動能力との比が1:1であるものとする。

【0023】

出力部11は、高電位側電源端子(例えば、電源端子VDD)と低電位側電源端子(例えば、接地端子VSS)との間に直列に接続された第1導電型トランジスタ(例えば、PチャネルトランジスタMP1)と第2導電型トランジスタ(例えば、NチャネルトランジスタMN1)とを有する。そして、PチャネルトランジスタMP1とNチャネルトランジスタMN1は、インバータを構成する。そして、出力部11は、前段バッファ10が出力する信号を入力信号とし、当該入力信号の反転信号を出力する。以下の説明では、前段バッファ10に入力されるクロック信号にCIN0の符号を付し、前段バッファ10が出力する(又は出力部11に入力される)クロック信号にCIN1の符号を付し、出力部11が出力するクロック信号にCOUTの符号を付す。

【0024】

また、出力部11は、可変クロックバッファVCB11〜VCB14のそれぞれに設けられるが、可変クロックバッファ毎に流入電流による駆動能力と流出電流による駆動能力とが異なる。PチャネルトランジスタMP1のトランジスタサイズKと、NチャネルトランジスタMN1のトランジスタサイズLを可変クロックバッファ毎に変えることで駆動能力の違いを設定する。そこで、可変クロックバッファVCB11〜VCB14のトランジスタサイズの設定値を示す表を図3に示す。なお、図3に示す値は、各可変クロックバッファの出力部11を構成するPチャネルトランジスタMP1のトランジスタサイズKとNチャネルトランジスタMN1のトランジスタサイズLを示している。このとき、トランジスタサイズK(又はL)の値が1のトランジスタは、基準となる駆動能力を発揮するトランジスタである。そして、図3に示すトランジスタサイズK(又はL)の値は、各トランジスタが基準駆動能力の何倍の駆動能力を有するかを示す。

【0025】

図3に示すように、可変クロックバッファVCB11は、Pチャネルトランジスタの駆動能力が1、Nチャネルトランジスタの駆動能力が4である。可変クロックバッファVCB12は、Pチャネルトランジスタの駆動能力が2、Nチャネルトランジスタの駆動能力が3である。可変クロックバッファVCB13は、Pチャネルトランジスタの駆動能力が3、Nチャネルトランジスタの駆動能力が2である。可変クロックバッファVCB14は、Pチャネルトランジスタの駆動能力が4、Nチャネルトランジスタの駆動能力が1である。

【0026】

なお、基準駆動能力を発揮するトランジスタを設計し、駆動能力の倍数に応じて、トランジスタを並列して並べることでトランジスタの駆動能力を設定することができる。また、基準駆動能力を発揮するトランジスタを設計し、トランジスタのゲート幅を駆動能力の倍数に応じた倍数とすることでもトランジスタの駆動能力を設定することができる。

【0027】

図3に示す例では、出力するクロック信号の立ち上がりエッジの応答時間は、可変クロックバッファVCB11が最も長く、可変クロックバッファVCB14が最も短い。また、出力するクロック信号の立ち下がりエッジの応答時間は、可変クロックバッファVCB11が最も短く、可変クロックバッファVCB14が最も長い。つまり、可変クロックバッファは、PチャネルトランジスタMP1の駆動能力がNチャネルトランジスタMN1の駆動能力よりも大きいほど出力するクロック信号の立ち上がりエッジの応答時間が短くなる。また、可変クロックバッファは、NチャネルトランジスタMN1の駆動能力がPチャネルトランジスタMP1の駆動能力よりも大きいほど出力するクロック信号の立ち下がりエッジの応答時間が短くなる。

【0028】

続いて、フリップフロップの詳細について説明する。実施の形態1にかかる半導体装置のフリップフロップは、当該フリップフロップに動作クロック信号を供給する可変クロックバッファの駆動能力に応じてクロック信号に対する閾値電圧に違いを設けている。また、実施の形態1において説明するフリップフロップは、動作クロック信号に対する閾値電圧以外については一般的なフリップフロップと同じである。そこで、以下の説明では、フリップの動作クロック入力部についてのみ説明する。

【0029】

図4にフリップフロップの動作クロック信号CLKの入力部12の回路図を示す。入力部12は、高電位側電源端子(例えば、電源端子VDD)と低電位側電源端子(例えば、接地端子VSS)との間に直列に接続された第1導電型トランジスタ(例えば、PチャネルトランジスタMP2)と第2導電型トランジスタ(例えば、NチャネルトランジスタMN2)とを有する。そして、PチャネルトランジスタMP2とNチャネルトランジスタMN2は、インバータを構成する。そして入力部12は、入力される動作クロック信号CLKの反転信号CRTCを出力する。この反転信号CRTCは、図示しない、ラッチ回路に入力され、当該ラッチ回路に保持されている値の更新状態を制御する。

【0030】

また、入力部12は、フリップフロップ群FF11〜FF14に属するフリップフロップのそれぞれに設けられるが、フリップフロップ群毎に入力部12の動作クロック信号CLKに対する閾値電圧が異なる。PチャネルトランジスタMP2のトランジスタサイズMと、NチャネルトランジスタMN2のトランジスタサイズNをフリップフロップ群毎に変えることで閾値電圧の違いを設定する。そこで、フリップフロップ群FF11〜FF14の入力部12のトランジスタサイズの設定値を示す表を図5に示す。なお、図5に示す値は、フリップフロップ群FF11〜FF14の出力部11を構成するPチャネルトランジスタMP2のトランジスタサイズMとNチャネルトランジスタMN2のトランジスタサイズNを示している。このとき、トランジスタサイズM(又はN)の値が1のトランジスタは、基準となる駆動能力を発揮するトランジスタである。そして、図5に示すトランジスタサイズM(又はN)の値は、各トランジスタが基準駆動能力の何倍の駆動能力を有するかを示す。

【0031】

図5に示すように、フリップフロップ群FF11に属するフリップフロップの入力部12は、Pチャネルトランジスタの駆動能力が1、Nチャネルトランジスタの駆動能力が4である。フリップフロップ群FF11に属するフリップフロップの入力部12は、Pチャネルトランジスタの駆動能力が2、Nチャネルトランジスタの駆動能力が3である。フリップフロップ群FF11に属するフリップフロップの入力部12は、Pチャネルトランジスタの駆動能力が3、Nチャネルトランジスタの駆動能力が2である。フリップフロップ群FF11に属するフリップフロップの入力部12は、Pチャネルトランジスタの駆動能力が4、Nチャネルトランジスタの駆動能力が1である。

【0032】

なお、基準駆動能力を発揮するトランジスタを設計し、駆動能力の倍数に応じて、トランジスタを並列して並べることでトランジスタの駆動能力を設定することができる。また、基準駆動能力を発揮するトランジスタを設計し、トランジスタのゲート幅を駆動能力の倍数に応じた倍数とすることでもトランジスタの駆動能力を設定することができる。

【0033】

ここで、入力部12を構成するトランジスタのトランジスタサイズと入力部12の閾値電圧との関係について説明する。入力部12は、PチャネルトランジスタMP2とNチャネルトランジスタMN2によりインバータを構成する。そこで、インバータの閾値電圧とインバータを構成するトランジスタのトランジスタサイズとの関係を(1)式に示す。

【数1】

(1)式において、Vthはフリップフロップの動作クロック信号CLKの入力部12の閾値電圧であり、Vtnは入力部12を構成するNチャネルトランジスタMN2の閾値電圧であり、Vtpは入力部12を構成するPチャネルトランジスタMP2の閾値電圧であり、VDDは入力部12に与えられる電源電圧である。また、βNは(2)式、βPは(3)式により表される値である。

【数2】

【数3】

なお、(2)式のμnはNチャネルトランジスタMN2のキャリアの移動度であり、CoxはNチャネルトランジスタMN2のゲート容量であり、WnはNチャネルトランジスタMN2のゲート幅であり、LnはNチャネルトランジスタMN2のゲート長である。また、(3)式のμpはPチャネルトランジスタMP2のキャリアの移動度であり、CoxはPチャネルトランジスタMP2のゲート容量であり、WpはPチャネルトランジスタMP2のゲート幅であり、LpはPチャネルトランジスタMP2のゲート長である。

【0034】

上記(1)〜(3)式より、PチャネルトランジスタMP2及びNチャネルトランジスタMN2のゲート長を固定して、ゲート幅(又は並列トランジスタ数)を調節することでインバータの閾値電圧が変化することがわかる。より具体的には、PチャネルトランジスタMP2のゲート幅をNチャネルトランジスタMN2のゲート幅に比べて大きくすると、閾値電圧は電源電圧VDD側にずれる。一方、NチャネルトランジスタMN2のゲート幅をPチャネルトランジスタMP2のゲート幅に比べて大きくすると、閾値電圧は接地電圧VSS側にずれる。

【0035】

図1に示すように、実施の形態1にかかる半導体装置では、フリップフロップの入力部12のPチャネルトランジスタMP1の駆動能力とNチャネルトランジスタMN1の駆動能力との比をフリップフロップに動作クロックを供給する可変クロックバッファの出力部11の駆動能力の比に応じて決定する。つまり、流出側の駆動能力が高い可変クロックバッファには、流出側の駆動能力が高い入力部12を有するフリップフロップを対応させて設ける。また、流入側の駆動能力が高い可変クロックバッファには、流入側の駆動能力が高い入力部12を有するフリップフロップを対応させて設ける。

【0036】

より具体的には、PチャネルトランジスタMP1のトランジスタサイズKが1、NチャネルトランジスタMN1のトランジスタサイズLが4の可変クロックバッファVCB11には、PチャネルトランジスタMP2のトランジスタサイズMが1、NチャネルトランジスタMN2のトランジスタサイズNが4の入力部12を有するフリップフロップ群FF11に属するフリップフロップが設けられる。

【0037】

実施の形態1にかかる半導体装置では、このような対応関係に基づき可変クロックバッファVCB11〜VCB14とフリップフロップ群FF11〜FF14を設ける。これにより、閾値電圧が高い(電源電圧VDDに近い)フリップフロップには、立ち上がりエッジの応答時間が短い動作クロック信号CLKが入力され、閾値電圧が低い(接地電圧VSSに近い)フリップフロップには、立ち上がりエッジの応答時間が長い動作クロック信号CLKが入力される。

【0038】

ここで、実施の形態1にかかる半導体装置における可変クロックバッファVCB11〜VCB14とフリップフロップ群FF11〜FF14との動作を示すタイミングチャートを図6に示す。図6に示すように、可変クロックバッファに入力される動作クロック信号CIN0は、ほとんど遅延なく動作クロック信号CIN1として出力される。ここで、動作クロック信号CIN0、CIN1は、十分な駆動能力を有するバッファにより出力されるため、立ち上がりエッジと立ち下がりエッジは傾きが急峻になる。

【0039】

そして、動作クロック信号CIN1の立ち下がりエッジに応じて、可変クロックバッファは、動作クロック信号COUTを立ち上げる。この動作クロック信号COUTの立ち上がりエッジは、可変クロックバッファVCB11〜VCB14の電流流出駆動能力により異なる傾きとなる。より具体的には、電流流出駆動能力が高い可変クロックバッファVCB14が出力する動作クロック信号COUTの傾きが最も立ち上がりエッジの応答時間が短くなる。一方。可変クロックバッファVCB11は、電流流出駆動能力が最も低いため、可変クロックバッファVCB11が出力する動作クロック信号COUTの応答時間は最も長くなる。

【0040】

そして、可変クロックバッファVCB14が出力する応答時間が短い(立ち上がりエッジの傾きが急峻な)動作クロック信号COUTは、高い閾値電圧を有するフリップフロップ群FF14に属するフリップフロップに入力される。また、可変クロックバッファVCB11が出力する応答時間が長い(立ち上がりエッジの傾きが緩やかな)動作クロック信号COUTは、低い閾値電圧を有するフリップフロップ群FF11に属するフリップフロップに入力される。そして、動作クロック信号COUTのエッジの応答時間とフリップフロップの閾値電圧が上記のような関係を有することで、フリップフロップ群FF11〜FF14に属するフリップフロップに入力される動作クロック信号COUTの電圧レベルは、いずれも、タイミングT1フリップフロップ群FF11〜FF14の閾値電圧Vthを超える。つまり、フリップフロップ群FF11〜FF14に属するフリップフロップは、一のタイミング(図6に示すタイミングT1)で動作する。そして、すべてのフリップフロップ群に属するフリップフロップも一のタイミングで動作することで、属するフリップフロップ群に関わらず、フリップフロップ間での同期動作が可能になる。

【0041】

続いて、可変クロックバッファVCB11〜VCB14の消費電流について説明する。図7に可変クロックバッファVCB11〜VCB14の消費電流の変動を示すタイミングチャートを示す。図7に示すように、可変クロックバッファVCB11〜VCB14は、出力する動作クロック信号COUTの電圧レベルが傾きをもって遷移している期間において消費電流が増大する。そして、この消費電流は、動作クロック信号COUTの電圧レベルが電源電圧VDDの半分の電圧レベル(VDD/2)付近となるタイミングで最も多くなる。そのため、可変クロックバッファVCB11〜VCB14の消費電流Ivcb11〜Ivcb14のピークが生じるタイミングはずれる。そして、この消費電流Ivcb11〜Ivcb14の合計値であるItotalは、可変クロックバッファを用いない場合よりもピーク値が小さくなる。

【0042】

上記説明より、実施の形態1にかかる半導体装置では、可変クロックバッファと、当該可変クロックバッファの駆動能力に応じた閾値電圧を有するフリップフロップと、を有する。これにより、実施の形態1にかかる半導体装置では、可変クロックバッファの動作に起因する消費電流のピーク値を抑制することができる。さらに、実施の形態1にかかる半導体装置では、入力される動作クロック信号の応答時間に応じてフリップフロップの閾値電圧を設定する。これにより、動作クロック信号の応答時間をずらしながら、入力される動作クロック信号の応答時間によらず複数のフリップフロップを一のタイミングで動作させることができる。また、入力される動作クロック信号によらず複数のフリップフロップを一のタイミングで動作させることで、入力される動作クロック信号によらずフリップフロップ間の同期動作を実現することができる。

【0043】

さらに、実施の形態1にかかる半導体装置における可変クロックバッファは、出力部11を構成する2つのトランジスタの駆動能力の比を変えることで消費電流のピークが発生するタイミングをずらすものである。つまり、実施の形態1にかかる半導体装置では、消費電流のピーク発生タイミングをずらすために別途回路を追加する必要がなく、回路面積の増大を防止することができる。

【0044】

さらに、実施の形態1にかかる半導体装置では、可変クロックバッファの出力部11の駆動能力の比と、フリップフロップの入力部12の駆動能力の比と、を対応する比とすることでフリップフロップ間の動作タイミングを一致させる。つまり、動作クロック信号のずれに応じて、フリップフロップの動作タイミングをずらすために、別途回路を追加する必要がなく、回路面積の増大を防止することができる。

【0045】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0046】

10 前段バッファ

11 出力部

12 入力部

CB11 クロックバッファ

CB21、CB22 クロックバッファ

CB31、CB32 クロックバッファ

FF11〜FF14 フリップフロップ群

MN1、MN2 Nチャネルトランジスタ

MP1、MP2 Pチャネルトランジスタ

VCB11〜VCB14 可変クロックバッファ

【特許請求の範囲】

【請求項1】

動作クロック信号に応じて第1のクロック信号を出力し、第1の応答時間で前記第1のクロック信号のエッジを変化させる第1のクロックバッファと、

前記動作クロック信号に応じて第2のクロック信号を出力し、前記第1の応答時間とは異なる第2の応答時間で前記第2のクロック信号のエッジを変化させる第2のクロックバッファと、

前記第1のクロック信号に同期して動作し、第1の電圧レベルを前記第1のクロック信号の閾値電圧とする第1の論理回路と、

前記第2のクロック信号に同期して動作し、前記第1の電圧レベルとは異なる第2の電圧レベルを前記第2のクロック信号の閾値電圧とする第2の論理回路と、を有し、

前記第1、第2の論理回路は、前記動作クロック信号に応じて一のタイミングで動作する半導体装置。

【請求項2】

前記第1のクロックバッファの出力部及び前記第1の論理回路のクロック信号の入力部は、それぞれ高電位側電源端子と低電位側電源端子との間に直列に接続された第1導電型トランジスタと第2導電型トランジスタとを有し、前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比が同じ値に設定され、

前記第2のクロックバッファの出力部及び前記第2の論理回路のクロック信号の入力部は、それぞれ高電位側電源端子と低電位側電源端子との間に直列に接続された第1導電型トランジスタと第2導電型トランジスタとを有し、前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比が同じ値に設定され、

前記第1のクロックバッファと前記第2のクロックバッファとは、前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比が互いに異なる値に設定される請求項1に記載の半導体装置。

【請求項3】

前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比は、前記第1の導電型トランジスタのゲート幅と前記第2の導電型トランジスタのゲート幅との比により設定される請求項2に記載の半導体装置。

【請求項4】

前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比は、トランジスタの所定のゲート幅を1単位とした場合に、前記第1の導電型トランジスタを構成するトランジスタの単位数と前記第2の導電型トランジスタを構成するトランジスタの単位数との比により設定される請求項2に記載の半導体装置。

【請求項5】

前記第1の論理回路の閾値電圧は、前記第1の論理回路の入力部を構成する前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比に応じて設定され、

前記第2の論理回路の閾値電圧は、前記第2の論理回路の入力部を構成する前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比に応じて設定される請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

前記第1、第2のクロックバッファは、前記動作クロック信号を複数の論理回路に分配するクロック分配網の末端に配置される請求項1乃至5のいずれか1項に記載の半導体装置。

【請求項7】

前記第1、第2のクロックバッファは、出力部の前段に少なくとも一つのインバータ回路を有し、前記インバータ回路は、前記出力部よりも駆動能力が高い請求項1乃至6のいずれか1項に記載の半導体装置。

【請求項8】

動作クロック信号を伝達し、出力部を構成するPチャネルトランジスタとNチャネルトランジスタの駆動能力の比が異なる複数の可変クロックバッファと、

前記複数の可変クロックバッファのそれぞれに対応して設けられ、対応する前記可変バッファを介して前記動作クロック信号が入力されるフリップフロップと、を有し、

前記フリップフロップの前記動作クロック信号の入力部は、対応する前記可変クロックバッファの駆動能力の比に応じてPチャネルトランジスタとNチャネルトランジスタとの駆動能力の比が決定される半導体装置。

【請求項9】

前記Pチャネルトランジスタの駆動能力と前記Nチャネルトランジスタの駆動能力との比は、前記Pチャネルトランジスタのゲート幅と前記Nチャネルトランジスタのゲート幅との比により設定される請求項8に記載の半導体装置。

【請求項10】

前記Pチャネルトランジスタの駆動能力と前記Nチャネルトランジスタの駆動能力との比は、トランジスタの所定のゲート幅を1単位とした場合に、前記Pチャネルトランジスタを構成するトランジスタの単位数と前記Nチャネルトランジスタを構成するトランジスタの単位数との比により設定される請求項8に記載の半導体装置。

【請求項11】

前記複数の可変クロックバッファは、前記動作クロック信号を複数のフリップフロップに分配するクロック分配網の末端に配置される請求項8乃至10のいずれか1項に記載の半導体装置。

【請求項12】

前記複数の可変クロックバッファは、出力部の前段に少なくとも一つのインバータ回路を有し、前記インバータ回路は、前記出力部よりも駆動能力が高い請求項8乃至11のいずれか1項に記載の半導体装置。

【請求項13】

前記フリップフロップは、一のタイミングで複数個が動作する請求項8乃至12のいずれか1項に記載の半導体装置。

【請求項14】

第1の応答時間を有する第1のCTSバッファと、

前記第1のCTSバッファに結合され、前記第1のCTSバッファの出力信号のエッジに応答して一のタイミングで動作するように閾値電圧が設定された第1のフリップフロップと、

前記第1の応答時間とは異なる第2の応答時間を有する第2のCTSバッファと、

前記第2のCTSバッファに結合され、前記第2のCTSバッファの出力信号のエッジに応答して前記一のタイミングで動作するように閾値電圧が設定された第2のフリップフロップと、

を有する半導体装置。

【請求項1】

動作クロック信号に応じて第1のクロック信号を出力し、第1の応答時間で前記第1のクロック信号のエッジを変化させる第1のクロックバッファと、

前記動作クロック信号に応じて第2のクロック信号を出力し、前記第1の応答時間とは異なる第2の応答時間で前記第2のクロック信号のエッジを変化させる第2のクロックバッファと、

前記第1のクロック信号に同期して動作し、第1の電圧レベルを前記第1のクロック信号の閾値電圧とする第1の論理回路と、

前記第2のクロック信号に同期して動作し、前記第1の電圧レベルとは異なる第2の電圧レベルを前記第2のクロック信号の閾値電圧とする第2の論理回路と、を有し、

前記第1、第2の論理回路は、前記動作クロック信号に応じて一のタイミングで動作する半導体装置。

【請求項2】

前記第1のクロックバッファの出力部及び前記第1の論理回路のクロック信号の入力部は、それぞれ高電位側電源端子と低電位側電源端子との間に直列に接続された第1導電型トランジスタと第2導電型トランジスタとを有し、前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比が同じ値に設定され、

前記第2のクロックバッファの出力部及び前記第2の論理回路のクロック信号の入力部は、それぞれ高電位側電源端子と低電位側電源端子との間に直列に接続された第1導電型トランジスタと第2導電型トランジスタとを有し、前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比が同じ値に設定され、

前記第1のクロックバッファと前記第2のクロックバッファとは、前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比が互いに異なる値に設定される請求項1に記載の半導体装置。

【請求項3】

前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比は、前記第1の導電型トランジスタのゲート幅と前記第2の導電型トランジスタのゲート幅との比により設定される請求項2に記載の半導体装置。

【請求項4】

前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比は、トランジスタの所定のゲート幅を1単位とした場合に、前記第1の導電型トランジスタを構成するトランジスタの単位数と前記第2の導電型トランジスタを構成するトランジスタの単位数との比により設定される請求項2に記載の半導体装置。

【請求項5】

前記第1の論理回路の閾値電圧は、前記第1の論理回路の入力部を構成する前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比に応じて設定され、

前記第2の論理回路の閾値電圧は、前記第2の論理回路の入力部を構成する前記第1の導電型トランジスタの駆動能力と前記第2の導電型トランジスタの駆動能力との比に応じて設定される請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

前記第1、第2のクロックバッファは、前記動作クロック信号を複数の論理回路に分配するクロック分配網の末端に配置される請求項1乃至5のいずれか1項に記載の半導体装置。

【請求項7】

前記第1、第2のクロックバッファは、出力部の前段に少なくとも一つのインバータ回路を有し、前記インバータ回路は、前記出力部よりも駆動能力が高い請求項1乃至6のいずれか1項に記載の半導体装置。

【請求項8】

動作クロック信号を伝達し、出力部を構成するPチャネルトランジスタとNチャネルトランジスタの駆動能力の比が異なる複数の可変クロックバッファと、

前記複数の可変クロックバッファのそれぞれに対応して設けられ、対応する前記可変バッファを介して前記動作クロック信号が入力されるフリップフロップと、を有し、

前記フリップフロップの前記動作クロック信号の入力部は、対応する前記可変クロックバッファの駆動能力の比に応じてPチャネルトランジスタとNチャネルトランジスタとの駆動能力の比が決定される半導体装置。

【請求項9】

前記Pチャネルトランジスタの駆動能力と前記Nチャネルトランジスタの駆動能力との比は、前記Pチャネルトランジスタのゲート幅と前記Nチャネルトランジスタのゲート幅との比により設定される請求項8に記載の半導体装置。

【請求項10】

前記Pチャネルトランジスタの駆動能力と前記Nチャネルトランジスタの駆動能力との比は、トランジスタの所定のゲート幅を1単位とした場合に、前記Pチャネルトランジスタを構成するトランジスタの単位数と前記Nチャネルトランジスタを構成するトランジスタの単位数との比により設定される請求項8に記載の半導体装置。

【請求項11】

前記複数の可変クロックバッファは、前記動作クロック信号を複数のフリップフロップに分配するクロック分配網の末端に配置される請求項8乃至10のいずれか1項に記載の半導体装置。

【請求項12】

前記複数の可変クロックバッファは、出力部の前段に少なくとも一つのインバータ回路を有し、前記インバータ回路は、前記出力部よりも駆動能力が高い請求項8乃至11のいずれか1項に記載の半導体装置。

【請求項13】

前記フリップフロップは、一のタイミングで複数個が動作する請求項8乃至12のいずれか1項に記載の半導体装置。

【請求項14】

第1の応答時間を有する第1のCTSバッファと、

前記第1のCTSバッファに結合され、前記第1のCTSバッファの出力信号のエッジに応答して一のタイミングで動作するように閾値電圧が設定された第1のフリップフロップと、

前記第1の応答時間とは異なる第2の応答時間を有する第2のCTSバッファと、

前記第2のCTSバッファに結合され、前記第2のCTSバッファの出力信号のエッジに応答して前記一のタイミングで動作するように閾値電圧が設定された第2のフリップフロップと、

を有する半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−175173(P2012−175173A)

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願番号】特願2011−32343(P2011−32343)

【出願日】平成23年2月17日(2011.2.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願日】平成23年2月17日(2011.2.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]