Fターム[5J056HH00]の内容

論理回路 (30,215) | 基板構造、製造時の特徴 (247)

Fターム[5J056HH00]の下位に属するFターム

チャネル(ゲート)幅 (58)

チャネル(ゲート)長 (51)

配線の位置、幅、長さ (73)

マスタースライス、PLA (19)

Fターム[5J056HH00]に分類される特許

1 - 20 / 46

レベルシフター回路、集積回路装置、電子時計

【課題】 出力信号にスパイクノイズが乗ることや、応答速度が遅くなることを防止するレベルシフター回路を提供する。

【解決手段】 第1の高電位と第1の低電位とを電源電位とする第1の電位系の入力信号Aを受け取り、第1の電位系の信号である第1の信号XAを出力する第1の回路10と、第2の高電位と第2の低電位とを電源電位とする第2の電位系の、入力信号に応じた出力信号Yを生成する第2の回路20と、入力信号を受け取り、第1の電位系の信号であって入力信号と論理的に等価な第2の信号Bを生成するバッファー回路と、を含み、第2の回路は、第2の信号を受け取り、第3の信号XDを出力する初段インバーターと、第1の信号に基づいて、初段インバーターと第2の高電位を供給する電源又は第2の低電位を供給する電源との接続、切断を切り換える初段スイッチと、を含み、第3の信号に基づいて出力信号を生成する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

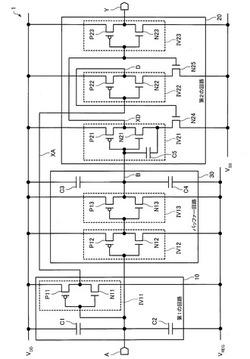

半導体集積回路装置

【課題】低コストで低電圧高速動作が可能なI/O回路を備えた半導体集積回路装置を提供する。

【解決手段】I/O回路において、I/O電圧vcc(例えば3.3V)をvcc_18(例えば1.8V)へ低電圧化した場合に、速度劣化を引き起こす部分が、レベル変換部と、メインの大型バッファを駆動するためのプリバッファ部分であることに着目し、レベルアップコンバータLUCとプリバッファPBFの回路に高電圧(電圧vcc)を印加することにより、低コストで低電圧高速動作が可能なI/O回路を実現する。

(もっと読む)

非同期回路検証装置及びプログラム

【課題】回路規模が大きくても、高い検証精度で、回路動作が正常であるかどうかを検証することができるようにする。

【解決手段】回路分割部30によって、検証対象の非同期回路を分割した複数のブロック回路に分割する。第1形式検証部32によって、ブロック回路データに対して、回路動作の形式検証を行う。モデル生成部34によって、回路動作が正常であることが検証された複数のブロック回路データの各々について、入力端に接続されている2段分のフリップフロップと、出力端に接続されている1段分のフリップフロップと、残りの回路部分を表わす不明回路部とを用いて記述された検証用モデルを生成する。第2形式検証部36によって、検証用モデルを組み合わせた、検証対象の非同期回路を表わす非同期検証用モデルに対して、回路動作の形式検証を行う。

(もっと読む)

半導体集積回路

【課題】トランジスタの特性ばらつきによる遅延回路の遅延時間の変動を抑制することが可能で、更に、製造工程における加工ばらつきに強く、レイアウト拡張性に優れた半導体集積回路を小面積に提供する。

【解決手段】第1の電源VDDと第2の電源(接地電源)との間に直列に接続されたP型MOSトランジスタMP11と2以上のN型MOSトランジスタMN11、MN12とが備えられる。入力端子INは前記P型MOSトランジスタMP11のゲート端子と前記N型MOSトランジスタMN11、MN12のゲート端子とに接続される。更に、P型MOSトランジスタMP11とN型MOSトランジスタMN11の接点である出力端子OUTに接続した1以上の容量素子C1を有し、P型MOSトランジスタMP11の駆動能力を、2以上に直列接続したN型MOSトランジスタMN11、MN12の総駆動能力よりも大きく構成する。

(もっと読む)

半導体装置、及び動作モ−ド切換方法

【課題】動作モード切換用パッドの配置自由度を向上させる。

【解決手段】パッドに新規に設けたプルアップ回路、及びプルダウン回路のスイッチを排他的に(交互に)切り換えられるようにして、プルアップ回路接続時のパッド電位と、プルダウン回路接続時のパッド電位とのEOR演算を行う。それぞれの電位は時系列で測定されるため、先に測定された電位は一時的な記憶回路に格納しておき、次に測定された電位とEOR演算を行う。以上の演算処理により、パッケージピンとパッドが接続されている端子は「0」、OPENの端子は「1」の情報を得ることができるため、これらの情報を基に動作モードを切り換える。

(もっと読む)

半導体装置

【課題】設計時の配置、又はプロセスばらつきによってパイプライン処理を行う各ステージ毎に処理速度が異なる。そこで、本発明の目的は、各段の処理機構が独立して動作でき、それらが同じ一定の時間内で処理が終了できるプロセッサの設計および製造を行うできる装置を提供することである。

【解決手段】複数段のステージ分割されたパイプライン処理を行う演算器において、各段が独立に動作することが求められている各段及びステージ毎に、独立に各段及びステージを構成しているMOSトランジスタのしきい値電圧を製造後において変化させる。

(もっと読む)

半導体集積回路装置

【課題】チップへの回路セルの実装率を保ちつつ、微細化の進んだ半導体素子および配線の均等性を保つことのできる技術を提供する。

【解決手段】NAND回路セルを形成するnチャネル型MISFETQn2およびnチャネル型MISFETQn3のそれぞれのゲート電極4を同一ノードとし、同じ入力信号に従って同時にオン・オフ動作を行う構成とする。nチャネル型MISFETQn2およびnチャネル型MISFETQn3は隣接して配置し、電気的には直列に接続された構造とする。また、NAND回路セルを形成pチャネル型MISFETQp3およびpチャネル型MISFETQp4のそれぞれのゲート電極4を同一ノードとし、同じ入力信号に従って同時にオン・オフ動作を行う構成とする。pチャネル型MISFETQp3およびpチャネル型MISFETQp4は隣接して配置し、電気的には直列に接続された構造とする。

(もっと読む)

半導体装置

【課題】論理回路部におけるリーク電流の低減を可能とする半導体装置を提供する。

【解決手段】半導体装置は、 第1の高電位(Vper1)を供給する第1の電源線(31)と、第2の高電位(Vper2)を供給する第2の電源線(32)と、第1の低電位(Vss1)を供給する第1の接地線(41)と、第2の低電位(Vss2)を供給する第2の接地線(42)と、第1の高電位を生成し、第1の電源線に供給する第1の内部電源発生回路(VDC1)と、第2の高電位を生成し、第2の電源線(32)に供給する第2の内部電源発生回路(VDC2)と、第1の電源線及び第1の接地線に接続された第1の論理回路(11)と、第2の電源線及び第2の接地線に接続された第2の論理回路(13)とを備える。所定数の第1の論理回路と第2の論理回路が交互に直列に接続される。

(もっと読む)

信号伝搬回路および信号処理装置

【課題】電気信号の検出を高感度にする。

【解決手段】基板11cをそなえるとともに、基板11cに、出力端に接続される終端抵抗とインピーダンスが実質的に整合し、入力端からの信号を伝搬する信号伝搬路11aと、信号伝搬路11aの途中箇所において信号伝搬路11aに非接触に形成された線路11b−1,11b−2と、をそなえる。

(もっと読む)

不揮発性記憶ゲートおよびその動作方法、および不揮発性記憶ゲート組込み型論理回路およびその動作方法

【課題】電源遮断後もデータを保持可能な不揮発性記憶ゲートを組み込み、待機状態に入ると同時に電源を遮断できる不揮発性記憶ゲートを組込み型論理回路を提供する。

【解決手段】論理ゲート16を有する論理演算部14と、不揮発性記憶部18,不揮発性記憶部に隣接して配置され,不揮発性記憶部へのデータ書込みおよび不揮発性記憶部からのデータ読出しのための制御信号を受信するデータインタフェース制御部22,データインタフェース制御部に隣接して配置され,データ入力信号Dおよびクロック信号CLKを受信し,データ出力信号Qを出力する揮発性記憶部24を有する不揮発性記憶ゲート12とを備える。

(もっと読む)

半導体設計方法、装置、およびプログラム

【課題】電源遮断からの復帰時間が短く、かつ回路規模が抑制されたパワードメインを設計する。

【解決手段】回路挿入位置抽出部13は、パワードメインの出力側境界からN段目のFFと(N−1)段目のFFとの間の信号経路において、出力の分岐点をノードとして定義し、この定義に基づくノードモデルにおいて、N段目の各FFから(N−1)段目の各FFまでのすべての信号経路上のノードの数が同じになるようにノードを追加して、ノードモデルを更新する。そして、更新したノードモデルにおいて、N段目または(N−1)段目の各FFから見て同じノード段数となる位置に配置されたノードをカウントし、ノードの数が最も少ないノード段数に対応するノードの出力側を、電源遮断時にその直前の入力信号値を保持する機能を備えたデータラッチ回路を挿入する位置として抽出する。

(もっと読む)

半導体装置

【課題】プロセス工程及び開発期間を減らし、サイズを小さくすることができる静電気放電保護回路を有する半導体装置を提供することを課題とする。

【解決手段】入出力パッド(101)と、電源電圧が供給される電源電圧ノード(VDE)と、基準電位が供給される基準電位ノード(GND)と、アノードが前記入出力パッドに接続され、カソードが第1のノードに接続される第1のダイオード(131)と、前記入出力パッド及び前記電源電圧ノードに接続され、前記入出力パッドに前記電源電圧より低い電圧が入力されると、前記第1のノードが前記電源電圧になるように制御する電位制御回路(103)と、前記入出力パッドに静電気が入力されると静電気オン信号を出力するトリガ回路(109)と、前記静電気オン信号が出力されると、前記第1のノード及び前記基準電位ノード間に静電気放電電流を流す静電気放電サージパス回路(108)とを有する。

(もっと読む)

集積回路装置、電気光学装置および電子機器

【課題】 簡単な制御で、該当するリピータのバッファリングを禁止し、リピータの内部構成も簡素化すること。

【解決手段】 複数の回路ブロックに共通に使用される信号伝送路L4と、転送対象の信号をバッファリングするバッファ回路(CBF1等)を有するリピータ(Rep(1)等)を有し、リピータは転送禁止回路(CNT1等)を含み、転送対象の信号は、バッファ回路(CBF1等)および回路ブロック(ブロック(1)等)の双方に並行的に入力され、イネーブル信号に基づいて複数の回路ブロックのうちの少なくとも一つが選択的にイネーブルにされる場合、イネーブルにされる少なくとも一つの回路ブロックに対応した少なくとも一つのリピータに含まれる転送禁止回路(CNT1等)は、イネーブル信号に基づいて、少なくとも一つのリピータに含まれるバッファ回路のバッファリングを禁止する。

(もっと読む)

半導体集積回路、および、その起動方法

【課題】起動直後に電源スイッチトランジスタをオフ状態にとどめることにより無駄な電力消費を防止する。

【解決手段】回路部(回路ブロックB(BLK_B)等)と、電源スイッチトランジスタSW1,SW2と、制御部(オフスタート・スイッチ制御部2)とを有する。オフスタート・スイッチ制御部2は、外部から入力されるオフスタートモードの設定信号(OSM_SET)が起動時に活性(“1”)のときは、電源スイッチトランジスタSW1,SW2の導通禁止状態(クリア信号(CL):“0”)で起動動作を開始する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置におけるクロック信号の遅延補正方法

【課題】他の外部装置に転送する非クロック信号の確定遅延の増加を抑えることができる半導体集積回路装置を提供する。

【解決手段】遅延補正回路80は、所定の内部回路から内部バスを介して与えられる外部に出力すべきクロック信号SDCKおよびデータ信号DO0〜DO3を入力し、遅延補正制御回路81に制御されて信号入出力部3におけるSSOノイズによるデータ信号DO0〜DO3の確定遅延の増加を抑えるようにクロック信号SDCKの遅延補正を行い、この遅延補正を行ったクロック信号SDCKと、所定時間遅延させたデータ信号DO0〜DO3とを出力する。

(もっと読む)

半導体装置、半導体装置の設計方法および半導体装置設計プログラム

【課題】レイアウト構成にかかわらず漏れ電流を防止することができる。

【解決手段】半導体装置1は、階層構造のモジュールを備えている。具体的には、基板2上に載置された第1のモジュール3と、第1のモジュール3と階層関係にある第2のモジュール4と、第1のモジュール3に駆動電圧VDD1を供給する第1のパワーゲーティングセル5と、第1のパワーゲーティングセル5を介さずに第2のモジュール4に駆動電圧VDD2を供給する第2のパワーゲーティングセル6と、第1のパワーゲーティングセル5の制御信号#1の切断(OFF)に基づいて、第2のパワーゲーティングセル6の制御信号を切断する電源切断検出回路7とを有している。第1のパワーゲーティングセル5および第2のパワーゲーティングセル6とには、それぞれ電源電圧VDDが供給されている。

(もっと読む)

マスタスレーブ型フリップフロップ回路

【課題】ゲートアレイを用いて実現する場合に、消費電力およびEMIの低減化を図るとともに、配線リソースを確保して配線の容易化を図ること。

【解決手段】マスタラッチ1は、クロックドインバータ11と、ラッチ回路12とからなる。スレーブラッチ1は、伝送ゲート21と、ラッチ回路22とを含んでいる。このようなフリップフロップ1、2を構成する各要素は、ゲートアレイを構成する基本セルを用いて構成した。そのゲートアレイの基本セルは、N型の3連のMOSトランジスタと、これに対応するP型の3連のMOSトランジスタとからなる。N型の3連のMOSトランジスタは、2連の通常サイズの主トランジスタと、通常サイズよりも小さなサイズの1つの補助トランジスタとからなる。N型の3連のMOSトランジスタも同様に構成する。

(もっと読む)

半導体装置および記憶媒体

【課題】論理回路を構成するコアセルを備えた半導体装置の電源ノイズを低減する。

【解決手段】半導体基板の主面に設けられた論理回路を構成するコアセルCLの上方に、コアセルCLに対する電源Vdd用の電源幹線PM1と電気的に接続された支線BL1、および、コアセルCLに対する電源Vss用の電源幹線PM2と電気的に接続された支線BL2を設ける。支線BL1と支線BL2とが対向して、電源Vddと電源Vssとの間に容量C1を構成する。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

1 - 20 / 46

[ Back to top ]