Fターム[5J056AA39]の内容

論理回路 (30,215) | 回路の種類 (3,583) | インターフェース、レベルシフト、レベル変換 (1,016) | タイミングの調整、遅延、同期 (148)

Fターム[5J056AA39]に分類される特許

1 - 20 / 148

省面積及び省電力のスタンダードセル方法

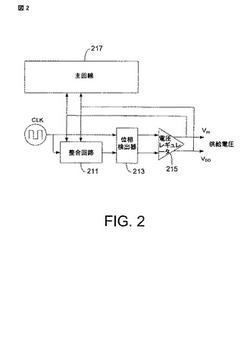

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

ディジタル信号処理回路及び車載用電子機器

【課題】ディジタル信号処理回路及び車載用電子機器において、消費電力を低減し、発熱量を低減する。

【解決手段】車載用電子機器に搭載されるディジタル信号処理回路は、クロック信号に同期して信号取込を行う入力段のフリップフロップ回路と、クロック信号に同期して信号取込を行う出力段のフリップフロップ回路と、順次処理を行う複数の組み合わせ回路が直列に接続されて構成されるとともに、クロック信号に同期して入力段のフリップフロップ回路から処理対象の信号が入力されて前記出力段のフリップフロップ回路に処理後の信号を出力する組み合わせ回路群と、クロック信号に同期して、組み合わせ回路毎に、クロック信号の1周期内において、駆動用電源の供給期間及び非供給期間を設けて駆動用電源の供給を行う電源供給回路と、を備える。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

半導体集積回路

【課題】記憶装置の消費電力を低減すること、記憶装置の面積を低減すること、記憶装置を構成するトランジスタの数を低減する。

【解決手段】第1の出力信号及び第2の出力信号の電位を比較する比較器と、第1の酸化物半導体トランジスタ及び第1のシリコントランジスタを有する第1のメモリ部と、第2の酸化物半導体トランジスタ及び第2のシリコントランジスタを有する第2のメモリ部と、当該第1の出力信号及び当該第2の出力信号の電位を確定する出力電位確定器とを有し、当該第1の酸化物半導体トランジスタのソース又はドレインの一方は、当該第1のシリコントランジスタのゲートに電気的に接続されており、当該第2の酸化物半導体トランジスタのソース又はドレインの一方は、当該第2のシリコントランジスタのゲートに電気的に接続されている記憶装置に関する。

(もっと読む)

回路装置及び電子機器

【課題】断熱的回路動作により消費電力を抑制することができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、第1の基準電圧を基準として電圧が周期的に変化する第1の電源電圧VP、及び第2の基準電圧を基準として電圧が周期的に変化する第2の電源電圧VMが供給されて断熱的回路動作を行う断熱的回路100と、第1の直流電源電圧VDD及び第2の直流電源電圧VSSが供給されて動作する非断熱的回路120と、断熱的回路100と非断熱的回路120との間に設けられるラッチ回路210とを含む。ラッチ回路210は、断熱的回路100からの出力信号D2を、第1の電源電圧VPが極大となり第2の電源電圧VMが極小となるタイミングに対して設定された第1のラッチ期間においてラッチし、出力信号D2のラッチ信号Q2を非断熱的回路120に対して出力する。

(もっと読む)

半導体装置

【課題】 本実施形態は、出力ドライバのドライブ能力のキャリブレーション精度を向上することが可能な半導体装置を提供する。

【解決手段】 第1、第2のプルアップドライバユニットPUDUa、PUDUbは、プルアップドライバを調整する。プルダウンドライバユニットPDDUbは、プルダウンドライバを調整する。キャリブレーション回路CBCは、プルアップドライバのキャリブレーション時、基準電圧VREFと、基準抵抗RZQに基づく第1のプルアップドライバの出力電圧を比較して第1、第2のプルアップドライバユニットのドライブ能力を決定し、プルダウンドライバのキャリブレーション時、基準電圧と、第2のプルアップドライバとプルダウンドライバの接続ノードの電圧を比較してプルダウンドライバのドライブ能力を決定する単一の比較器COMPを有している。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

集積回路及び集積回路の制御方法

【課題】回路若しくは装置が、仕様或いは規格に適用しない部分があったとしても、使用することに問題がない場合の対応方法のひとつを提供する。

【解決手段】集積回路が入出力回路とタイミング測定回路とを含み、前記入出力回路の第1の入力端子に入力される第1の信号と、前記入出力回路の第1の出力端子から出力される第2の信号とが前記タイミング測定回路に入力され、前記第2の信号は、前記入出力回路の第1の入出力端子における信号が前記第1の出力端子から出力されたものであり、前記タイミング測定回路において、前記第1の信号における第1の変化を検出し、前記第2の信号における前記第1の変化に対応する第2の変化を検出し、前記第1の変化を検出したときと前記第2の変化を検出したときとの間の時間間隔の計測を行うことを特徴とする。

(もっと読む)

回路装置及び回路装置の制御方法

【課題】プルアップ電流を増加することなく、オープンドレイン接続の信号ラインのスルーレートを向上させる。

【解決手段】オープンドレイン若しくはオープンコレクターの出力端子を駆動する出力回路と、前記出力回路を制御する制御回路と、を含み、前記制御回路は、前記出力回路が前記出力端子にローレベルを出力しない期間において、前記出力端子がローレベルからハイレベルに遷移する場合に前記出力回路が前記出力端子にハイレベルを出力する制御を行うことを特徴とする。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、クロックツリーにおける消費電流を削減しながら、同期回路間の同期動作を行うことが難しかった。

【解決手段】本発明にかかる半導体装置は、動作クロック信号CLKに応じて第1のクロック信号を出力し、第1の応答時間で第1のクロック信号のエッジを変化させる第1のクロックバッファ(VCB11〜VCB14のうちの一つ)と、動作クロック信号CLKに応じて第2のクロック信号を出力し、第2の応答時間で第2のクロック信号のエッジを変化させる第2のクロックバッファ(VCB11〜VCB14のうちの他の一つ)と、第1のクロック信号に同期して動作し、第1の電圧レベルを閾値電圧とする第1の論理回路と、第2のクロック信号に同期して動作し、第2の電圧レベルを閾値電圧とする第2の論理回路と、を有し、第1、第2の論理回路は、動作クロック信号に応じて一のタイミングで動作する。

(もっと読む)

タイミング制御回路、タイミング制御方法、及びシステム

【課題】タイミングマージンの減少を抑制すること。

【解決手段】システム装置21に形成された制御回路36は、可変容量35の容量値を制御し、トレーニング回路45にタイミングトレーニングを実行させる。トレーニング回路45は、メモリ12がデータDQに基づく正常なデータを書き込むことができる設定値の最大値と最小値を出力する。制御回路36は、その最大値及び最小値に基づいてデータDQのウインドウ幅を算出し、より大きなウインドウ幅に対応する容量値を可変容量35に設定する。

(もっと読む)

クロックバッファ回路及びこれを用いたクロック分配回路

【課題】小さな回路規模により広帯域のクロック信号に対応できるクロックバッファ回路を提供すること。

【解決手段】本発明の一態様であるクロックバッファ回路100は、ドライバ部11及びLCタンク部21を有する。ドライバ部11は、クロック入力IN及びINBからの入力クロック信号の少なくとも正転出力を、それぞれクロック出力OUT及びOUTBへ出力する。LCタンク部は、ドライバ部11とクロック出力OUT及びOUTBとの間に配置される。ドライバ部11は、入力クロック信号の周波数に対応した制御信号に応じて、ドライバ部11の入力と出力とを短絡させるスイッチSW1及びSW2を有する。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】並列接続された複数の入力回路のうち使用する入力回路を切り替える際に生じる出力ノードの信号ノイズ(ハザード)を防止する。

【解決手段】それぞれが、入力信号INが供給される一つの入力ノードN10に接続し、出力信号OUTを供給する一つの内部出力ノードN11に接続し、互いに電気的特性が異なる第1及び第2の入力回路100A,100Bと、切り替え信号SELを生成し、切り替え信号SELによって、入力回路100A,100Bを制御する入力制御回路300とを備える。入力制御回路300は、入力回路100A,100Bのいずれか一方を活性から非活性へ、いずれか他方を非活性から活性へ切り替えるとき、入力回路100A,100Bが同時に活性状態となる時間を含むように制御する。これにより、入力回路100A,100Bの切り替えに伴う信号ノイズ(ハザード)の発生が防止される。

(もっと読む)

半導体装置

【課題】出力バッファを制御する制御回路部において発生する電源ノイズを低減する。

【解決手段】データ出力端子14を駆動する単位バッファ501〜507と、単位バッファ501〜507を制御するインピーダンス制御回路511〜513と、インピーダンス制御回路511〜513を制御する制御回路部400とを備える。インピーダンス制御回路511〜513と制御回路部400は互いに異なる電源によって動作し、制御回路部400は、互いに逆相であるプルアップデータ及びプルダウンデータをインピーダンス制御回路511〜513に供給し、インピーダンス制御回路511〜513は、逆相であるプルアップデータ及びプルダウンデータを同相に変換して単位バッファ501〜507に供給する。これにより、制御回路部400にて使用する電源VDDにノイズが生じにくくなる。

(もっと読む)

差動出力回路

【課題】ゲート電圧に対する遅延調整を行わずに、クロスポイントの変動を抑えること。

【解決手段】駆動部100と出力部101は、カレントミラー構成により、プロセス、電圧、温度条件が変動しても共に同一の変動となるため、入力信号INTの信号レベルが“H”から“L”に切り替わる際、MOSFET3、6がオンしているときに、MOSFET5、4がオフ状態からオン状態に速く切り替わることはない。従って、クロスポイントの変動を抑えることができる。また、この構成により、ゲート電圧PL、PR、NL、NRは、電源電圧VSSからVDDまでフルスイングされないため、MOSFET3、6をオンさせ、MOSFET5、4をオフさせる場合、ゲート電圧PLの立ち下がりに対してゲート電圧NLの立ち下がりに遅延をもたせたり、ゲート電圧NRの立ち上がりに対してゲート電圧PRの立ち上がりに遅延をもたせたりする必要がない。

(もっと読む)

半導体装置

【課題】データ出力タイミングの設計を簡略化出来る半導体装置を提供すること。

【解決手段】第1クロックCLKに同期してデータを連続的に出力する半導体装置であって、外部から与えられる前記第1クロックCLKから第2クロックICLKを生成するクロック生成回路50、51と、前記第2クロックICLKに同期して動作し、前記データが入力されるフリップフロップ回路52と、前記フリップフロップ回路52から出力される前記データを外部へ出力する出力バッファ回路54と、バンドギャップリファレンス回路22を含み、該バンドギャップリファレンス回路22により制御される電圧VBGRを発生し、該電圧VBGRを前記クロック生成回路50、51、前記フリップフロップ回路52及び前記出力バッファ回路54へ電源電圧として供給する電源回路とを備える。

(もっと読む)

1 - 20 / 148

[ Back to top ]