Fターム[5J039MM16]の内容

Fターム[5J039MM16]に分類される特許

1 - 20 / 351

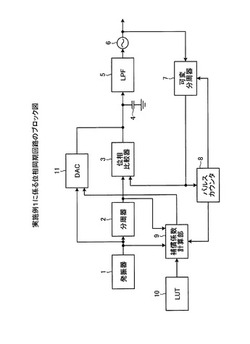

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

クロック分配回路及びクロック分配回路の形成方法

【課題】 28nm以降の半導体プロセスでは、チップ内バラツキが顕著になったため、フィードバックパスにトランジションフォルトが発生する頻度が上がった。従来技術ではフィードバックパスのトランジションフォルトが発生した場合の対策がなく、歩留まり低下につながる。

【解決手段】 クロック信号が分配されるクロックツリーと、クロックツリーの異なる分岐点から出力される複数のフィードバッククロック信号を受信し、各フィードバッククロック信号の位相差を検知する位相比較回路とを有する。位相比較回路によって検知した位相差に基づいて、半導体集積回路内の製造バラツキを補正するためのバラツキ補正済フィードバッククロック信号を生成するフィードバッククロック信号生成回路を有する。フィードバッククロック信号生成回路によって生成されたバラツキ補正済フィードバッククロック信号と基準クロック信号との位相差が小さくなるようにクロック信号を遅延する位相調整回路を有する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に搭載されたデジタル制御発振装置が生成するクロック信号の品質を向上させる。

【解決手段】ICチップは周辺部を除く部位に位置する回路形成部位が、パルス遅延回路10からなる第1回路ブロック3と、時間/数値変換回路20及びデータ処理部30,デジタル制御発振回路40からなる第2回路ブロック5と、第1回路ブロック3及び第2回路ブロック5により形成されるデジタル制御発振装置1にて生成されたクロック信号CKOを利用した各種処理を実行するための周辺回路等からなる第3回路ブロック7とからなる。また、第1回路ブロック3は、電源パッドP1及び電源ラインL1を介して供給される第1の電源VDD1により駆動され、第2回路ブロック5及び第3回路ブロック7は、電源パッドP2及び電源ラインL2を介して供給される第2の電源VDD2により駆動されるように、レイアウトされている。

(もっと読む)

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】半導体装置に含まれるスプリッター回路10は、入力信号INTを受けて反転信号IB1を出力するインバータINV1と、反転信号IB1を受けて非反転信号IT1(第1の出力信号)を出力するインバータINV2が縦続接続される信号パスPASS1を含む。また、スプリッター回路10は、入力信号INTを受けて反転信号IB3(第2の出力信号)を出力するインバータINV3を含む信号パスPASS2を含む。また、インバータINV3と補助インバータINVCは出力信号線を共有する。インバータINV3と補助インバータINVCは、共に、入力信号INTの反転信号を電源とする。

(もっと読む)

遅延ロックドループを内蔵する半導体集積回路およびその動作方法

【課題】擬似ロックを防止するための論理回路の回路規模を低減する。

【解決手段】遅延ロックドループ(DLL)は、複数の可変遅延回路DL0〜8の電圧制御遅延回路1と位相周波数比較器2とチャージポンプ3を具備する。初段の出力PH[0]と最終段の出力PH[8]は、比較器2に供給される。比較器2のアップ信号とダウン信号は、チャージポンプ3に供給される。擬似ロック防止回路4は、第M段の出力PH[1]と第M+1段の出力PH[2]に応答して、可変遅延リセット信号RST_VDL_T、Bを生成する。初段の回路DL0から第M+1段の回路DL2に、クロック入力信号CLKとクロック反転入力信号がリセット信号RST_B、Tとして供給される。第M+2段の回路DL3から最終段の回路DL8に、可変遅延リセット信号RST_VDL_T、Bがリセット信号RST_B、Tとして供給される。

(もっと読む)

コンパレータシステム、アナログデジタルコンバータおよびコンパレータの閾値補正方法。

【課題】 閾値のずれを補正できるコンパレータシステムを提供する

【解決手段】 コンパレータは、一対のキャパシタを介して入力端子から入力信号を受ける一対の入力ノードと、入力信号の電圧差を示す出力信号を出力する出力ノードとを有する。第1制御回路は、コンパレータの閾値を補正する補正期間に、所定量の負荷が出力ノードに接続された状態で、出力信号の論理が反転するまで一対の入力ノードに設定するコモン電圧を変更し、出力信号の論理が反転するときのコモン電圧の値を求め、求めたコモン電圧を補正期間後の通常動作期間に使用する。第2制御回路は、出力ノードに接続される負荷の量を設定する。第3制御回路は、補正期間に、所定量の負荷が出力ノードに接続されているときのコンパレータの標準の閾値の変動量に対応する電圧差を有する第1電圧および第2電圧を入力端子にそれぞれ供給する。

(もっと読む)

クロック生成回路、及びクロック生成方法

【課題】一種類の多相クロックより多くの周波数の種類の単相クロックを得ることができるクロック生成回路及びその方法を提供する。

【解決手段】少なくともn個の位相補間器を有し、周波数がfで位相差が1/(f×m)づつ異なるm相クロックを、周波数がfで位相差が1/(f×n)づつ異なるn相クロックに変換するクロック変換回路1と、前記n相クロック信号の一部又は全部を用いて、周波数(f×n)/Aの単相クロック信号を生成する単相クロック生成回路2と、前記位相補間器に設定する内分比を制御する制御回路とを有し、前記各位相補間器は、前記m相の内の異なる二つのクロックを入力し、それらのタイミング差を、制御回路により設定した内分比で分割した遅延時間のクロックを生成して出力し、前記制御回路は、基準クロックと、回路の末端で分配されたクロックとのタイミングとが一致するように内分比を制御する。

(もっと読む)

半導体装置及びこれを用いた情報処理システム

【課題】遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成する。

【解決手段】縦列接続された遅延回路UD1〜UDnからなり、入力クロック信号IGCKをk周期遅延させるディレイラインと、遅延回路UD1〜UDnからそれぞれ出力される出力クロック信号Node1〜Nodenに基づいて互いに位相の異なる多相クロック信号DTCK1を生成するルーティング回路130とを備える。nとkの最大公約数をGCM、入力クロック信号IGCKの1サイクルをGCK、多相クロック信号DTCK1の相間隔をUIとした場合、相間隔UIの長さは、UI=GCK×GCM/nで与えられる。これにより、1個の遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

(もっと読む)

クロック設定回路および集積回路

【課題】 端子数を低減して集積回路のコストを低減可能とする。

【解決手段】 キャプチャー回路23は、入力端子14−1〜14−4に対する設定入力値SEL1〜SEL4をタイミングT1およびタイミングT2で読み取り、タイミングT1で読み取った設定入力値SEL1〜SEL4をクロック発生回路11に供給し、タイミングT2で読み取った設定入力値SEL1〜SEL4をクロック発生回路12に供給する。また、設定信号生成回路22は、タイミングT1とタイミングT2との間において設定入力値の取り得る値から設定入力値の取り得る別の値へ値が変化する設定信号SET0to1,SET1to0を生成し出力端子15−1,15−2にそれぞれ出力する。

(もっと読む)

チョッパ型コンパレータ

【課題】寄生容量に起因するオフセット電圧を低減するチョッパ型コンパレータを提供する。

【解決手段】本実施の形態に係るチョッパ型コンパレータは、一方端に入力電圧Vinが入力する第1のスイッチ10と、一方端に電圧Vrefが入力する第2のスイッチ16と、一方端が第1のスイッチ10の他方端と電気的に接続されるコンデンサ28と、一方端が第2のスイッチ16の他方端と電気的に接続され、他方端がコンデンサ28の一方端と電気的に接続される第1のダミースイッチ22と、一方端がコンデンサ28の他方端と電気的に接続し、他方端から出力電圧Voutを出力するインバータ30と、一方端がインバータ30の一方端、及びコンデンサ28の他方端、と電気的に接続する第2のダミースイッチ36と、一方端が第2のダミースイッチ36の他方端と電気的に接続し、他方端がインバータ30の他方端と電気的に接続する第3のスイッチ42と、を備える。

(もっと読む)

コンパレータ回路

【課題】プルアップ抵抗の抵抗値や接続する外部回路に依存せず、ハイレベル出力電圧を所望の電圧に精度よく設定することが可能なコンパレータ回路を提供する。

【解決手段】オープンドレイン型またはオープンコレクタ型のコンパレータ2と、一端がコンパレータ2の出力端子5に電気的に接続されたプルアップ抵抗RLと、反転入力端子11がコンパレータ2の出力端子5に電気的に接続され、出力端子12がプルアップ抵抗RLの他端に電気的に接続され、非反転入力端子13にハイレベル出力電圧となる基準電圧V0が印加される増幅回路10と、を備えたものである。

(もっと読む)

位相比較装置

【課題】ステップ応答収束時間だけ待つ必要なく積分値を抽出し、また、入力信号の周波数が既知でなくても抽出した積分値に応じて位相差を演算する位相比較装置を得る。

【解決手段】分周器4が入力信号の周波数を2分周し、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分し、基準積分器7が既知の一定レベルの基準信号を分周器4により設定された周期分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、入力信号の周波数の1/2倍の周波数の整数倍の周波数にヌル点のできるsyncフィルタ特性が形成されることを利用し、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。また、2つの入力信号の周波数が既知でなくても、2つの入力信号の位相差を演算することができる。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

電気遅延型光クロック型トランジスタアレイ

【課題】PDの数を減らし、光遅延分岐回路を必要としない電気遅延型OCTAを提供すること。

【解決手段】伝送線路10に入力パラレル電気信号が入力されたスイッチ20−1〜20−Nが並列に取り付けられている。スイッチ20−1〜20−Nは、ノーマリオフ状態に設定されており、光電変換器30から出力され分岐した電気信号によってONされると伝送線路10に出力シリアル電気信号を構成する電気パルスを生成する。光電変換器30は光パルス又は光ラベルトリガーが照射されると電気信号を出力し、分岐回路40−1〜40〜N、遅延回路50−1〜50−(N−1)を介して各スイッチ20−1〜20−Nに入力する。遅延回路50−1〜50−(N−1)は分岐回路40−1〜40〜Nの間に設置されており、出力シリアル電気信号のビット間隔τに相当する時間差でスイッチ20−1〜20−Nに電気信号が到達するように調整されている。

(もっと読む)

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

CDR回路

【課題】線形位相比較器を用いながら、チャージポンプやVCO等のアナログ回路を不要とすることができ、回路面積を抑えたCDR回路を提供する。

【解決手段】位相比較器902は、データエッジ検出回路111〜114により伝送データのエッジを検出し、データエッジマスク回路115〜118、サンプリング回路119〜122、低域通過型フィルタ123〜126、及びアナログ・デジタル変換回路127〜130により、伝送データのエッジを検出したときの再生クロックの電圧を検出し、検出した電圧に基づいて再生クロックの位相調整を行う。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

1 - 20 / 351

[ Back to top ]