Fターム[5J039EE14]の内容

Fターム[5J039EE14]の下位に属するFターム

直列接続の出力段を持つもの (43)

Fターム[5J039EE14]に分類される特許

1 - 20 / 49

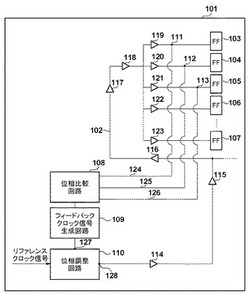

クロック分配回路及びクロック分配回路の形成方法

【課題】 28nm以降の半導体プロセスでは、チップ内バラツキが顕著になったため、フィードバックパスにトランジションフォルトが発生する頻度が上がった。従来技術ではフィードバックパスのトランジションフォルトが発生した場合の対策がなく、歩留まり低下につながる。

【解決手段】 クロック信号が分配されるクロックツリーと、クロックツリーの異なる分岐点から出力される複数のフィードバッククロック信号を受信し、各フィードバッククロック信号の位相差を検知する位相比較回路とを有する。位相比較回路によって検知した位相差に基づいて、半導体集積回路内の製造バラツキを補正するためのバラツキ補正済フィードバッククロック信号を生成するフィードバッククロック信号生成回路を有する。フィードバッククロック信号生成回路によって生成されたバラツキ補正済フィードバッククロック信号と基準クロック信号との位相差が小さくなるようにクロック信号を遅延する位相調整回路を有する。

(もっと読む)

半導体装置

【課題】不揮発性メモリを備えた半導体装置において、高速動作の場合と低速動作の場合とに切替え可能にするとともに、低速動作時の消費電力を従来よりも削減する。

【解決手段】半導体装置1において、クロック生成回路40は、高周波モード時には低周波モード時よりも周波数の高いクロックを生成する。中央処理装置20は、データバス11を介して不揮発性メモリ10から読み出された読出データを取得する。クロック遅延部50Aは、縦続接続された複数段のバッファ55を介した第1の経路51と複数段のバッファ55を迂回した第2の経路52とを含む。クロック遅延部50Aは、高周波モード時には、クロック生成回路40からのクロックを第1の経路51を介して中央処理装置20に供給し、低周波モード時には、クロック生成回路40からのクロックを第2の経路52を介して中央処理装置20に供給する。

(もっと読む)

デジタル信号処理装置

【課題】フレーム同期式のDSPにおいて、動作クロックの異なる信号処理回路間のデータの受け渡しを簡便に実現する。

【解決手段】各々の動作クロックの異なる複数の信号処理回路のうちから送信側回路と受信側回路を定め、各信号処理回路の動作クロックの全ての立ち上がりエッジが揃うタイミングをデータ受け渡しタイミングとする。送信側回路には、当該送信側回路に与えられるタイミング信号がアクティブレベルであることを条件にデータを出力させる一方、受信側回路には、各動作クロックの周波数の約数を周波数とし、かつデータ受け渡しタイミングを跨ぐ所定期間に亘ってアクティブレベルとなるフレーム同期信号がアクティブレベルであることを条件に、送信側回路から出力されるデータを取り込む処理を実行させる。

(もっと読む)

多相クロック生成回路

【課題】N相から2N相に切り替わったときに位相関係が不適切にならないようにする。

【解決手段】多相クロック生成回路は,基準クロックに同期して0°,90°の位相の中間クロックを生成する第1の分周器と,0°の中間クロックに同期して0°,90°の位相の第1群の出力クロックを生成する第2の分周器と,90°の中間クロックに同期して45°,135°の位相の第2群の出力クロックを生成する第3の分周器と,第1の分周器と第3の分周器との間に設けられ,切替信号に応じて,90°の中間クロックまたは固定値のいずれかを第3の分周器に供給するセレクタとを有する。さらに,切替信号が2N相モードのときに,第1群の出力クロックと第2群の出力クロックの位相関係にエラーがあるか否かを検出するエラー検出回路と,エラー検出回路がエラーを検出したときに基準クロックと非同期のタイミングで2N相モードの切替信号をセレクタに出力する再リセット回路とを有する。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

送信回路および通信システム

【課題】複数送信レーン間の同期を行うために分配する制御信号のタイミング制約を緩和でき、設計工数を削減することが可能な送信回路および通信システムを提供する。

【解決手段】並列に配置され、供給されるパラレルデータをシリアルデータに変換して出力する複数のレーン部330−0〜330−3と、基準クロックに位相同期した駆動クロックを、イネーブル信号CLKENに応じた駆動クロックの複数サイクル分経過してから複数のレーン部に出力するクロックイネーブラ部320とを有し、複数のレーン部330−0〜330−3の各々は、クロックイネーブラによる駆動クロックを分周して分周クロックおよびロード信号を生成する分周器331−0〜33−3と、分周器による分周クロックおよびロード信号、並びに駆動クロックに同期してパラレルデータをシリアルデータに変換するパラレルシリアル変換器332−0〜332−3と、を含む。

(もっと読む)

信号処理装置および試験装置

【課題】制御チップに占める制御回路の面積を低減し、且つ、制御信号を出力する出力部の数を低減しつつ、複数の命令信号の処理時間の増大を抑制する。

【解決手段】複数チャネルの被制御回路を制御する制御信号を生成する信号処理装置であって、それぞれの被制御回路に対する命令信号を共通の入力部で受け取り、受け取った命令信号に応じて制御信号を生成し、それぞれの被制御回路への制御信号を共通の出力部から出力する制御チップと、制御チップが出力するそれぞれの制御信号を、対応する被制御回路に分配する分配回路とを備える信号処理装置を提供する。

(もっと読む)

クロック分配回路及びその回路を含む半導体回路装置

【課題】

半導体チップを製造する際の製造バラツキ又は半導体チップ内の半導体回路の動作条件による、複数の最終バッファから出力される複数のクロック間の位相差を軽減することが可能なクロック分配回路を提供することを目的とする。

【解決手段】

回路装置内に配置されたクロック分配回路であって、リング状のクロック配線と、前記クロック配線に接続し、自己発振により、前記クロック配線内に第1クロック信号を発生させる発振回路と、前記回路装置内において、2以上の場所それぞれに、配置され、第2クロック信号を出力する2以上の位相調整回路と、を備え、前記位相調整回路それぞれは、配置場所に応じた位相を有する前記第1クロック信号を受け取り、前記位相調整回路それぞれが受け取った前記第1クロック信号間の位相差よりも、前記位相調整回路それぞれが出力する前記第2クロック信号間の位相差を減じる調整を行うことを特徴とするクロック分配回路。

(もっと読む)

単一クロック共有形コンピュータシステム

【課題】 音楽編集、音楽再生や画像映像編集再生等を行うコンピュータにおいて多数の異なる発振子から発生させたクロックを利用する為に生じた雑音発生による音楽再生編集品質の劣化、および映像や画像処理の品質の劣化を防止し、かつ使用発振子の数を減らし、さらに音楽と映像、または複数ある機器の同期タイミングをとるための遅延時間を少なくすることを目的とする。

【解決手段】 一台または複数台のコンピュータで使われているCPUや周辺回路を動作させるクロックと、クロックを利用する周辺機器又は外部機器を、単一の基準クロックから生成したクロックを用いて動作させる。

(もっと読む)

多相クロック生成回路

【課題】

位相ノイズが少ない多相クロック生成回路を提供する。

【解決手段】

多相クロック生成回路は,基準クロックを生成する基準クロック生成器と,リング状に接続された複数の遅延回路を有し,前記複数の遅延回路がそれぞれ位相がずれた出力クロックを出力する多相クロック発振器と,前記複数の遅延回路のいずれかの出力端子に前記基準クロックを供給する基準クロック注入回路とを有する。多相クロック発振器のクロックの位相ノイズを低減し周波数変動が抑制できる。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

電子回路、電子機器、デジタル信号処理方法

【課題】多相クロックを使用してデジタル信号処理を行なう場合に、クロック信号の各位相関係を正しく保ったまま高速動作が要求される各デジタル信号処理部まで多相クロックを分配できるようにする。

【解決手段】基準タイミング生成部110は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低い基準タイミング信号J0を生成して局所タイミング再生部120に供給する。局所タイミング再生部120は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低いクロック信号であって、高速信号処理部140におけるデジタル信号処理の基準となる複数のクロック信号でなる多相タイミング信号J2を生成して高速信号処理部140に供給する。高速信号処理部140と局所タイミング再生部120を1対1で設け、1つの局所タイミング再生部120から複数の高速信号処理部140へ多相タイミング信号J2を分配しないようにする。

(もっと読む)

クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法

【課題】クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法を提供する。

【解決手段】クロック情報及びデータ情報を含む差動信号対を受信するにおいて、差動信号対の共通電圧レベルの変化を利用してクロック信号及びデータを復元できる、クロック情報及びデータ情報を含む信号を受信する受信器及びクロック埋め込みインターフェース方法である。

(もっと読む)

クロック分配回路およびクロック分配方法

【課題】クロック分配網間のクロックスキューをより低減する。

【解決手段】リファレンスクロック信号11の位相を調整してクロック分配網に分配するPLL回路1、2と、クロック分配網における複数のフィードバック点PA1〜PAn、PB1〜PBnからそれぞれフィードバッククロック信号HA1〜HAn、HB1〜HBnを入力し、PLL回路1、2でリファレンスクロック信号11の位相比較対象とされる複数のフィードバッククロック信号から一つの信号を、複数のフィードバッククロック信号のそれぞれの遅延値に基づいて選択するフィードバッククロック信号選択回路9、16と、を複数のクロック分配網のそれぞれに対応して備える。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

信号生成回路

【課題】 プロセス要因で生じるクロック信号の位相バラツキを抑える。

【解決手段】 信号生成回路100は、クロック信号PLLCKが通るクロック信号線30に1以上のクロックバッファ31が配置され、1以上のクロックバッファ31によりクロック信号PLLCKを遅延させ、遅延したクロック信号に基づき所定の信号を生成する。この信号生成回路100は、前記クロックバッファ31と同一チップ上に形成された複数のクロックバッファ41を有して構成される参照用クロックバッファ40と、参照用クロックバッファ40の遅延量を検知し、この遅延量と予め定められた遅延量との差に基づく位相調整信号PHADJを出力する遅延検知回路50と、位相調整信号PHADJに応じて、クロック信号PLLCKの位相を変える位相調整回路20と、を備える。

(もっと読む)

半導体デバイスおよびディスプレイ装置

【課題】クロック信号の復帰時に発生する誤動作を防止する。

【解決手段】クロック分配回路10は、クロック信号CKを受け、複数の経路P1〜P3に分配する。デジタル回路30は、複数の経路P1〜P3に対応づけられた複数の領域R1〜R3に分割されている。各領域R1〜R3が共通の電源電圧Vddを受ける。また各領域R1〜R3はクロック分配回路10により分配されたクロック信号CK1〜CK3と同期動作する。クロック分配回路10は、クロック信号CKが非入力状態から入力状態に遷移するとき、複数の経路P1〜P3それぞれに対して、時間差を付けてクロック信号を分配する。

(もっと読む)

クロック生成装置、集積回路装置、電子機器及びクロック生成方法

【課題】故障検出率の向上を図る一方で、通常動作時において低消費電力化を実現できるクロック生成装置、集積回路装置、電子機器及びクロック生成方法を提供する。

【解決手段】複数のFFと、前記FFを構成する2つのFFの間に挿入された組み合わせ回路と、該組み合わせ回路の所定のノードをプローブする1又は複数のプローブ用FFとを含む回路ブロックに対し、クロックを生成するクロック生成装置は、基準クロックの位相を調整して位相調整クロックを生成する位相調整回路と、第1の動作モードにおいて、前記位相調整回路への前記基準クロックの入力を停止するクロック停止制御回路とを含み、前記第1の動作モードにおいて前記基準クロックを前記FFに出力し、第2の動作モードにおいて前記基準クロックを前記FFに出力すると共に、前記位相調整クロックを前記1又は複数のプローブ用FFに出力する。

(もっと読む)

タイミングコントローラ、ディスプレイドライバー及びそれを備えたドライバーモジュール及びディスプレイ装置、及び信号伝送方法

【課題】タイミングコントローラを提供する。

【解決手段】タイミングコントローラは、クロック発生器とデータ処理部とを具備する。クロック発生器は、第1クロックを受信するとともに、第1クロックの周波数と異なる周波数を有する第2クロックを生成し、かつ、該生成された第2クロックを多数のディスプレイドライバーのそれぞれに伝送する。データ処理部は、データを受信するとともに、該受信されたデータを変換し、かつ、該変換されたデータを第1クロックに基づいて、多数のディスプレイドライバーのそれぞれにポイントツーポイント方式で分配する。

(もっと読む)

信号の較正方法および装置

信号較正方式において、一連の複数の信号の間で所望の位相関係が維持される。たとえば、いくつかの態様では、高速度の基準クロック信号から発生したクロックツリーの所望の位相を、低速度の基準クロック信号と、クロックツリーの様々な位相に関連付けられた低速度のクロック信号との間の位相差を検出することにより、維持することが可能である。いくつかの態様では、クロックツリーの使用中に発生するフレーミングオフセットを検出することにより、クロックツリーの所望の位相を維持することが可能である。 (もっと読む)

1 - 20 / 49

[ Back to top ]