Fターム[5J065AC04]の内容

Fターム[5J065AC04]に分類される特許

1 - 20 / 33

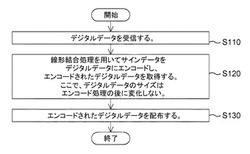

デジタルデータのエンコード又はデコード方法、データ配布装置、およびデータ管理装置

【課題】デジタルデータのエンコード又はデコード方法、データ配布装置、およびデータ管理装置を提供する。

【解決手段】デジタルデータのエンコード方法は、以下のステップを有する。デジタルデータが受信される。線形結合処理を用いて、サインデータがデジタルデータにエンコードされ、エンコードされたデジタルデータが取得される。ここでデジタルデータのサイズはエンコード処理後において変化しない。エンコードされたデジタルデータが配布される。

(もっと読む)

二次元コード生成装置、画像形成システム、二次元コード読み取り装置、コンピュータプログラム及び媒体

【課題】ビット列をシャフリングする等の複雑かつ負荷の大きい処理を必要とせずに、バースト的に発生した読み取り誤りを訂正できる二次元コードを生成する。

【解決手段】本発明に係る二次元コード生成装置1は、符号化する情報である符号化情報を分割して得られる分割情報のそれぞれに誤り訂正符号を付して符号化した分割情報符号のそれぞれに基づいて1単位の二次元コードである分割情報コードを生成する分割情報コード生成手段と、前記分割情報符号のそれぞれから対応する情報を抽出して得られる交差情報に誤り訂正符号を付して符号化した交差情報符号に含まれる前記誤り訂正符号のそれぞれから対応する情報を抽出して得られる交差情報訂正符号のそれぞれに基づいて1単位の二次元コードである交差情報訂正コードを生成する交差情報訂正コード生成手段と、を有する。

(もっと読む)

フラッシュファイルシステムの誤り検出訂正機能

【課題】フラッシュファイルシステムのようなフラッシュメモリにデータを読み書きする場合は誤り訂正手段が不可欠である。しかし、誤り検出、訂正機能を使用するときの演算量は大変多くの時間を消費する。

【解決手段】そこで、新しい間のフラッシュメモリはほとんど誤りが無く、誤り訂正の必要は少ない、ところが経年により誤りの発生数は急激に増加し、誤り訂正の必要性が急に増加する。本発明はこのようなフラッシュメモリの特性に鑑み、フラッシュメモリが新しい間は誤り数が少ないと予測し、できるだけ誤り検出、訂正の時間を少なくする方法を発明した。

(もっと読む)

情報担持片、機械読取方法及び復号方法並びに記録媒体

【課題】 貴重印刷物等に付与された偽造防止要素を、機械によって読み取ったパターンにエラーが発生した場合においても正しい情報を得ることができる情報担持片及び復号方法並びに記録媒体を提供する。

【解決手段】 二元符号で、かつ、機械読取可能なセルが配設された情報担持片であって、前述のセルは、情報担持片の長辺方向に沿って、a個で1パターンを形成して繰り返され、少なくともb個(bはaの倍数)配置され、パターンは、情報を表現するための符号化されたデータであり、a個で形成されるパターンの二元系列から成る符号長及び符号語の第一の符号は二元から成る長さa個の系列すべての集合から最小片方向巡回ハミング距離又は最小双方向巡回ハミング距離がc(cは0以上の整数)となる部分集合を選択することで、(bc/a-1)/2を超えない最大の整数個のセルの誤り訂正が可能と成ることを特徴とする。

(もっと読む)

半導体記憶装置、その制御方法、および誤り訂正システム

【課題】誤り訂正能力を損なうことなく消費電力及び回路規模を低減することが可能な半導体記憶装置、その制御方法、および誤り訂正システムを提供することを目的とする。

【解決手段】SSD100のECC回路40は、読み出しデータに対して、第1誤り訂正符号(ハミング符号)を用いて第1誤り訂正し、この第1誤り訂正結果を、第2誤り訂正符号(BHC符号)を用いてさらに第2誤り訂正し、さらに、第2誤り訂正結果を、第3誤り訂正符号(RS符号)を用いて第3誤り訂正する。

(もっと読む)

チェンサーチ装置およびチェンサーチ方法

【課題】チェンサーチ処理を高速化することが可能なチェンサーチ装置およびチェンサーチ方法を提供することを目的とする。

【解決手段】不揮発性メモリから読み出されたデータに含まれる誤りを訂正する場合の誤り位置計算を行うチェンサーチ装置において、入力データの誤り訂正対象領域に対して、少なくとも1ビット単位で誤り位置の探索処理を行う第1の処理部と、前記入力データの誤り訂正対象外領域に対して、複数ビットを一度に処理する第2の処理部と、を備えている。

(もっと読む)

計算基底軸設定装置、計算基底軸設定方法、プログラム及び記録媒体

【課題】従来よりも少ない物理量子ビットを用い、対称性のあるノイズとランダムなノイズとの古典的な混合からなるノイズに対する誤り訂正を行う。

【解決手段】計算基底軸設定部13が、各物理量子ビットに共通の基準計算基底軸に対する、j〔j∈{1,...,n} ,n≧2〕番目の物理量子ビットQjの計算基底軸の回転を示す2×2のユニタリー行列Vjを設定し、計算基底軸評価部14が、量子誤りの無い状態に対する、対称性のあるノイズによる量子誤りを訂正した後の状態のフィデリティに基づいて、設定された行列Vjを採用するか否かを判定する。

(もっと読む)

メモリ装置

【課題】4ビットエラーが検出訂正可能なECCシステムを搭載したメモリ装置を提供する。

【解決手段】BCHコードを利用して読み出しデータのエラーを検出し訂正するエラー検出訂正システムが搭載されたメモリ装置において、前記エラー検出訂正システムは、4ビットエラーが検出訂正可能であって、4次のエラー位置探索方程式を、2以上の低次の因子方程式に分解し、それらの因子方程式を解くに当たって変数変換により未知数部分とシンドローム部分とに分離し、予めテーブルとして求められた解の候補のインデックスとシンドロームのインデックスとを比較してエラー位置を求める。

(もっと読む)

復号化装置

【課題】所定の符号則で符号化されたデータを復号化する際に、簡単な構成で、高速に誤り訂正を行うことが可能な復号化技術を提供する。

【解決手段】復号化部は、入力された4ビットの符号化データのビット列(例えば“0011”)と、符号則において情報データが変換される5種類の変換先ビット列のそれぞれとの間の符号間距離に基づいて、当該符号化データのビット列を、当該5種類の変換先ビット列のいずれか一つ(例えば“0010”)に割り当てる。そして、復号化部は、入力された符号化データのビット列を、その割り当てた変換先ビット列に対応する2ビット情報データのビット列(例えば“10”)に変換する。

(もっと読む)

半導体記憶装置

【課題】ECC回路を搭載した半導体記憶装置において、ユーザデータの入出力に際し、データの信頼性が高く、従来の装置とも互換性を備えかつユーザデータの記憶容量の高い半導体記憶装置を提供する。

【解決手段】ECC回路205に入力されるデータのビット数を、書き込みのため外部から入力されるデータのビット数よりも多くすることにより、メモリセルアレイ201に書き込まれるユーザデータに対するパリティビットの比率を低減させる。結果、従来装置に比べてメモリセルにおけるパリティビット用の記録領域の占める割合を低下させることで、集積密度が同一のメモリセルアレイにおいて、ユーザが利用可能な記憶容量を高くしている。

(もっと読む)

誤り訂正確率を減らすエラー訂正回路、その方法及び前記回路を備える半導体メモリ装置

【課題】誤り訂正確率を減らすエラー訂正回路、その方法及び前記回路を備える半導体メモリ装置を提供する。

【解決手段】本発明によるエラー訂正回路は、ECCエンコーダ及びECCデコーダを備える。ECCエンコーダは、情報データ及び生成多項式に基づいて、h(2以上の整数)ビットエラー訂正が可能なシンドロームデータを発生させる。ECCデコーダは、情報データとシンドロームデータを含む符号データとに基づいて、情報データから最大(h−j)ビットのエラー位置を算出する単一モードで動作できる。ECCデコーダは、情報データとシンドロームデータを含む符号データとに基づいて、情報データから最大hビットのエラー位置を算出する第1動作モードまたは情報データから最大(h−j)ビットのエラー位置を算出する第2動作モードで動作できる。

(もっと読む)

行列対角化方法、行列対角化装置、復号装置、およびプログラム

【課題】行列の対角化処理の高速化を図ることが可能な行列対角化方法、行列対角化装置、復号装置、およびプログラムを提供する。

【解決手段】行列対角化装置100は、行列を記憶する行列メモリ120と、行のインデックスを記憶する行インデックスメモリ110と、要探索、掃き出しを行う要探索、掃き出し回路130と、を含み、行インデックスメモリ110から順に行インデックスを読み出し、その行インデックスが指定する行を行列メモリ120から読み出し、当該行の対角化の対象となる列の要素を見て、要探索、掃き出しを行う機能を有し、要探索の対象とする要素をその要素を含む行が未だ要行になっていない要素のみに限定する。

(もっと読む)

LDPCおよびインターリーブによるマルチレベル信号メモリ

本発明の実施形態は、LDPCおよびインターリーブによるマルチレベル信号メモリを提供する。したがって、本発明のさまざまな実施形態は、複数のメモリセルを有するメモリブロックを備えるメモリ装置を提供する。各メモリセルは、マルチレベル信号により動作する。このようなメモリ装置は、メモリセルに書き込まれるデータ値をLDPC符号化する低密度パリティチェック(LDPC)コーダと、ビットインターリーブ符号化変調(BICM)をLDPC符号化データ値に適用することにより、BICM符号化データ値を生成するインターリーバとをさらに備える。他の実施形態も記載されかつ請求される。 (もっと読む)

記憶された情報データの読み取りのための誤り訂正と誤り検出の方法およびそのための記憶制御ユニット

【課題】記憶された情報データの読み取りのための誤り訂正および誤り検出方法、およびそのための記憶装置

【解決手段】本発明は、記憶装置(M)からの記憶された情報データ(D(8:1))の読み取り(3−5)のための誤り訂正および/または誤り検出方法であって;情報データ(D(8:1))に加えてコードデータ(C(4:1))が記憶装置(M)から読み出され、読み出されたデータにおける誤りおよび/または誤り位置を決定するために情報データ(D(8:1))とコードデータとからシンドロームデータ(S(4:1))が形成され;多重誤りの検出のために、決定された誤り位置の場合、関連記憶位置に関連する情報データ(D(8:1))またはコードデータ(C(4:1))がすべて0か、すべて1かが検証される誤り訂正および/または誤り検出方法に関する。

(もっと読む)

データ蓄積装置及びエラー訂正方法

【課題】HDDアレイユニットにおいて、パリティ用のデコーダの処理効率を向上させることにより、パリティ用のHDDを3台以上設けることによってエラー訂正能力を高めるような場合にもデータ転送速度の低下を防止する。

【解決手段】所定のタイムスロット毎にエラー訂正処理の複数の工程を並列的に実行することにより、順次供給される符号語についてのエラー訂正処理をパイプライン処理によって行うデコーダを備える。

(もっと読む)

データ処理方法

【課題】ソフトウェアによるECC処理を能率的に行うための技術を提供する。

【解決手段】nビットのデータに対してECCコードをmビットとするとき、mビットの相互に異なる2進数をm+n列に並べた行列テーブルをフラッシュメモリの記憶領域(20Bb)に固定データとして形成し、ECCコード生成プログラムの処理にその行列テーブルを参照させる。ECCコードの生成において、データの論理値“1”のビット位置に対応する前記行列テーブルの列の値を行方向のビット毎に排他的論理和を採り、これによって得られたmビットの値をECCコードとし、データにECCコードを付加してm+nビットの符号語を生成する。

(もっと読む)

誤り検出/訂正回路及び方法

1つ以上の情報ビット又は1つ以上のペイロードデータビットの形式の情報と、1つ以上の検査ビット又は1つ以上の冗長ビットの形式の冗長性とを具える少なくとも1つのデータワードの少なくとも1つの誤りを検出及び/又は訂正する誤り検出/訂正回路(100;100’)並びに方法において、それぞれのデータワードに補足される少なくとも1つの検査ビット又は冗長ビットを最適化し、特に少なくとも1つの物理的メモリスペースをアプリケーションの要求に依存して最適に使用可能にするために、この誤り検出/訂正回路及び方法は、

少なくとも1つの第1のデータパス(30;30’)に割り当てられ、少なくとも1つの第1の誤り訂正スキームを実行するとともに、

少なくとも1つの第2のデータパス(40;40’)に割り当てられ、少なくとも1つの第2の誤り検出/訂正スキームを実行するよう設計され、且つ前記第2のデータパスを経て伝送されるそれぞれのデータワードの前記情報及び/又は前記冗長性、特に前記1つ以上の情報ビット又は前記1つ以上のペイロードデータビットの数及び/又は前記1つ以上の検査ビット又は前記1つ以上の冗長ビットの数を増大させるように設計された少なくとも1つの第2の誤り訂正スキームを実行することを提案する。  (もっと読む)

(もっと読む)

フラッシュエラー訂正

【課題】書き換え可能メモリに書き込まれるデータおよびこのメモリから読み出されるデータにエラー訂正アルゴリズムを適用するデータ処理装置を開示する。

【解決手段】前記データ処理装置はハードウェアで実現されたコーディングユニットを備え、このコーディングユニットはコーディング動作を実行でき、このコーディングユニット動作において、コーディングユニットはメモリに書き込まれる第1データセットを受け取り、エラー訂正アルゴリズムに従ってそのデータを処理して第2データセットを生成し、第2データセットを出力してメモリに書き込む。前記データ処理装置はさらにソフトウェアで実現されたエラー訂正ユニットを備える。

(もっと読む)

量子回路、量子誤り訂正装置および量子誤り訂正方法

【課題】誤り訂正処理の計算量を削減して、量子誤り訂正の効率を向上させること。

【解決手段】量子誤り訂正装置において、符号キュービット群を入力して、シンドロームを出力するシンドローム出力回路111と、出力されたシンドロームに対してシンドロームの観測を用いた量子誤り訂正処理で観測されて古典情報となったシンドロームを入力して誤り位置情報を出力する古典論理回路を構成する基本論理素子の集合のそれぞれと同一の演算を量子状態の各基底に対して実行する量子ゲートである量子基本論理素子を作用させることによって、量子状態の基底として表現されている複数のシンドロームパターンに対して同時に誤り位置計算を行い、符号語情報における誤りの位置を示す誤り位置情報を求める誤り位置算出回路112と、誤り位置情報に基づいて符号語情報に生じた誤りを訂正する訂正回路113とを備えた。

(もっと読む)

同時メモリアクセスを利用したメッセージ伝達デコーディング装置及び方法

【課題】同時メモリアクセスを利用したメッセージ伝達デコーディング装置及び方法が開示される。

【解決手段】それぞれの記憶場所は、複数のプロセスノードを含むデコーダのプロセスノードを連結するエッジのそれぞれに割り当てられる。コーディングされた入力信号はデコーダに適用して、デコーディングされた出力信号を生成する。この際、エッジ値はプロセスノード動作中に記憶場所のうち、複数の記憶場所は、同時にアクセスされるように、記憶場所から反復的に更新され、記憶場所に提供される。プロセスノードは、可変ノードとチェックノードとを含むことができ、エッジは可変ノードとチェックノードとを連結するエッジを含む。本発明は、方法、装置、及びコンピュータプログラム製品として具体化される。

(もっと読む)

1 - 20 / 33

[ Back to top ]