Fターム[5J081CC41]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 寿命劣化防止 (6)

Fターム[5J081CC41]に分類される特許

1 - 6 / 6

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

発振周波数補正信号発生回路

【課題】発振周波数とは別の周波数を生成するための回路を別途設けることなく、発振周波数を補正することができるようにする発振周波数補正信号発生回路を提供する。

【解決手段】発振信号を互いに異なる遅延時間にて遅延させて複数の遅延信号を生成し、当該遅延信号の各々に基づくタイミングにて当該発振信号を1周期単位でサンプリングして周期毎のサンプル値群を生成し、互いに異なる時点の2つの測定対象周期における当該サンプル値群の一連のサンプル値を比較してその比較結果に応じて前記補正信号を生成する。

(もっと読む)

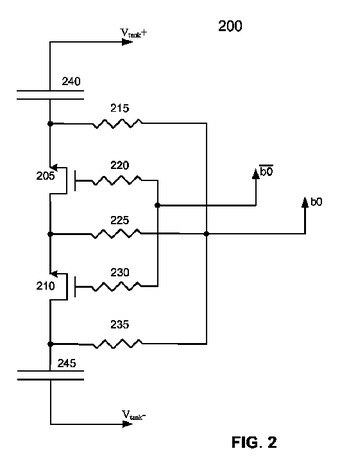

キャパシタスイッチング回路

キャパシタンススイッチング素子(200)が、トランジスタ(205、210)によって直列に接続された、第1のキャパシタ(240)と第2のキャパシタ(245)とを含む。トランジスタのゲートは、一組の抵抗器(220、230)を介して第1の信号(b0/)によってバイアスをかけられ、ソースおよびドレインは、第2の組の抵抗器(215、225、235)を介して第2の信号(b0)によってバイアスをかけられる。信号はレベルシフトされており、相補的であってよい。素子をオンにするためには、第1の信号(b0/)をVDDに設定することができ、第2の信号(b0)をゼロに設定することができる。素子をオフにするためには、第1の信号(b0/)をVDD/2の倍数に設定することができ、第2の信号(b0)をVDD/2の倍数プラス1(the multiple plus one)に設定することができる。素子が発振器同調回路で使用されるとき、トランジスタの圧力ストレスが低減され、トランジスタを薄酸化物で製作することができる。発振器は、セルラアクセス端末のトランシーバにおいて使用されてもよい。  (もっと読む)

(もっと読む)

半導体発振回路および携帯電話

【課題】基準周波数生成回路は、ロジック回路の電源ノイズの影響を受けて、周波数偏差やピリオドジッターの悪化を引き起こしていた。

【解決手段】CPUや周辺回路などのロジック回路12の電源はレギュレータ13より供給し、基準周波数生成回路11の電源には電源の高周波ノイズを10dB以上の減衰量を持つローパスフィルター10を介してから供給する。これによりロジック回路12で発生する高周波ノイズ起因での周波数偏差やジッターの悪化を抑えることができ、この基準周波数をUARTシリアル回路に接続して通信ができる。

(もっと読む)

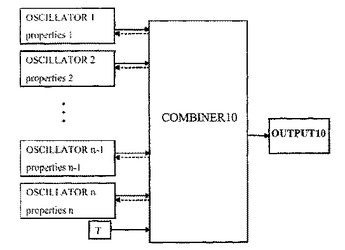

基準発振器の周波数安定化

従来技術の不利な点を取り除き、特性(1)高い長期安定性、(2)低位相雑音、(3)高耐熱性、(4)その基準発振器の周波数についての正確な値、を改善したMEMS基準発振器を提供することが、本発明の目的である。  (もっと読む)

(もっと読む)

弾性表面波センサー内蔵発振回路及びバイオセンサー装置

液体が付着した場合であっても、バイアス電圧の印加による電極膜の剥離が生じ難く、かつ安定に動作させ得る弾性表面波センサー内蔵発振回路を提供する。 圧電基板上にインターデジタル電極33,34と、インターデジタル電極33,34を覆うように、検出対象物質または検出対象物質を結合する結合物質を結合する反応膜が設けられており、微小な質量負荷を周波数変化により検出することを可能とする弾性表面波センサー32が共振子として接続されている弾性表面波センサー内蔵発振回路であって、弾性表面波センサー32に対して、直列に直流カット用コンデンサ36,42が接続されており、該直流カット用コンデンサ36,42が、それぞれ、インピーダンス整合回路を構成している、弾性表面波センサー内蔵発振回路31。 (もっと読む)

1 - 6 / 6

[ Back to top ]