Fターム[5J106SS02]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 細部の構成 (94) | LPF・積分器の具体的回路が示されたもの (12)

Fターム[5J106SS02]に分類される特許

1 - 12 / 12

周波数シンセサイザ

【課題】ディジタル処理を用いたPLLにより周波数シンセサイザを構成するにあたって、A/D変換部を不要とすること。

【解決手段】設定周波数に応じたディジタル値を積分することにより、位相信号となる鋸波を生成する。一方電圧制御発振器から出力される周波数信号を分周回路を介してエッジ検出部に入力し、前記周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた矩形波信号を生成する。そしてラッチ回路にて、前記矩形波信号により鋸波の値をラッチし、この値をループフィルタにて積分し、電圧制御発振器の制御電圧とする。

(もっと読む)

信号レベル調整装置及び高周波機器

【課題】電圧制御発振器の後段に設けられた可変減衰器と、検波器と、検波電圧に応じてディジタル/アナログ変換器を介して可変減衰器の減衰量調整用の制御電圧を出力する制御部と、を備えた周波数シンセサイザにおいて、ディジタル/アナログ変換器の出力変化に基づくスプリアスを抑制できる技術を提供すること。

【解決手段】ディジタル/アナログ変換器の出力側と可変減衰器との間にローパスフィルタを設けて、ディジタル/アナログ変換器の出力の変化時に発生するオーバーシュートに対応する周波数成分をカットする。そして制御部が制御電圧を出力してから検波器で検出された信号レベルを読み込むまでの時間は、ローパスフィルタのカットオフ周波数で決まる当該ローパスフィルタの時定数よりも長い時間に設定し、信号レベルの自動制御動作に影響がないようにする。

(もっと読む)

フラクショナル−N方式位相同期ループ形周波数シンセサイザ

【課題】 位相比較器の位相差に対する検波電圧特性の非線形性によって、F−N方式PLL周波数シンセサイザ出力に発生するスプリアスの抑圧を実現することを目的とする。

【解決手段】 高周波信号を生成する電圧制御発振器と、前記高周波信号より同期信号を生成する可変分周器と、基準信号を生成する基準発振源と、前記基準信号より位相差を有する2つの基準信号を生成する基準信号生成手段と、前記それぞれの基準信号と前記同期信号を入力とし、第1と第2の位相比較信号を出力する第1の位相比較器と、第3と第4の位相比較信号を出力する第2の位相比較器と、前記第1と第2の位相比較信号を差分した差分結果と、前記第3と第4の位相比較信号を差分した差分結果を合成して平滑化した合成信号を出力するループフィルタとを備え、前記合成信号に応じて電圧制御発振器を制御することにより前記高周波信号を生成する。

(もっと読む)

PLL周波数シンセサイザ

【課題】ループフィルタの帯域幅切換時の周波数変動を低減することによって、高速に周波数切換が可能なPLL周波数シンセサイザを提供する。

【解決手段】本発明の一実施形態のPLL周波数シンセサイザ1は、分周器30と、位相比較器40と、チャージポンプ50と、ループフィルタ60と、電圧制御発振器70と、切換スイッチ(切換部80の内部)とを備える。ループフィルタ60は、半導体基板上の基準電位を接地電位とし、切換スイッチは、半導体基板2上に形成され、ループフィルタ60の時定数を切り換えるためにループフィルタ60の中間ノードと半導体基板2上の基準電位とを接続するか否かを切り換える。

(もっと読む)

フィードフォワード分割器を有する適応帯域幅位相ロックループ

【課題】位相ロックループを提供する。

【解決手段】一部の実施形態では、チップは、第1及び第2の電圧制御式発振器(VCO)出力信号を供給するための第1及び第2のVCOと、第1及び第2VCO出力信号の第1及び第2の周波数を第1及び第2の分周率によって分割するための第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)を含む。チップはまた、第1及び第2分周率を選択するための位相ロックループ制御回路を含む。他の実施形態も説明して特許請求する。

(もっと読む)

周波数シンセサイザおよびこれに用いるループフィルタ

【課題】コンデンサの容量値を小さくしてループフィルタのIC化を容易にし、かつ、周波数シンセサイザの同期状態に関係なくC/N特性やスプリアス特性を改善できるようにする。

【解決手段】並列接続された複数のコンデンサC1〜Cnと、これらのチャージ/ディスチャージ動作をパイプライン処理として行うように切り替えを行うスイッチSW11〜SW1n,SW21〜SW2nと、複数のコンデンサC1〜Cnを備えた並列回路の出力側に接続されたコンデンサCHとを備えてLPF15を構成し、各コンデンサC1〜Cnに順次チャージされた電荷が並列回路の出力として得られ、それがコンデンサCHに順次に蓄積されるようにすることにより、各コンデンサC1〜Cn,CHの容量値を小さくすることにより時定数が小さくなっても、回路全体として大きな時定数を実現できるようにする。

(もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】位相比較器のフリップフロップ間の誤差に起因するスプリアスを抑圧することができる位相同期ループ形周波数シンセサイザを得ることを目的とする。

【解決手段】位相比較器33から出力された位相比較信号Dnu(t)を第1の利得値αnuで電圧増幅するとともに、その位相比較器33から出力された位相比較信号Dnd(t)を第1の利得値αnuと異なる第2の利得値αndで電圧増幅し、電圧増幅後の位相比較信号Dnu(t)と電圧増幅後の第2の位相比較信号Dnd(t)との差分信号を出力する減算回路33を設ける。

(もっと読む)

PLL回路及びチャージポンプ回路の駆動方法

【課題】PLL回路のロック時のループフィルタの出力電圧の変動を抑えることである。

【解決手段】基準クロック信号と帰還クロック信号の位相が一致したとき、基準クロック信号と帰還クロック信号の立ち下がりのタイミングで、オン時間の短いUP信号とDOWN信号をチャージポンプ回路の2個のMOSトランジスタに供給する。これにより、チャージポンプ回路の貫通電流を少なくできるので、貫通電流によるループフィルタの出力電圧の変動を抑えることができる。

(もっと読む)

周波数シンセサイザ、通信機、及び周波数シンセサイズ方法

【課題】高精度のクロックを高速に切り換えることの出来る周波数シンセサイザ、通信機、及び周波数シンセサイズ方法を提供する。

【解決手段】高精度に生成された基準クロックを元に、デジタル的な演算とD/Aコンバータ、ローパスフィルタを用いて所望の周波数の正弦波信号を発生させ、その正弦波信号を元の基準クロックとミキシングし、適切なフィルタを通す事で所望の周波数の正弦波を生成する事ができる。また、ミキシング後のバンドパスフィルタの中心周波数や、上記正弦波信号を発生させる演算処理、あるいは出力部のセレクタを変化させる事で、基準クロックの周波数を変更する事無く周波数切り換えを行うので、高速な周波数切り換えを実現する事ができる。周波数生成に用いる正弦波信号はデジタル的な演算によって生成されるので、周波数制御を精度良く行う事ができる。

(もっと読む)

ループフィルタ部品を低減するために二重経路およびデュアルバラクタを用いるタイプII位相ロックループ

フィルタ内のオンチップ部品サイズを低減するデュアルチャージポンプおよび対応する二重信号経路を有し、低減されたループフィルタ部品を備えた位相ロックループ(PLL)。二重経路は、電圧制御発振器内のデュアルバラクタを介して有利に結合され、ループフィルタ部品をさらに低減する。PLLは、二重経路構成を加算するために通常用いられる回路によってもたらされるノイズの欠点をなくす。  (もっと読む)

(もっと読む)

多重周波数源システム及び動作方法

多重周波数源システムが、既定の目標周波数に同調可能な少なくとも1つの周波数源と、目標周波数より高い、又は低い周波数の第2の信号を生成するように動作する少なくとも1つの追加周波数源を含む。同調可能周波数源を、第2の信号の同時生成の間に目標周波数に同調させる方法は、(i)第2の信号の周波数が目標周波数より高いときに、同調可能周波数源を、目標周波数より低い少なくとも1つの周波数点周波数に同調するように制御し、その後、発振器を目標周波数に同調するように制御すること、又は(ii)第2の信号の周波数が目標周波数より低いときに、同調可能周波数源を、目標周波数より高い少なくとも1つの周波数点に同調するように制御し、その後、同調可能周波数源を、目標周波数に同調するように制御することを含む。 (もっと読む)

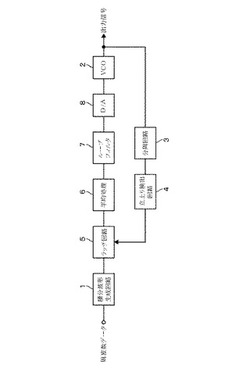

PLL回路

【課題】ダイオードを回路に並列に接続したLPFにおいて、LPFに供給するVCOの自走周波数制御電圧供給手段の出力電圧を2段階に分けて異なる電圧を供給することにより、ダイオードの順方向電圧の影響をキャンセルし、更にLPFの応答速度を改善したPLL回路を提供する。

【解決手段】PLL回路100は、位相同期用制御電圧v及び制御電圧Voに基づいて発振周波数fが制御されるVCO1と、発振信号の周波数fを所定の分周比により分周する分周器2bと、分周された信号と基準周波数信号Fの位相とを比較する位相比較器2cと、この位相誤差εを積分するループフィルタ4と、VCO1の自走周波数を決定するための制御電圧Viを供給する自走周波数制御電圧供給手段5と、この自走周波数制御電圧供給手段5の制御電圧Viに含まれるノイズを除去するLPF6と、PLL−IC2及び自走周波数制御電圧供給手段5を制御するCPU7と、を備える。

(もっと読む)

1 - 12 / 12

[ Back to top ]