Fターム[5J500AC16]の内容

Fターム[5J500AC16]の下位に属するFターム

寄生トランジスタによるもの (1)

寄生容量によるもの (31)

Fターム[5J500AC16]に分類される特許

1 - 19 / 19

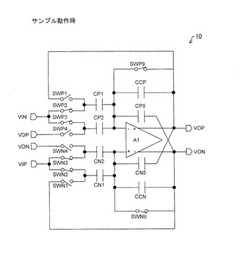

増幅回路およびA/D変換器

【課題】最小限の構成を用いて、演算増幅器の入出力端子間の寄生容量に起因する増幅回路の演算誤差を補償し、高精度の増幅率を得る。

【解決手段】増幅回路10は、一方の端子が演算増幅器A1の反転入力端子に、他方の端子が演算増幅器A1の反転出力端子に接続された容量CP5と、一方の端子が演算増幅器A1の非反転入力端子に、他方の端子が演算増幅器A1の非反転出力端子に接続された容量CN5とを備えている。

(もっと読む)

トランスインピーダンス増幅器、集積回路、及び、システム

【課題】複数の帰還抵抗、及び、入力ノードの配線長による寄生容量を増加させ得る。

【解決手段】集積回路は、第1のトランスインピーダンス増幅器、第2のトランスインピーダンス増幅器を備えている。この集積回路では、第1のトランスインピーダンス増幅器及び第2のトランスインピーダンス増幅器の一方が動作状態となり、他方が非動作状態となる。第1のトランスインピーダンス増幅器及び第2のトランスインピーダンス増幅器は入力トランジスタを共有している。第1のトランスインピーダンス増幅器は、その帰還ノードと入力トランジスタに接続する入力ノードとの間に設けられた第1の抵抗を有している。第2のトランスインピーダンス増幅器は、その帰還ノードと第1の抵抗との間に設けられた第2の抵抗を有している。第2のトランスインピーダンス増幅器の帰還抵抗は、第1の抵抗と第2の抵抗の直列接続により構成されている。

(もっと読む)

増幅回路

【課題】無視することが出来ない寄生容量や寄生インダクタンスを有するトランジスタを用いながら、4次以上の次数に亘ってF級または逆F級の負荷条件を満たす増幅回路を提供する。

【解決手段】トランジスタの後段に、n段(n=1、2、3、…)の梯子型回路を有する高調波処理回路を設ける。高調波処理回路の後段に、それぞれの共振周波数が互いに異なる2n+1個の共振器を有する共振回路部を設ける。2n+1個の共振器の共振周波数を、高調波処理回路の出力部を短絡した場合にトランジスタのドレーン出力部および接地面との間に形成されるn+1個の極およびn個の零点の周波数にそれぞれ一致させる。2n+1個の共振器のうち、2n個の共振器の共振周波数を、2次から2n+1次の高調波の周波数にそれぞれ一致させる。

(もっと読む)

差動分布回路

【課題】接続線路のようなレイアウト寄生成分による帯域劣化を抑制する。

【解決手段】差動分布回路は、入力コプレナー線路CPW1P,CPW1Nおよび出力コプレナー線路CPW2P,CPW2Nに沿って配置された複数の差動増幅器とを備える。各差動増幅器は、電流源ISと、トランジスタQ1Pを含む差動半回路DPと、トランジスタQ1Nを含む差動半回路DNと、一端がトランジスタQ1Pのエミッタに接続され、他端が電流源ISに接続された接続線路ME1Pと、一端がトランジスタQ1Nのエミッタに接続され、他端が電流源ISに接続された接続線路ME1Nとから構成される。接続線路ME1P,ME1Nは、キャパシタンス成分がインダクタンス成分よりも大きい線路である。

(もっと読む)

差動分布回路ICパッケージ

【課題】回路性能の劣化に繋がる先鋭度の高い利得ピークを抑圧する。

【解決手段】差動分布回路ICチップ102は、バイアス電圧端子VCC_CP,VCC_CNからバイアス電圧VCCが供給され、出力端がチップの出力端子DOUTP,DOUTNに接続された出力コプレナー線路CPW2P,CPW2Nと、入力端子DINP,DINNから差動信号が入力され、出力が出力コプレナー線路CPW2P,CPW2Nに接続された差動増幅器CMLとを有する。パッケージ103aは、バイアス電圧端子VCC_CP,VCC_CNにバイアス電圧VCCを供給するボンディングワイヤ110a,111a,204,205に対して直列に挿入された抵抗R5P,R5Nを有する。

(もっと読む)

増幅回路及びこれを備える光ピックアップ

【課題】増幅回路の応答速度等を改善する。

【解決手段】増幅回路1は、差動増幅回路20と複数のソースフォロア回路30、複数の位相補償ブロック300、複数の帰還回路40を含む。差動増幅回路20は、入力信号と基準信号が入力されるNチャンネルMOSトランジスタ23、24を備え、スイッチ18−1−3、18−2−3により差動出力電流を取り出すべき接続点(P1、P2)を選択する。複数の帰還回路40は、スイッチ18−1−1、18−1−2により選択される。スイッチ18−1−1、18−2−1、18−1−2、18−2−2は互いに連動する。スイッチ18−1−1がオンのときには、帰還回路40−1、接続点P1、位相補償ブロック300−1、ソースフォロア回路30−1がまとめて選択される。

(もっと読む)

増幅回路及びこれを備える光ピックアップ

【課題】帰還回路内のスイッチを用いずに電圧増幅度を切り替え可能な増幅回路を提供する。

【解決手段】本発明による増幅回路3bは、差動入力部81A及び81Bと、該差動入力部81A及び81Bのうちのいずれか一方を選択するスイッチ79A及び79Bと、を備え、該スイッチ79A及び79Bにより選択された差動入力部を用いた増幅処理を行うオペアンプ70bと、オペアンプ70bの出力端と差動入力部81Aの入力端との間に設けられ、所定抵抗値の抵抗を有する第1の帰還回路と、オペアンプ70bの出力端と差動入力部81Bの入力端との間に設けられ、上記所定抵抗値とは異なる抵抗値の抵抗を有する第2の帰還回路と、を備えることを特徴とする。差動入力部の選択により電圧増幅度を切り替え可能であるので、帰還回路内のスイッチを用いずに電圧増幅度を切り替え可能となっている。

(もっと読む)

光受信回路および光結合装置

【課題】広いダイナミックレンジを有する光受信回路および光結合装置を提供する。

【解決手段】入力光11に応じて電流Ipを出力する受光素子12と、入力端子13aに受光素子12が接続された反転増幅器13と、トランスインピーダンスが低周波数側で小さくなり、且つ高周波数側で大きくなる周波数特性を有し、反転増幅器13の出力電圧Voを入力端子13aに帰還する帰還回路14とを具備する。帰還回路14が、反転増幅器13の入力端子13aと出力端子13bとの間に直列接続された第1抵抗R1および第2抵抗R2と、第1抵抗R1と第2抵抗R2との接続点14aと接地電位線GNDとの間に直列接続された第3抵抗R3およびキャパシタCとを具備する。

(もっと読む)

LD差動駆動回路

【課題】レーザダイオードに流れる電流のジッタを低減する。

【解決手段】LD駆動電流が出力する差動形式の出力端子OUT1,OUT2およびLDバイアス電流が出力するLDバイアス端子BBを有するLDドライブ回路10と、レーザダイオードLDの一方の端子と出力端子OUT1との間に接続されるの伝送線路T1と、レーザダイオードLDの他方の端子と出力端子OUT2との間に接続されるの伝送線路T2と、レーザダイオードLDの一方の端子とLD電源端子VCC2との間に接続されるバイアス用インダクタL1と、レーザダイオードLDの他方の端子とLDバイアス端子BBとの間に接続されるバイアス抵抗R6とを有する。

(もっと読む)

リンギング低減回路および該リンギング低減回路を備えた半導体集積回路

【課題】 動作速度を犠牲にせず、半導体集積回路の出力信号のリンギングを低減する。

【解決手段】 リンギング低減回路40NAは、出力信号線120および低電位電源線112間のNチャネルトランジスタ401と、コンパレータ410とを有する。コンパレータ410は、出力信号OUTを高電位電源線111のレベルPVDDIと比較し、出力信号OUTがレベルPVDDIを越えるオーバシュートが発生しているとき、Nチャネルトランジスタ401をON状態とし、オーバシュートを低減する。リンギング低減回路40PAは、同様の原理により、出力信号OUTのアンダシュートを低減する。

(もっと読む)

接続部に結合された電極を有する素子を備える装置

接続部(11,12)に結合された電極を有する素子(5)を備え、一つ以上の接続部(11,12)がインピーダンス送信ネットワークの一部を形成する装置(1)において、接続部(11,12)の最大部分が非平行面に配されることにより、接続部(11,12)の間の電磁結合が低減される。これにより、さらに、不要なフィードバック及び素子(5)の送信特性の悪化が低減され、さらに、各素子(5)の別個の電極が互いにより近接して配置されてサイズが小さくなる。接続部(11,12)の最大部分は、それぞれの他の平面の一部を形成せず、同一平面の一部を形成しない。これら平面は45度と135度との間の角度をなす。一つの接続部(11,12)がループ等の形状を有し、さらに電磁結合を低減する。インピーダンス送信ネットワークの一部を形成する一つ以上の接続部(11,12)がインダクタンスを備え、一つ以上の接続部(11,12)が素子内部容量(13,14)に結合される。  (もっと読む)

(もっと読む)

差動増幅回路

【課題】 出力電圧の反転を防止するとともに、入力電圧範囲を広くすることができる差動増幅回路を提供する。

【解決手段】 第1の入力信号をベースに入力する第1のトランジスタと、第2の入力信号をベースに入力する第2のトランジスタと、第1の電源電位に接続し、第1および第2のトランジスタに電流を供給する電流源とからなる差動回路と、第1のトランジスタのコレクタにエミッタを、第2電源電位にベースを接続した第3のトランジスタと、第3のトランジスタのコレクタと第2電源電位との間に接続した第1の負荷と、第2のトランジスタのコレクタと第2電源電位との間に接続した第2の負荷と、第3のトランジスタのコレクタに接続した第1の出力端子とで構成する。

(もっと読む)

カレントミラー回路および定電流回路

【課題】 トランジスタの共通のベースラインと電源線との間に抵抗が接続されている場合でも高精度のミラー比を得る。

【解決手段】 カレントミラー回路18において、抵抗R5はノイズ耐量を上げるとともにトランジスタQ10、Q11の漏れ電流を防止するために必要であり、トランジスタQ12のコレクタ電流は、抵抗R5に流れる電流が支配的となる。トランジスタQ12のベース電流IB(Q12)を、トランジスタQ14のベース電流IB(Q14)により補償する。抵抗R5に流れる電流とトランジスタQ11、Q13〜Q15に流れる電流とが等しい場合にほぼ完全に補償でき、ミラー比はより正確に1に近付く。

(もっと読む)

差動増幅回路

【課題】 SOI基板上に形成された差動増幅回路において、ソースタイ型のトランジスタの基板効果による、動作開始時の誤動作を防止する。

【解決手段】 入力信号INP,INMが与えられる増幅部10のソースタイ型のNMOS11a,11bのドレインと、負荷用のPMOS14a,14bが接続されるノードN3,N2との間に、アクティブ時にオンになり、スタンバイ時にオフとなるNMOS15a,15bを挿入する。スタンバイ時には、ノードN1と接地電位GNDとの間の定電流用のNMOS12もオフになるので、NMOS11a,11bは完全にフローティング状態となり、ボディの電位はスタンバイ状態になる直前のアクティブ時の状態に維持される。従って、再びアクティブ状態になった時に、ソースとボディの電位差が生じないので、基板効果による影響を防止することができる。

(もっと読む)

増幅器および無線通信装置

【課題】寄生抵抗の影響で、歪み補償回路の減衰特性が電力増幅器の歪み特性と異なってしまう場合においても、電力増幅器の出力信号の歪みを低減することが可能な増幅器およびその増幅器を搭載した無線通信装置を提供することを目的とする。

【解決手段】本発明にかかる増幅器は、半導体トランジスタを含み、入力信号の電力を増幅する電力増幅器33と、電力増幅器33の入力側に設けられ、入力信号レベルの増加に伴って減衰量が減少する特性を有し、電力増幅器33の出力信号の歪みを補償する歪み補償回路32と、電力増幅器33の利得抑圧特性と歪み補償回路32の減衰特性との傾きのズレを解消すべく、電力増幅器33の利得抑圧特性を調整する利得抑圧調整回路34とを備えている。

(もっと読む)

高出力差動増幅器

【課題】小型で利得が高く、高い出力が得られる高出力差動増幅器を得る。

【解決手段】基本トランジスタセルをN段(Nは2以上の整数)並列接続してなる第1の増幅器11および第2の増幅器12を有し、第1の増幅器11のエミッタ端子および第2の増幅器12のエミッタ端子を互いに接続して仮想接地点6を設け、第1の増幅器11のベース端子および第2の増幅器12のベース端子にそれぞれ逆位相となる信号を入力することにより、第1の増幅器11のコレクタ端子および第2の増幅器12のコレクタ端子から増幅された信号を出力する高出力差動増幅器において、第1の増幅器11および第2の増幅器12の対応する段の基本トランジスタセルのエミッタ電極同士を接続して1対ごとの仮想接地点6a〜6fを設け、1対ごとの仮想接地点6a〜6fを互いに接続したものである。

(もっと読む)

バッファ回路および半導体装置

【課題】 内部回路から出力される信号の駆動能力を高め、外部負荷に出力するバッファ回路において、容易にリンギングを抑制する。

【解決手段】 出力バッファ60は、入力される信号の駆動能力を可変し、外部負荷90に出力する。電圧モニタ回路70は、出力バッファ60から出力される信号を駆動能力制御回路50にフィードバックする。駆動能力制御回路50は、電圧モニタ回路70から出力される信号に応じて、出力バッファ60の駆動能力を制御する。これにより、外部負荷90に出力する信号の状態に応じて、信号の駆動能力が制御されるので、回路上の伝送線路負荷定数の変更や、回路を構成している半導体装置の変更等、回路条件を変更することなく、容易にリンギングを抑制することができる。

(もっと読む)

高周波増幅回路

【課題】出力端子におけるVSWRを劣化させることなく、しかも、歪特性や効率の変化を招くことなく回路の安定性向上を図る。

【解決手段】第1乃至第3のトランジスタ11〜13は、それぞれエミッタ接地増幅回路を形成し、第1及び第2の段間整合回路5,6を介して縦続接続されると共に、それぞれのエミッタは、第1乃至第3の寄生インピーダンス14a〜14cを介してグランドに接続される一方、第1のトランジスタ11のエミッタと第3のトランジスタ13のエミッタがインピーダンス素子15を介して接続されて高周波増幅回路が構成されており、これによって、VSWR特性劣化、歪特性や効率の変化を伴うことなく、回路安定性が確保されたものとなっている。

(もっと読む)

安定化回路網を有する電力増幅器

増幅器が振動する(oscillate)のを防止するために、安定化回路(530)が、電力増幅器トランジスタ(502)の出力に接続される。この安定化回路(530)は、基本的に、コンデンサ(534)と直列に接続された抵抗器(536)を含む。また、この安定化回路は、コンデンサと抵抗器とに直列に接続されたインダクタ(532)を含んでもよい。このインダクタは、プリント導電線及び/又はボンディング・ワイヤによって部分的に、又は完全に実現されることができる。この安定化回路は、動作周波数の範囲全体にわたって、トランジスタ出力において低インピーダンスをもたらす。  (もっと読む)

(もっと読む)

1 - 19 / 19

[ Back to top ]