Fターム[5J500AC63]の内容

Fターム[5J500AC63]に分類される特許

1 - 11 / 11

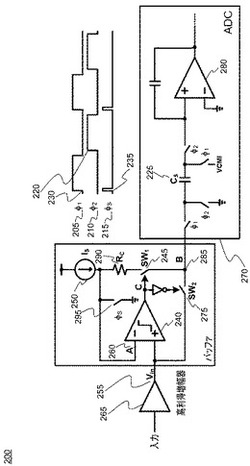

抵抗の誤差訂正を用いるコンパレータベースのバッファ

【課題】スイッチトキャパシタの負荷を有する高利得増幅器の駆動容量を高めるコンパレータベースのバッファ方法及びシステムを提供することを目的とする。

【解決手段】電流源と、コンパレータと、スイッチと、サンプリングキャパシタと、オーバーシュート訂正抵抗を含む。充電経路内の抵抗及び訂正位相を使用する訂正の解決法は、電力消費を制約し、コンポーネントを最小化する一方で、出力電圧のオーバーシュートを低減する。Spectre(登録商標)シミュレーションは、本発明の効果を確証する。

(もっと読む)

ピーキング回路及びピーキング調整方法並びにピーキング回路を備えた差動増幅器及びレーザダイオード駆動回路及び情報処理装置

【課題】

高周波信号を取り扱う回路の高周波領域での周波数特性が劣化することをより少ない消費電力で防止するピーキング調整回路を提供する。

【解決手段】

高周波信号のピーキングを調整するピーキング回路を、第1のコンダクタと、第1のインダクタとカップリングする第2のインダクタと、入力信号を受ける信号入力部と、信号入力部から入力された入力信号に応じて第2のインダクタに流れる電流を調整するトランジスタと、第1のインダクタでピーキングを調整された信号を出力する信号出力部とを備えて構成し、信号入力部から入力された入力信号に応じてトランジスタで第2のインダクタに流れる電流を制御して第2のインダクタとカップリングしている第1のインダクタとの相互インダクタンスを変化させることにより第1のインダクタを流れる電流の信号波形のピーキングを調整し、ピーキングを調整した信号を信号出力部から出力するようにした。

(もっと読む)

高周波増幅回路

【課題】高周波増幅回路において、LC共振を用いずにピーキングをかけること。

【解決手段】高周波増幅回路は、1段目にトランジスタTr1を用いたエミッタ接地増幅回路、2段目にダーリントン接続のトランジスタTr2、Tr3を用いたエミッタ接地回路の2段増幅の構成となっている。トランジスタTr1のエミッタとトランジスタTr2のコレクタとの間には容量素子が挿入されている。容量素子は、ダイオード接続のトランジスタTr4であり、トランジスタTr4のエミッタはトランジスタTr2のコレクタに、トランジスタTr4のベースおよびコレクタはトランジスタTr1のエミッタに接続されている。ダイオード接続のトランジスタTr4によって位相をずらしてフィードバックすることにより、高域での利得を向上させることができる。

(もっと読む)

ピーキング回路、ピーキング回路制御方法、波形測定装置、情報処理装置

【課題】ピーキング量を変化させるときに低周波域の増幅度に与える影響を抑えたピーキング技術を提供する。

【解決手段】本発明に係るピーキング回路は、多段接続された増幅回路と、入力側から見た増幅度が異なる2以上の出力点から入力側へフィードバックするフィードバック回路とを備え、フィードバック回路のフィードバック量を変化させることができるように構成されている。

(もっと読む)

低周波透過回路、通信回路、通信方法、通信回路のレイアウト方法

【課題】透過周波数域における利得が一定かつ遮断周波数域への遷移における利得変化が急峻であって、かつ、帯域外抑圧比の大きい低周波透過回路を提供すること。

【解決手段】本発明の一態様は、インダクタ素子を有する低周波透過フィルタ101と、低周波透過フィルタ101に縦続接続され、低周波透過フィルタ101が透過から遮断へ遷移する周波数近傍かつ透過周波数域内に利得の盛り上がりを有する増幅器100と、を備える低周波透過回路である。

(もっと読む)

アクティブインダクタおよび差動アンプ回路

【課題】低電源電圧下においても、半導体集積回路上での面積および消費電力の増大を抑えつつ、高域での利得のピーキングの傾きを急峻化する。

【解決手段】P型電界効果トランジスタM1のソースを電源電位VDDに接続し、P型電界効果トランジスタM1のドレインを出力端子outに接続し、N型電界効果トランジスタM2のドレインを電源電位VDDに接続し、N型電界効果トランジスタM2のソースを電流源IBを介して接地電位に接続し、P型電界効果トランジスタM1のゲートをN型電界効果トランジスタM2のソースに接続し、N型電界効果トランジスタM2のゲートを抵抗素子Rpを介してP型電界効果トランジスタM1のドレインに接続する。

(もっと読む)

差動アンプ回路

【課題】インダクタンスを外部から簡単に調整することができる差動アンプ回路を得る。

【解決手段】差動対を構成する第1及び第2のトランジスタと、第1のトランジスタの出力端子と電源との間に接続された第1のインダクタと、第2のトランジスタの出力端子と電源との間に接続された第2のインダクタと、第1のインダクタにシリアル接続された第1のトランスミッションゲートと、第2のインダクタにシリアル接続された第2のトランスミッションゲートとを有する。

(もっと読む)

論理回路

【課題】ラッチ回路を一例とする各種論理回路の高速化を実現する。

【解決手段】例えば、クロック信号CKが‘H’レベルの際に差動アンプ構成でデータ入力信号Dinの取り込みを行うデータ取り込み部BFと、CKが‘L’レベルの際にBFからのデータ出力信号Doutをラッチするラッチ部LTからなる構成に対し、ゲイン制御部GCTLとコモンノード制御部CMNCTLを設ける。GCTLは、差動アンプ内のNMOSトランジスタMN1,MN2のコモンノードCOMN1,COMN2間に設けられ、差動アンプのゲインを低周波数帯よりも高周波数帯で高くする機能を備える。CMNCTLは、CKが‘L’レベルの際に、COMN1,COMN2の電位差を無くすように電荷を制御する機能を備える。これによって、Doutの遷移時間が早くなり、LTでのセットアップマージンが拡大できる。

(もっと読む)

増幅回路およびトランスインピーダンスアンプ

【課題】光受信回路に用いる可変利得型の増幅器に関し、利得を切り替えた場合でも過剰ピーキングのない平坦な周波数特性を得ることができるようにする。

【解決手段】増幅信号Sが出力されるエミッタ接地回路1Aの出力端子OUTaに電流源回路3を接続して、エミッタ接地回路1Aの入力段トランジスタへ供給されるバイアス電流を電流源回路3へ分流し、この際、利得切替回路20で選択された増幅回路10Aの利得に応じて分流する電流の大きさを調整する。

(もっと読む)

トランジスタ回路

【課題】 トランジスタの熱暴走を防止すると共に、ベースバラスト抵抗による所望周波数成分の電力利得の低下を抑制しつつ、不要な高調波成分や帯域外信号成分の電力利得を大幅に低減させることができるトランジスタ回路を提供する。

【解決手段】 トランジスタ回路1は、トランジスタ11、ベースバラスト抵抗12、容量13及びインダクタ14で構成される複数のトランジスタセル10からなる。トランジスタ11のコレクタ及びエミッタは、それぞれトランジスタ回路1のコレクタ端子1c及びエミッタ端子1eに共通接続される。ベースバラスト抵抗12は、一方端がトランジスタ11のベースに、他方端がトランジスタ回路1のベース端子1bに接続される。容量13とインダクタ14とは、直列接続されて直列共振回路15を形成し、ベースバラスト抵抗12と並列に、トランジスタ11のベースとトランジスタ回路1のベース端子1bとの間に接続される。

(もっと読む)

増幅回路

【課題】 アクティブフィードバック回路のピーキング強度を外部から調整することができる増幅回路を得る。

【解決手段】 第1の差動増幅回路と、第1の差動増幅回路の出力信号を増幅する第2の差動増幅回路と、第2の差動増幅回路の出力信号をフィードバックして第1の差動増幅回路の出力信号を波形整形するアクティブフィードバック回路とを有し、アクティブフィードバック回路は、コレクタ又はドレインがそれぞれ第1の差動増幅回路の2つの出力ノードに接続され、ベース又はゲートがそれぞれ第2の差動増幅回路の2つの出力ノードに接続され、エミッタ又はソースが共通接続された第1及び第2のトランジスタと、一端が第1及び第2のトランジスタのエミッタ又はソースに接続され、他端が低電位側電源に接続された、電流値を外部から調整することができる第1の電流源とを有する。

(もっと読む)

1 - 11 / 11

[ Back to top ]