Fターム[5J500AH37]の内容

増幅器一般 (93,357) | 回路素子 (16,323) | コイル(インダクタンス) (1,435) | トランス (212) | 中間タップ付トランス (16)

Fターム[5J500AH37]に分類される特許

1 - 16 / 16

電力増幅回路、および無線通信装置

【課題】回路面積を縮小しつつ、電力効率の向上を図ることが可能な電力増幅回路を提供する。

【解決手段】電力増幅回路は、シリコン基板上に集積された電力増幅回路である。電力増幅回路は、入力が第1の信号入力端子に接続された第1のアンプを備える。電力増幅回路は、入力が第2の信号入力端子に接続された第2のアンプを備える。電力増幅回路は、入力が前記第1のアンプの出力に接続され、出力が前記第2のアンプの出力に接続されたアンプ出力移相器を備える。電力増幅回路は、一端が電源に接続され、他端が前記アンプ出力移相器の出力に接続された一次側巻線と、一端が第1の信号出力端子に接続され、他端が第2の信号出力端子に接続された二次側巻線と、を有するトランスフォーマと、を備える。

(もっと読む)

電力増幅回路

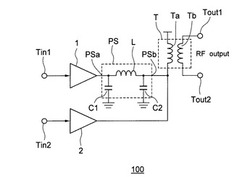

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

増幅回路

【課題】高出力時と低出力時の間で利得の変化や通過位相の変化が少ないもしくは抑制された増幅回路を提供する。

【解決手段】電力分配回路は,入力信号の電圧を複数の電圧に分配する電圧分配回路と,入力信号の電流を複数の電流に分配する電流分配回路とを縦続接続し,前段の電圧または電流分配回路に分配前入力信号を入力し,後段の電流または電圧分配回路が分配入力信号を出力する。電力合成回路は,電圧合成回路と,電流合成回路とをいずれかを前段にして縦続接続し,前段の電流または電圧合成回路に分配出力信号を入力し,後段の電圧または電流合成回路が合成後出力信号を出力する。さらに,電圧分配数Mと電流分配数Nの比M/Nと,電圧合成数Kと電流合成数Lの比K/Lとを一定に維持しながら,分配数M,Nと合成数K,Lとを変化させると共に,信号が分配される増幅器を動作状態に分配されない増幅器を非動作状態に制御する制御回路を有する増幅回路。

(もっと読む)

増幅器及び無線機器

【課題】増幅器の入出力特性の直線性が悪化することを防ぐこと。

【解決手段】一対のFET素子Q1,Q2の出力側の各々の間に1次側の両端が接続され、2次側の両端よりFET素子Q1,Q2から出力される信号を降圧した降圧信号を出力する帰還用トランスL3と、FET素子Q1,Q2の入力側の各々と、FET素子Q1,Q2の入力側の位相と同相となる降圧信号を出力する帰還用トランスL3の2次側の各々との間に、FET素子Q1,Q2の入力側に向かって整流する方向に接続された整流用ダイオードD1,D2と、整流用ダイオードD1,D2を介してFET素子Q1,Q2の入力側にバイアス電圧またはバイアス電流を供給するバイアス回路と、を備える。

(もっと読む)

入力信号の電力増幅用回路及びそのような回路を組み込んでいる信号発信システム

【課題】 入力信号の電力増幅用回路及びそのような回路を組み込んでいる信号発信システムを提供する。

【解決手段】 本発明は、入力段(EE)及び出力段(ES)を含む入力信号の電力増幅用回路(CIR)に関し、前記入力段(EE)は:

―いわゆる主駆動トランジスタ(T3)を組み込んでいる駆動手段(MP)と、

―入力信号を受信可能で、主駆動トランジスタ(T3)と共に電流ミラーとして組み立てられた、第1のいわゆる主入力トランジスタ(T1)とを備える。

第1の主入力トランジスタ(T1)は、入力段(EE)内へ組み込まれた第2のいわゆる主入力トランジスタ(T2)を介して出力段(ES)に連結され、かつ駆動手段(MP)によって制御され、第1の主入力トランジスタ(T1)と第2の主入力トランジスタ(T2)は相互に連結され、かつ共振回路(BB2,Cp)を経由してDarlington型の構造に従ってアースに連結される。

(もっと読む)

E/F級スイッチング電力増幅器

【課題】E級と逆F級のハイブリッド回路を用いて高効率な電力増幅器を提供する。

【解決手段】「E/F級増幅器」と呼ばれる、新たな分類のスイッチング増幅器は、選択された調波でF-1級のインピーダンスと、それら以外の調波でE級のインピーダンスを配備することによって、電圧と電流の改良された波形のための負荷ネットワークと共に、ゼロ電圧スイッチング(ZVS)位相補正技術を用いて、E級増幅器で利用されるスイッチングデバイスの固有キャパシタンスに通常関連した損失を取り除く。

(もっと読む)

D級増幅装置

【課題】 高速且つ均一なスイッチングを実現し、装置の小型化を図ることができるD級増幅装置を提供する。

【解決手段】 トランジスタQ10,Q11のオン/オフによって1次側中点を中心にプッシュプル動作を行うパルストランス24と、それによりスイッチングを行うパワートランジスタQ12,Q13と、プッシュプル動作の時間分、搬送波信号の出力タイミングを調整するタイミング調整手段30と、音声信号が入力されている場合に、タイミング調整手段30からの搬送波信号について逆位相の信号を生成する反転回路35及びAND回路37と、AND回路37から出力された、タイミング調整手段30からの搬送波信号に逆位相の矩形波でオン/オフするトランジスタQ14と、タイミング調整手段30からの搬送波信号に同位相の矩形波でオン/オフするトランジスタQ15とを備える。

(もっと読む)

オーディオ電力増幅器

【課題】従来のA級電力増幅器では、消費電力が大きいという問題があった。

【解決手段】A級電力増幅器の一つの形態である差動プッシュプル電力増幅器の、電源ノイズを出力しないという性質を利用して、出力信号電圧の絶対値の高低に応じて電源電圧を変えることにより、音楽再生時間の大部分を占める無信号あるいは低レベル再生時の消費電力を大幅に低く抑えることができる。

(もっと読む)

オーディオパワーアンプ

【課題】 従来よりも小型かつ軽量であり、しかも様々な使用条件に柔軟に対応することができるハイ・インピーダンス方式のパワーアンプを提供する。

【解決手段】 多チャンネルモードが選択されると、入力側のリレー16は、第2チャンネルCH2用の増幅回路12aの入力側を第2チャンネルCH2用の入力端子14aと接続するように切り換わる。併せて、出力側のリレー42は、OFFする。これにより、第1チャンネルCH1と第2チャンネルCH2とを有する多チャンネルアンプが形成される。一方、大出力モードが選択されると、入力側リレー16は、第2チャンネルCH2用の増幅回路12aの入力側を第1チャンネルCH1用の入力端子14と接続するように切り換わる。併せて、出力側リレー42はONする。これにより、合成チャンネルCH0のみの単一チャンネルながらも60[W]の定格出力を有する大出力アンプが形成される。

(もっと読む)

増幅装置

【課題】増幅回路を構成する素子であるトランジスタがASO破壊を起こさず、トランジスタを完全動作領域内で動作させることができる増幅装置を提供する。

【解決手段】入力信号を増幅するトランジスタ6と、このトランジスタに電圧を供給する電圧源4、5と、このトランジスタに流れるコレクタ電流を検出する電流検出部7と、電流検出部が検出したコレクタ電流の電流値に応じて、電圧源がそのトランジスタに供給する電圧を調整する電圧調整部8とを備える。

(もっと読む)

広帯域インピーダンスおよびノイズ整合を備えた周波数選択性増幅器

【解決手段】 この開示は、広帯域インピーダンスおよびノイズ整合を備えた周波数選択低ノイズ増幅器(LNA)に向けられている。本LNAは、広帯域の入力整合をサポートする閉ループ回路を含み得る。例えば、閉ループ回路は入力信号をインピーダンス整合するとともに低ノイズ指数をもたらすように構成され得る。また、LNAは、入力信号を増幅し、高い出力インピーダンスをもたらす開ループ回路を含み得る。開ループ回路は、所望の周波数帯の外側の周波数を濾波により除去する選択性フィルタをさらに含み得る。LNAは、開ループ回路によって調整可能な帯域通過フィルタを駆動し得る。 (もっと読む)

D級増幅装置

【課題】 従来は、高速スイッチングを実現するために、ハイパワーFETと同等の耐圧を備えた大型のFETをハイパワーFETのソース側に設けており、装置の小型化の妨げとなり、また、スイッチングの精度が悪化するという問題点があり、高精度の高速スイッチングを実現し、装置の小型化を図ることができるD級増幅装置を提供する。

【解決手段】 互いに逆相のタイミングでスイッチングを行うハイパワートランジスタQ10とQ12のゲート側に、音声信号によって増幅器出力のオン/オフを制御する小電力用のトランジスタQ14を備え、トランスのGND側に音声信号によってオン/オフし、電荷を高速に抜く小電力用のトランジスタQ15、Q16を備えたD級増幅器を、ビッグステップPA及びバイナリーステップPAとして複数設けたD級増幅装置である。

(もっと読む)

サーキュレータタイプのモノリシック装置

【解決手段】本発明は、高周波信号を送受信するためにアンテナ(2) に接続されることが意図され、サーキュレータの出力(S) に信号を供給することが可能なデュアル−インプット差動増幅器(31)と、第1、第2及び第3アクセス端子を夫々含む2つの3dB カプラー(A,B) とを備えたモノリシックサーキュレータに関し、第2端子はサーキュレータの1つの入力(E) に接続され、第3端子は増幅器の1つの入力に夫々接続され、第1端子は、アンテナとアンテナのインピーダンスに近いインピーダンスを有する負荷要素(30)とに夫々接続されることが意図されている。  (もっと読む)

(もっと読む)

電力変換装置

【課題】電力変換装置の回路構成を簡素化し且つ電力変換効率を向上する。

【解決手段】本発明による電力変換装置は、直流電源(1)に直列に接続された2つの主MOS-FET(4,5)と、2つの主MOS-FET(4,5)に並列に接続された2つのコンデンサ(3a,3b)とを有する発振回路(2)と、各主MOS-FET(4,5)の接続点と各コンデンサ(3a,3b)の接続点との間に接続されたトランス(9)の1次巻線(9a)と、トランス(9)の2次巻線(9b,9c)の一端及び他端とスピーカ(15,40)との間にそれぞれ接続された第1の制御用MOS-FET(10,35)と第2の制御用MOS-FET(11,36)との電力制御回路(12,37)と、各主MOS-FET(4,5)のオン・オフにより2次巻線(9b,9c)に発生する交流電圧の極性を検出する極性検出回路(51)と、極性検出回路(51)の検出信号により第1及び第2の制御用MOS-FET(10,11;35,36)をオン・オフ制御する駆動回路(24,25;49,50)とを備える。

(もっと読む)

デジタルスイッチングアンプ

【課題】 高精度に増幅された復調信号を生成するためのパルス信号を出力可能で、しかも、簡単な回路構成、かつ、ノイズの少ないデジタルスイッチングアンプを実現する。

【解決手段】 スイッチング回路4は、電源回路3からの電源電圧Vhをスイッチングして、パルス信号Soを生成している。減衰器6は、パルス信号Soを所定の減衰率で減衰して帰還信号Sfを生成する。デルタシグマ変調回路2およびドライバ回路5は、帰還信号Sfと入力信号Siとに基づいて、上記スイッチング動作を制御する。さらに、電源回路3には、無入力時の帰還信号Sfのレベルが最大入力振幅レベルを超えないように、レギュレーションカーブが設定されたトランス31と、トランス31の出力を整流して直流電圧を生成する整流回路32とが設けられ、当該直流電圧が、電源電圧Vhとして、スイッチング回路4に入力される。

(もっと読む)

ポーラー変調器および信号変調方法

【課題】低い電源電圧に適するとともに所要面積の少ないポーラー変調器を提供する。

【解決手段】ポーラー変調器では、位相同期回路(2)によって位相変調信号から変調されたキャリア信号が生成される。このキャリア信号は、リミッタ増幅器(30)を介して方形波信号に変換され、増幅器(4)へ入力される。同時に、第2入力部(11)の振幅変調信号が、制御可能な電流源(3)の制御入力部(31)に入力される。制御可能な電流源は、制御入力部(31)の振幅変調信号に応じた電流を出力部(32)に出力するように形成されている。制御可能な電流源(3)の出力部(32)は、増幅器(4)の電流入力部(43)と接続されている。その結果、増幅器(4)の電源電流は、伝送される振幅情報に応じて変調される。電流ドメインの範囲の振幅情報の処理によって、本発明のポーラー変調器をCMOS技術で集積回路として実現できる。

(もっと読む)

1 - 16 / 16

[ Back to top ]