Fターム[5J500AM04]の内容

Fターム[5J500AM04]に分類される特許

1 - 20 / 115

スプリッタ回路およびチューナーシステム

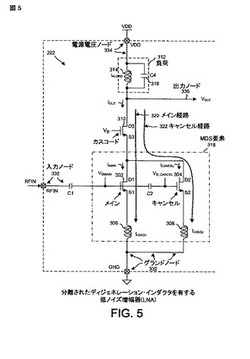

デブースト電流経路を有するマルチ線形性モードLNA

【課題】高線形性と低歪みの増幅器を提供する。

【解決手段】修正された微分重ね合わせ低ノイズ増幅器は、メイン電流経路とキャンセル電流経路を含む。キャンセル経路の三次歪みは、メイン経路の三次歪みをキャンセルするために使用される。新規な一側面では、分離されたソース・ディジェネレーション・インダクタが、2つの電流経路の各々につきあり、これにより他方の電流経路に影響を与えることなく、一方の電流経路の調整を容易にする。第2の新規な側面では、LNA負荷を通過しないデブースト電流経路が設けられる。デブースト電流は、ヘッドルームの問題を生じさせることなく、ネガティブ・フィードバックを増加させる。第3の新規な側面では、キャンセル電流経路及び/またはデブースト電流経路がプログラマブルにディセーブルとされて、高線形性を求めない動作モードにおいて電力消費を低減し、ノイズ量を改善する。

(もっと読む)

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

【課題】差動入力を有する直交出力低雑音トランスコンダクタンス増幅器を提供する。

【解決手段】低雑音トランスコンダクタンス増幅器200は、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部110と、PMOSトランスコンダクタンス部に結合されたPMOSカスコード部130と、RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部120と、NMOSトランスコンダクタンス部に結合されたNMOSカスコード部140と、を含み、PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号gmpq、gmnq及び差動同相出力信号gmpi、gmniを提供する。RF信号を増幅するための方法は、差動RF入力信号を受信することと、差動RF入力信号を電流信号に変換することと、電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供する。

(もっと読む)

レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置

【課題】レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置を提供する。

【解決手段】本願発明は、増幅器であって、入力信号を受け取るための入力ステージと、前記入力ステージに連結されると共に、前記入力信号に応答して出力ドライバステージに対して駆動信号を提供する高利得ステージと、前記出力ドライバステージに連結された出力端子とを具備することを特徴とする。前記出力ドライバステージは、前記高利得ステージから第1の駆動信号“pdrive”を受け取る第1の端子、第1の電圧降下を通じてVDDに連結された第2の端子、及び、前記増幅器の前記出力端子に連結された第3の端子を有する高電位側ドライバ回路を備える。

(もっと読む)

トランスインピーダンスアンプ

【課題】利得周波数特性の広帯域化と群遅延平坦特性とを両立させる。

【解決手段】ソース接地トランジスタM1、ゲート接地トランジスタM2、および負荷抵抗RLからカスコード接続回路11を構成し、ソース接地トランジスタM1のドレイン端子とゲート接地トランジスタM2のソース端子と間に第1のインダクタL1を設ける。

(もっと読む)

半導体装置

【課題】シングルエンド−差動変換器を備えた半導体装置において、理想的な出力差動電流特性が得られる周波数の上限を向上させる。

【解決手段】入力電圧Vinを、パッケージ3の外部電極PIN1に入力し、外部電極PIN1、ボンディングワイヤWire1、チップ2の入力端子PAD1、シングルエンド−差動変換器1の入力端子Tin1を介してゲート接地のMOSトランジスタM1のソースに伝達する。また、外部電極PIN1、ボンディングワイヤWire2、チップ2の入力端子PAD2、シングルエンド−差動変換器1の入力端子Tin2を介してソース接地のMOSトランジスタM2のゲートに伝達する。

(もっと読む)

低雑音増幅器

【課題】低雑音増幅器の周波数帯域を拡大すること。

【解決手段】入力信号がゲートに供給されるソース接地トランジスタと、前記ソース接地トランジスタのドレイン電流が供給される第1の負荷とを有する増幅回路と、前記入力信号がソースに供給されるゲート接地トランジスタと、前記ゲート接地トランジスタのドレイン電流が供給される第2の負荷とを有する終端回路と、前記ゲート接地トランジスタのソースとドレインの間に接続されたアクティブインダクタとを有すること。

(もっと読む)

集積フィルタを備えた増幅器

【課題】良好な雑音性能を有しかつ大きい干渉信号に対処できる増幅器を提供する。

【解決手段】集積フィルタを備えた増幅器320b(例えば,LNA)は利得ステージ330、フィルタ・ステージ340およびバッファ・ステージ350を含んでいてもよい。利得ステージは、入力信号に対して信号増幅を提供する。フィルタ・ステージは、入力信号に対してフィルタリングを提供する。バッファ・ステージは、フィルタ・ステージからのフィルタされた信号をバッファする。増幅器は、第2のフィルタ・ステージ360及び第2のバッファ・ステージ370をさらに含んでいてもよい。

(もっと読む)

全二重伝送回路、及び電子機器

【課題】消費電力を低減すること。

【解決手段】送信信号が入力される第1の内部入力端子と、送信信号に比べて振幅が1/2であり、かつ、送信信号と同相の信号が入力される第2の内部入力端子と、特性インピーダンスZを有する伝送路に接続された外部入出力端子と、外部入出力端子から入力された受信信号が出力される内部出力端子と、ソースが電流源及び外部入出力端子に接続され、ゲートが第1の内部入力端子に接続され、ドレインが第2のMOSトランジスタのソース及び内部出力端子に接続された第1のMOSトランジスタと、ソースが第1のMOSトランジスタのドレイン及び内部出力端子に接続され、ゲートが第2の内部入力端子に接続された第2のMOSトランジスタと、を備え、第1及び第2のMOSトランジスタのトランスコンダクタンスが1/Zとなる、全二重伝送回路が提供される。

(もっと読む)

差動増幅器及びデータドライバ

【課題】従来の差動増幅器は出力誤差が増大する問題がある。

【解決手段】本発明の差動増幅器は、内挿機能を有し、第1導電型トランジスタで形成される第1、第2の差動対(21、22)と、第2導電型トランジスタで形成される第3、第4の差動対(23、24)と、第1、第2の差動対に動作電流を供給する第1、第2の電流源(41、42)と、第3、第4の差動対に動作電流を供給する第3、第4の電流源(43、44)と、第1、第2の差動対にそれぞれ流れる電流量が第1、第2の電流源が出力する動作電流よりも小さくなる第1の動作範囲において、第1の差動対に供給される動作電流の変化点を制御する第1の制御回路51と、第3、第4の差動対にそれぞれ流れる電流量が第3、第4の電流源が出力する動作電流よりも小さくなる第2の動作範囲において、第4の差動対に供給される動作電流の変化点を制御する第2の制御回路52と、を有する。

(もっと読む)

信号増幅回路、電流電圧変換回路、および光受信器

【課題】入力電流の大きさの変化に応じた出力電圧波形の歪みを抑えることができる信号増幅回路、電流電圧変換回路、および光受信器を提供する。

【解決手段】プリアンプ13は、トランジスタ21、及び該トランジスタ21と電源電位線18との間において出力信号を提供するノードAを有し、光電流Iinを受ける信号入力端13aにトランジスタ21のエミッタが接続され、ノードAにトランジスタ21のコレクタが接続されたベース接地回路20と、ノードAに接続され、出力電圧Voutの平均レベルから利得制御信号Vagcを生成する検知回路50と、ベース接地回路20に対して並列に接続されたトランジスタ31を有し、そのベースに利得制御信号Vagcを受ける分流回路30とを備える。検知回路50は、平均レベルの上昇に応じてトランジスタ31を流れる電流が大きくなるように利得制御信号Vagcを生成する。

(もっと読む)

高直線性デジタル可変利得増幅器

【課題】温度と無関係に同一の動作および性能特性を示す増幅器を設計することが望まれる。

【解決手段】改良された直線性および低減されたパワー消費を備えた高周波数応答性を与える可変利得増幅器が提供される。改良された直線性および安定した動作のために複数の信号経路および補償回路網を備えた、1段トポロジから構築される増幅器が開示される。この増幅器において、改良された性能は、単一のトランジスタコンポーネントを、局所的な負帰還を組み込むエンハンスされた活性デバイスと置き換えることにより、取得される。本発明の1実施形態は、従来技術に対して、トランスコンダクタンスおよび入力インピーダンスを向上させるエンハンスメント回路である。さらなる発展は、改良された直線性を提供するエンハンスされた活性なカスコード回路である。

(もっと読む)

電流電圧変換回路

【課題】回路構成を簡素化した電流電圧変換回路を提供することである。

【解決手段】NPNトランジスタQ1のエミッタとPNPトランジスタQ2のエミッタとが入力端子INに接続される。NPNトランジスタQ1のコレクタが定電源V1ラインに接続され、PNPトランジスタQ2のコレクタが電源C2ラインにされる。NPNトランジスタQ1のベースと、PNPトランジスタQ2のベースとの間に、バイアス回路20が接続され、フローティング状態とされる。

(もっと読む)

位相可変増幅器

【課題】回路規模が小型で低消費電流、出力信号の線形性に優れ、周波数特性が平坦であって、その上低ノイズの位相可変増幅器を提供する。

【解決手段】入力信号の位相を調整する移相部1、位相が調整された後の信号のゲインを増幅するゲイン可変増幅部2によって位相可変増幅器を構成する。そして、移相部1は、全域通過フィルタで構成される可変容量の容量素子103、容量素子103がエミッタとベースとの間に接続され、調整された入力信号の位相に対応する位相電流を生成するトランジスタ101を含み、可変ゲイン増幅部2は、移相電流がテール電流として供給されるトランジスタ108、トランジスタ109を含む差動対、トランジスタ109に流れる電流を電圧に変換する抵抗素子107、トランジスタ108、トランジスタ109に流れる電流を制御する制御信号を出力する制御回路106を含む。

(もっと読む)

増幅回路

【課題】線形動作範囲の劣化を抑制することができる増幅回路を提供する。

【解決手段】増幅回路は、一対の相補信号がそれぞれ入力する入力端子であるエミッタEと、制御端子であるベースBと、出力端子であるコレクタCと、を具備する一対のトランジスタQ5及びQ6を有するコモンベース回路30と、一対のトランジスタQ5及びQ6が出力する一対の相補信号を差動増幅する差動増幅回路32と、差動増幅回路32が出力する一対の相補信号から、差動増幅回路32が出力する一対の相補信号間のオフセットを調整するためのオフセット信号を生成し、オフセット信号を一対のトランジスタQ5及びQ6の制御端子Bにそれぞれ出力するオフセット信号生成回路40と、を備える。

(もっと読む)

スイッチドキャパシタ利得段

【課題】出力電流を増やすことなくセトリング時間を短縮することが可能なスイッチドキャパシタ利得段、及び、これを用いたパイプライン型A/D変換器を提供する。

【解決手段】スイッチドキャパシタ利得段は、第1フェーズではサンプル/ホールド回路(キャパシタCf及びCs、並びに、スイッチSWa〜SWc)を用いて入力電圧Vinのサンプリングを行い、第2フェーズでは増幅器(AMP1及びAMP2)を用いてサンプリング済み入力電圧の増幅出力を行うスイッチドキャパシタ利得段において、入力電圧Vinのサンプリング動作時にのみ、前記増幅器のミラー補償を行うミラー補償部(Cm、SWg)を有する構成とする。

(もっと読む)

電子回路

【課題】相補信号による差動出力のバイアス電圧のオフセットの入力信号に対する変化を抑制すること。

【解決手段】ベースに入力信号Vinが入力される第1トランジスタQ1と、ベースに前記入力信号を平滑化した平滑信号Vavgが入力され、エミッタが前記第1トランジスタのエミッタと共通接続された第2トランジスタQ2と、前記第1トランジスタおよび前記第2トランジスタのコレクタに接続され、相補出力をなす第1出力端子OUT1および第2出力端子OUT2と、前記第1トランジスタおよび前記第2トランジスタのそれぞれのコレクタと前記第2トランジスタのベースとの電位差をそれぞれ一定に保つ電位差生成回路20と、を具備する電子回路。

(もっと読む)

シグナリングシステム、前置増幅器、メモリデバイスおよび方法。

電力合成回路

【課題】 2つのパルス信号を増幅して合成するときの出力波形の乱れを低減することが可能な電力合成回路を提供する。

【解決手段】 入力端子11〜13と、第1の入力端子に接続される第1の増幅器15と、第2の入力端子12に接続される第2の増幅器16と、ソース端子およびドレイン端子の一方ならびにゲート端子が第1の増幅器15に接続される第1のトランジスタ17と、ソース端子およびドレイン端子の一方ならびにゲート端子が第2の増幅器16に接続される第2のトランジスタ18と、第1および第2のトランジスタ17,18におけるソース端子およびドレイン端子の他方がソース端子およびドレイン端子の一方に接続されるとともに、第3の入力端子13がゲート端子に接続される第3のトランジスタ19と、第3のトランジスタ19におけるソース端子およびドレイン端子の他方が接続される出力端子14とを備える電力合成回路とする。

(もっと読む)

ゲート接地型増幅回路

【課題】高速低消費電力の電流検出型センスアンプの実現には、低バイアス電流でゲイン帯域積が大きな増幅器をゲート接地型トランジスタに設ける必要がある。

【解決手段】ソースが電流入力端子Iin1,Iin2、ドレインが負荷8,9および電圧出力端子Vout1,Vout2に接続されたゲート接地型トランジスタペアM1,M2のゲート・ソース間に、トランジスタM3とM5およびM4とM6の2組のソースが共通のプシュプル型CMOS反転増幅器で構成される差動増幅器の共通ソースに定電流トランジスタM7が設けられた差動増幅器AMPを設ける。

(もっと読む)

1 - 20 / 115

[ Back to top ]