Fターム[5K029KK23]の内容

直流方式デジタル伝送 (8,390) | 監視;試験 (418) | 測定値、検出値 (264) | 時間;位相 (92) | ジッタ (57)

Fターム[5K029KK23]に分類される特許

1 - 20 / 57

ワンダ測定装置及びワンダ測定方法

【課題】簡単な回路構成で高精度なワンダ測定が行える。

【解決手段】正弦波生成部4a,4bは、クロック信号からなる被測定信号と基準信号とを動作クロックとしてそれぞれ正弦波電圧信号u1(t),u2(t)を出力する。位相復調部6は、2つの正弦波電圧信号u1(t),u2(t)を一定周期でサンプリングして得られる系列u1(n),u2(n)間の瞬時位相の差に基づく時間差系列x(n)を出力する。制御部8は、予め設定される被測定信号の公称周波数と基準信号の公称周波数とに基づき、規定の出力周波数f0に最も近づく周波数チューニング・ワードFTW1,FTW2を1組の正弦波生成部4a,4bに設定して2つの正弦波電圧信号u1(t),u2(t)の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧する。

(もっと読む)

可変シンボル間干渉発生装置及びデータ生成方法

【課題】データ信号に与えるシンボル間干渉量を連続的に且つ正確に調整できるようにする。

【解決手段】データ信号を周波数応答可変のプログラマブル・フィルタ1010と、PCB配線、一定長のケーブル、ディスクリート・フィルタなどの固定周波数応答を有する固定フィルタ1015を通すことによって、データ信号に与えるシンボル間干渉の量を連続的に調整する。プログラマブル・フィルタ1010は、そのパラメータを調整することで、その挿入利得又は挿入損失を調整でき、これによって、シンボル間干渉量を連続的に可変できると共に正確に調整できる。

(もっと読む)

ジッタ付加装置及びジッタ付加方法

【課題】ジッタ付加対象である対象信号に付加するジッタのパラメータを簡便に設定できる。

【解決手段】ジッタ付加対象となる対象信号に対して任意に設定したジッタを付加するジッタ付加装置1において、位相変調量と変調周波数の2つのパラメータで座標軸が構成される2次元グラフデータからなり、機器毎に設定されたジッタ設定可能範囲が示されるパラメータグラフ情報を表示する表示部15と、パラメータグラフ情報が表示される同一画面上に表示されたポインタPで当該パラメータグラフ情報のジッタ設定可能範囲内の任意の位置を選択する際に操作される操作部11と、ポインタの座標位置に応じて前記対象信号に付加するジッタの各パラメータを設定する制御部13とを備えた。

(もっと読む)

信号発生装置及び方法

【課題】ランダム・ジッタのクレスト・ファクタ・エミュレーションを有する波形試験信号を発生する。

【解決手段】CPU60は、表示器56にユーザ・インタフェースを発生して、シリアル・データ・パターン用のパラメータと、シリアル・データ・パターンに与えるデターミニスティック・ジッタ欠陥、ランダム・ジッタ欠陥及び少なくとも1つの偏差クレスト・ファクタ・エミュレーション欠陥用のパラメータとを設定する。これらパラメータを用いて波形記録ファイルを発生し、偏差クレスト・ファクタ・エミュレーション欠陥が欠陥シリアル・データ・パターン内に選択的に位置決めされる。波形発生回路70は、 これらに基づいて、欠陥のあるシリアル・データ・パターン・アナログ出力信号を発生する。欠陥のあるシリアル・データ・パターン・アナログ出力信号に変位クレスト・ファクタ・エミュレーション欠陥を選択的に位置決めする。

(もっと読む)

伝送装置及び伝送信号のジッター抑圧方法

【課題】伝送装置の出力信号のジッターを抑制することを目的とする。

【解決手段】伝送装置は入力信号が入力しているか否かを検出する入力信号断検出部と、発振器と、前記入力信号断検出部により入力信号が入力していることが検出されたときには、前記発振器の発振周波数と、入力信号から抽出されるクロック信号を分周した分周信号の周波数との差の周波数がフィルタの通過帯域外となるように前記発振器の発振周波数を設定する周波数設定部とを備える。

(もっと読む)

アダプタ装置および伝送路評価システム

【課題】パッド付の伝送路の伝送特性についての評価装置による評価を可能にする、評価装置に接続されるアダプタ装置およびこれを備える伝送路評価システムを実現する。

【解決手段】試験信号が入力された評価対象伝送路2から出力される出力信号に基づき評価対象伝送路2の伝送特性を評価する評価装置3に接続されるアダプタ装置1は、評価対象伝送路2の入力端へ入力される試験信号と同じ信号が入力される入力端を有する基準伝送路11と、評価対象伝送路2の出力端から出力される出力信号から、基準伝送路11の入力端に生じた試験信号の反射成分と評価対象伝送路の入力端に生じた試験信号の反射成分との差を増幅した反射成分増幅信号と、基準伝送路11における試験信号の通過損失分と評価対象伝送路2における試験信号の通過損失分との差を増幅した通過損失分増幅信号と、を減算して生成される信号を評価装置3への評価信号とする生成手段12と、を備える。

(もっと読む)

半導体LSIおよび半導体装置

【課題】データレート可変な半導体装置及び信号伝送系においても、配線長共振起因のノイズやジッタを小さくする技術を提供する。

【解決手段】プリント回路基板3上に搭載されたメモリ1とメモリコントローラ2との間で信号配線4−1〜3を通じて信号伝送を行う信号伝送システムにおいて、メモリ1とメモリコントローラ2に、特定のデータレートで配線長共振によるノイズやジッタ増加が起こる場合において、このデータレートの情報を保持するレジスタ6−1、6−2を有する。すなわち、配線長共振が起こるデータレートを保存するレジスタ6−1、6−2とクロック周波数と配線長の関係を変更するような制御系を信号伝送システムに持たせ、共振回避できるようにデータレートまたは伝播遅延時間をコントロールする。

(もっと読む)

ジッタ測定装置

【課題】単体で復調信号の波形表示が正確に行えるようにする。

【解決手段】単一の筐体内に、外部から入力されたデジタル信号のジッタ成分を復調するジッタ復調器21と、そのジッタ復調器21から出力される復調信号Jの振幅値の算出を行うジッタ量算出器22と、ジッタ復調器21から出力される復調信号Jに対する周期測定を行い、その測定された周期に応じた倍率の補間処理を行う補間器23と、表示器25と、ジッタ量算出器22の算出値および補間器23によって補間された復調信号の波形を表示器に表示させる表示制御部24とが設けられている。

(もっと読む)

ジッタ測定装置、ジッタ算出器、ジッタ測定方法、プログラム、記録媒体、通信システム、および試験装置

【課題】短い測定期間で精度よくジッタを測定する。

【解決手段】予め定められたパターンが繰り返される被測定信号のタイミングジッタを測定するジッタ測定装置であって、予め定められた測定期間内で被測定信号をコヒーレントサンプリングするサンプリング部と、サンプリング部がサンプリングしたデータ値の順序を入れ換えて、被測定信号の波形を再現する再構成波形を生成する波形再構成部と、再構成波形を複素数の解析信号に変換する解析信号生成部と、解析信号に基づいて、被測定信号のジッタを測定するジッタ測定部とを備えるジッタ測定装置を提供する。

(もっと読む)

非対称な遅延に関して通信システムを診断する方法及び装置

本発明は、非対称な遅延に関して通信システムを診断するための方法及び装置に関し、非対称な遅延は、少なくとも1つの閾値と比較される。 (もっと読む)

クロック抽出回路

【課題】エラーが発生する前にエラー発生の予兆を知る。

【解決手段】データ入力信号Dinからデータ入力信号Dinに係るクロック信号CK1を再生するクロック再生回路11と、再生されたクロック信号CK1に同期すると共に再生されたクロック信号CK1に対して一定の位相差を有する1または2以上のサンプリングクロック信号CK2、CK3を生成するサンプリングクロック生成回路12と、1または2以上のサンプリングクロック信号CK2、CK3および再生されたクロック信号CK1によってそれぞれデータ入力信号Dinをサンプルホールドするサンプルホールド回路13と、サンプルホールド回路13のそれぞれのサンプリング結果の論理値の全てが同一ではない場合にエラー予兆信号Epを出力するエラー判定回路14と、を備える。

(もっと読む)

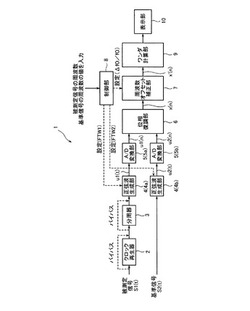

ジッタ伝達特性測定装置

【課題】ジッタ伝達特性を迅速に測定できるようにする。

【解決手段】変調用信号発生部22が、それぞれの振幅m1〜mnが既知で周波数f1〜fnが異なる複数の正弦波成分が含まれる変調用信号Mを生成してジッタ発生部21に出力する。この変調用信号Mによって位相変調されたクロック信号Cがデータ信号発生部23に入力され、クロック信号Cに同期したデータ信号Dが被測定物1に与えられ、被測定物1から出力されるデータ信号D′がクロック再生部25に入力されてそのクロック信号成分C′が再生され、位相検波器26によりクロック信号成分C′に対する位相検波処理がなされる。信号振幅検出部27は、位相検波器26の出力信号M′から変調用信号Mに含まれる複数の正弦波成分の振幅を検出し、その検出した振幅と、各正弦波成分の既知の振幅との比を演算処理部40においてそれぞれ求める。

(もっと読む)

算出装置、算出方法、プログラム、記憶媒体、試験システム、および、電子デバイス

【課題】サンプルタイミングの範囲およびビットエラーレートを精度良く算出する。

【解決手段】対象信号の特性を算出する算出装置であって、ビットエラーレートまたはサンプルタイミングの何れか一方の指定を受ける指定部と、対象信号のジッタに含まれるランダム成分の標準偏差および対象信号のジッタに含まれる確定成分のピークツゥピーク値をパラメータとして代入することにより得られる、ランダム成分および所定の確率密度分布の確定成分を含むジッタを有する信号を伝送する伝送モデルにおける、サンプルタイミングとビットエラーレートとの関係式を用いて、指定されたビットエラーレート以下となるサンプルタイミングの範囲、又は、指定されたサンプルタイミングにおけるビットエラーレートを計算する計算部とを備える算出装置を提供する。

(もっと読む)

タイムインターバルアナライザ及びその測定方法

【課題】従来のタイムインターバルアナライザは、測定結果を得るために測定サンプル数よりも多くの除算を行うために、測定時間が多くかかる問題があった。

【解決手段】本発明にかかるタイムインターバルアナライザは、被測定信号が特性値に対して正の遅延と負の遅延とのいずれの遅延量を有しているかを判定する位相比較器11と、正の遅延を有する被測定信号の個数と負の遅延を有する被測定信号の個数との除算結果を測定結果として出力する演算回路13と、を有するものである。

(もっと読む)

ディジタルインターフェースを有する半導体装置

【課題】本発明の課題は、インターフェースのレシーバにて、データパターンに依存するジッタを低減することにある。そして、低減するための遅延量の設定を装置毎に調整できるように自動的に調整可能なLSIを提供することにある。

【解決手段】データパターン依存ジッタは、前の状態がどの様であったかで予測可能であるので、レシーバにて受け取ったデータの状態を保持しこの保持された状態と、入力されたデータとから入力データの取り込みタイミングを調整する。

また、実装形態に依存する遅延量を決定するためのレシーバ内の調整機構として、ドライバから1サイクル間隔のパルスデータ、2サイクル間隔のパルスデータをテストパターンとして送受信する。パルス幅の異なるパルスの立上りと立下がり時間差から系に最適な遅延量を求める自動調整機構を持つ。

(もっと読む)

ジッタ測定装置、ジッタ測定方法、記録媒体、通信システム、および試験装置

【課題】短いサンプリング時間で精度よくジッタを求めることができる、ジッタ測定装置、ジッタ測定方法等を提供する。

【解決手段】周期Tの被測定信号をサンプリングするサンプリング部と、前記サンプリング部がサンプリングしたサンプル値の順序を再配列して、周期Tの再構成波形を形成する波形再構成部と、前記再構成波形におけるエッジ部のタイミング分布を生成する分布生成部と、前記タイミング分布の統計値を計算する統計値計算部とを備えたジッタ測定装置を提供する。前記サンプリング部は、周期Tの被測定信号がM周期繰り返される期間中に、前記Mと互いに素な関係の数Nの回数だけ前記被測定信号をサンプリングしてもよい。

(もっと読む)

ジッタ測定装置

【課題】高速なデータ信号のジッタ特性を容易に且つ正確に測定できるようにする。

【解決手段】被測定物1から繰り返し出力される所定パターンのNRZ形式のデータ信号Drを信号変換手段25によりRZ形式のデータ信号Dr′に変換し、そのRZ形式のデータ信号Dr′を、分周器28においてNRZ形式のデータ信号Drの符号周期内におけるデータの遷移回数と互いに素な値で分周することで、元のデータ信号より低いビットレートでありながら、元のデータ信号の符号周期内の全てのデータ遷移タイミングの情報が含まれるデータ信号Dr″を得て、そのジッタの測定をジッタ測定部30で行う。

(もっと読む)

ジッタ伝達特性測定装置

【課題】フィルタの温度特性無依存を維持しつつ、簡単な回路構成でジッタ伝達特性を求めることができるジッタ伝達特性測定装置を提供する。

【解決手段】ジッタが付加されたクロック信号を被測定装置に出力するジッタ発生ブロック230と受信した出力信号のジッタを復調して解析する復調解析ブロック700とを備える。ジッタ発生ブロック230は、変調信号を発生する変調信号発生器210と、第1クロック信号発生器200と、ジッタ発生部220とを備え、復調解析ブロック700は、第2クロック信号発生器400と、ジッタ復調部410と、A/D変換器500と、変調信号の周波数成分のみを抽出するためのディジタル・フィルタ610と、抽出されたジッタ信号に対して変調信号の周波数成分を有する時間軸の評価関数をあてはめてジッタ信号の振幅を得る最尤推定部620と、得られた振幅からジッタ伝達特性を計算する伝達特性演算手段630とを備える。

(もっと読む)

SFP制限増幅信号のジッタ耐性を改善するための方法および装置

【課題】SFP制限増幅信号のジッタ耐性を改善するための方法および装置を提供すること。

【解決手段】ジッタ耐性は、受信信号をSFP制限増幅器に印加することによって、およびSFP制限増幅器の出力を、ジッタ耐性を改善するローパスフィルタに印加することによって、通信受信機において改善される。ローパスフィルタは、任意選択的に、出力の高周波数成分に、プログラム可能な量の減衰を加える。低パスフィルタのスルーレートは、受信信号のデータアイ表示部を制御して(すなわち、回転させて)、データアイ表示部を時間軸に沿って増大させる。受信信号の雑音余裕は、任意選択的に、ローパスフィルタの出力を全パスフィルタに印加することによって改善可能である。スルーレート・コントローラが、データアイ統計値を求めて、ローパスフィルタについての設定を決定することが可能である。

(もっと読む)

チャネルスキューの識別および通知

本発明の実施形態は、複数の並列チャネルを分析し、容認可能なスキュー許容誤差外のスキューを有する特定のチャネルを識別する。ある実施形態では、本スキューは、被試験チャネルとデスキューチャネルとの間のタイミング不整合を決定することによって、識別される。複数のチャネル内の他のチャネルは、マスクされた反復ビットパターンを伝送することによって、マスクされる。本タイミング不整合は、被試験チャネル内のセグメントをデスキューチャネル内の対応するセグメントと比較し、2つのセグメント間の時間差を識別することによって、測定され得る。  (もっと読む)

(もっと読む)

1 - 20 / 57

[ Back to top ]