Fターム[5K047AA05]の内容

デジタル伝送方式における同期 (12,489) | 目的、効果 (2,701) | 同期品質の向上 (1,344) | タイミング品質の向上 (665)

Fターム[5K047AA05]の下位に属するFターム

位相ジッタ吸収 (104)

ケーブル長依存の伝送遅延変化の補償 (27)

スキュー補正 (110)

無信号時にもクロック供給 (10)

Fターム[5K047AA05]に分類される特許

401 - 414 / 414

復元回路、及び復元回路の復元方法

【課題】一つのチャージポンプのみを利用して制御されるアナログ位相補間技術を適用し復元回路及び復元方法を提供する。

【解決手段】高速直列データ送受信器の受信側でクロックとデータとを復元する時、位相補間技術を利用すると、必要なPLLの数が一つに減少され、電力消耗、雑音、面積側面で多くの利点を得ることができる。本発明は、従来に使用された制限された位相解像力を有するデジタル位相補間器の短所を克服するために、アナログ位相補間器を採用した。そして、二つのチャージポンプを使用した従来のアナログ位相補間器を適用したクロックデータ復元回路と比較して、一つのチャージポンプを使用して位相補間器を制御して、正確な特性制御を通じて改善されたジッタ特性を得ることができる。

(もっと読む)

クロック切り替え回路

【課題】 ハザードを生じることなく早いタイミングでのクロック切り替えが可能なクロック切り替え回路を提供すること。

【解決手段】 第1のクロックCLK1と、第2のクロックCLK2と、クロックCLK1とクロックCLK2を切り替えるためのクロック切り替え実行信号CESとを受け、クロックCLK2が第1のレベルである期間に信号CESがアクティブになった場合に、クロックCLK1の立ち上がりエッジまたは立ち下がりエッジを含む前後の所与の期間、クロックCLK2のレベルを第2のレベルに固定してクロック切り替え用合成クロックCMPとして出力する合成クロック生成回路300と、クロックCMPと、信号CESとを受け、クロックの切り替え指示信号CDSを出力する切り替え指示信号生成回路200と、信号CDSがアクティブになった場合に、第1のクロック選択信号CSS1のレベルを変化させるクロック選択信号生成回路100と、信号CSS1のレベルに応じて、クロックCLK1またはクロックCMPのいずれかを選択して出力する第1のセレクタ400を含む。

(もっと読む)

OFDM復調装置

【課題】 周波数誤差を低減しつつ、移動体中においてもタイミング抽出が精度良く行える技術を提供する。

【解決手段】 IQ生成部109で発生するOFDMベースバンド信号(IQ信号)を複素相関演算部103が入力され、複素相関演算部103で計算された自己相関と相互相関とを移動平均演算部104に入力して各移動平均を計算し、相関強度演算部110において相関強度を計算する。さらに、ガードインバーバル期間は、有効シンボル期間長の1/4、1/8、1/16、1/32とGI比とが定義されている。これらの各MODEとGI比との関係を用いることにより、相関強度の形状やピーク値から、まず、有効シンボル期間長(MODE)の判定を行い、次に、GI期間長(GI比)の判定を行い、最後にこの判定MODEと判定GI比とに基づいてピーク位置検出を順次行う。

(もっと読む)

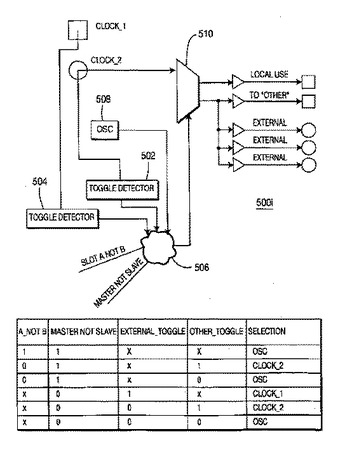

非同期信号をルーティングするためのシステムおよび方法

少なくとも1つの入力信号および少なくとも1つの出力をルーティングするルータ(100)は、少なくとも1つの入力モジュール(4021〜402x)および少なくとも1つの出力モジュール(4041〜404y)からなる。入力モジュールおよび出力モジュールの各々は、部分的には、第1および第2のクロック信号が切り替わったかどうか、に基づいて、第1および第2のクロック信号、および発振器信号の中から、共通の出力クロック信号として選択するための少なくとも1つのクロック・セレクタ回路(5001〜500n)を備えている。クロック・セレクタ回路は、リダンダンシーを提供し、各モジュール内部の各要素にクロック信号を配信する。  (もっと読む)

(もっと読む)

時刻読み出し方法、リアルタイムクロック及び電子装置

【課題】 本発明は、時刻読み出し方法、リアルタイムクロック及び電子装置に関し、リアルタイムクロックのカウント動作を停止させることなく、正しい時刻をリアルタイムクロックから読み出すことを目的とする。

【解決手段】 クロック信号をカウントして得た時情報、分情報及び秒情報を第1のレジスタ部に保持し、第1のレジスタ部に保持されている時情報、分情報及び秒情報を、時刻読み出し要求に応答して第1のレジスタ部とは異なる第2のレジスタ部に同時にコピーし、時刻読み出し要求に応答して、第2のレジスタ部に保持されている時情報、分情報及び秒情報を順次読み出すように構成する。

(もっと読む)

ディジタル信号処理装置及びディジタル信号処理方法

【課題】 動的にデータ量が変化する場合でも、ジッタの影響で生ずる音声・画像等の情報の劣化を低減し、かつ伝送レート制御を可能とするディジタル信号処理装置を提供する。

【解決手段】 入出力回路26は、メモリ18に蓄積されている符号化映像音声信号をDCLK12に同期して取り出し、符号化映像音声信号16として復号化器15に伝送する。伝送レート制御器27では、ディスク再生装置1で用いられているクロックPCLK4とは非同期の、クロックDCLK12に同期して生成した時間情報STCとPCR28との比較を行う。伝送レート制御器27は、その比較結果に基づいてディスク再生装置1の伝送レートを制御するための伝送レート制御命令を生成し、データ入出力回路26に命令データとして供給する。

(もっと読む)

キャリア位相不定性の補正

受信器は、復調された信号を供給する復調器と、復調された信号に応じ、セントロイドを算出し、かつ、復調器におけるキャリア位相不定性を除去するうえで用いる正しいキャリア位相を識別するセントロイド算出器とを備える。更に、セントロイド算出器は、リミタを含み得る。

(もっと読む)

(もっと読む)

シンボルタイミングの曖昧さ訂正

受信機は、シンボル期間あたり複数の信号サンプルをもつ復調信号を与える復調器と、前記復調信号に応答して前記複数の信号サンプルのうちチャネル仮想中心を決定するのに使う少なくとも一つを選択する、セントロイド計算器とを有する。さらに、セントロイド計算器は復調器にシンボルタイミング情報を提供してもよく、制限器を含んでいてもよい。  (もっと読む)

(もっと読む)

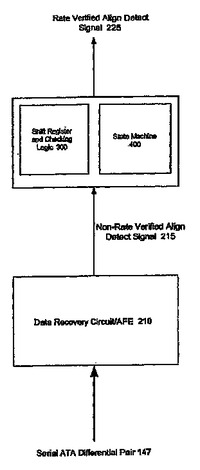

受信したシリアル転送アライメントシーケンスのレートの検証

受信したシリアル転送アライメントシーケンスのレートを検証する技術は、シリアル転送ストリームの受信を含む。そして、受信したシリアル転送ストリーム内でアラインシーケンスが認識されたかどうか判定する。アラインシーケンスが認識されると、予め定められた数のクロック周期の間にアラインプリミティブが適切な回数受信されたかどうかを判定するための検査が行われる。アラインプリミティブの受信回数と、予め定められた数字とが一致すると、レート検証済アライン検知信号がアサートされる。

(もっと読む)

(もっと読む)

クロックデータ再生回路

受信データ信号の揺らぎや変動に対する追従速度とクロック品質を改善し、さらに最適な識別位相に自動調整可能としたクロックデータ再生回路の提供。

VCO203からのクロックと受信データ信号を入力して位相差を検出する位相比較器209と、積分回路210と、VCO203よりなる第1のフィードバックループ204と、受信データ信号201を入力する識別器205と、識別器205の出力と受信データ信号201を入力して位相差を検出する位相比較器211と、積分回路212と、VCO203から出力されるクロックを入力し積分回路212の積分出力に応じて位相をシフトして出力する位相シフタ208よりなる第2のフィードバックループ207を有する。

(もっと読む)

クロックリカバリ回路及び通信デバイス

本発明に係るクロックリカバリ回路は、第1遅延量でデータ信号を順次遅延させる複数段の第1可変遅延素子と、第1遅延量より大きい第2遅延量で、クロック信号を順次遅延させる複数段の第2可変遅延素子と、複数段の第1可変遅延素子によって遅延された複数のデータ信号を、同一段の第2可変遅延素子によって遅延されたクロック信号によりサンプリングする複数のタイミングコンパレータと、連続する2つのタイミングコンパレータの2つのサンプリング結果を排他的論理和演算する複数のEOR回路と、複数のEOR回路の演算結果に基づいて、クロック信号を遅延させるリカバリ可変遅延回路とを有する。 (もっと読む)

可変周波数データのためのクロックデータリカバリ(「CDR」)回路、装置および方法

CDR回路などの回路には、本発明の実施形態におけるクロック信号に応じて、可変データビットレートを有するデータ信号を受信するサンプラが含まれる。クロック回路が、サンプラに連結され、選択可能な更新レートおよび選択可能な位相調整ステップサイズに応じてクロック信号を生成する。本発明の第2の実施形態において、クロック回路には、第1、第2および第3のステージに連結され、かつ第1および第2のステージ出力信号に応じて位相調整信号をホールドできるストールロジックが含まれる。本発明の第3の実施形態において、表示器が可変データビットレートを検出し、カウンタが調整信号のための選択可能な位相調整ステップサイズを提供する。本発明の第4の実施形態において、クロック回路には、ストールロジック、表示器およびカウンタが含まれる。本発明の第5の実施形態において、クロック回路には、所定期間の第1および第2の調整信号の平均値算出に応じて位相調整信号を出力する平均回路が含まれる。

(もっと読む)

(もっと読む)

ユニバーサル移動体通信システム受信機におけるセル・サーチの間の周波数の同期

ユニバーサル移動体通信システム(UMTS:Universal Mobile Telephone System)は、受信した一次同期サブチャンネル(PSCH)を使用してスロットの同期を実行する(305)。スロット同期の完了に続き、UMTS受信機は受信した二次同期サブチャンネル(SSCH)を使用してフレームの同期を実行し(320)、UMTS受信機は受信した一次同期サブチャンネル(PSCH)を使用して周波数のオフセットを調節する(325、330、335)。  (もっと読む)

(もっと読む)

データ処理回路

【課題】伝送データ流れの回復バージョンを発生するデータクロック回復回路を提供する。

【解決手段】データ流れを受け取り、これからもとの伝送データ流れのビット周期毎に信号レベルの評価推定値を発生する。データ回復ブロック4に信号レベルの評価推定値を記憶し、クロック回復ブロック6によってサンプリングし、もとのデータ流れを回復する。また、データ回復ブロック4については、評価推定された信号レベルの精度を表す品質係数,ワードメトリックを発生させる。クロック回復ブロック6は、受信データ流れおよびデータ回復ブロック4で発生したワードメトリックの両者を使用し、現在のサンプリング時間が正しいかどうかを決定する。正しくない場合には、現在のサンプリング時間を調節し、理想的なサンプリング時間に向けて移動させる。相関器8は、新しいデータ流れの起点をいつ受信したかを決定する。

(もっと読む)

401 - 414 / 414

[ Back to top ]